ELECTRICAL ENGINEERING DEPARTMENT STANFORD UNIVERSITY, STANFORD, CA 94305

# NETLIST PROCESSING FOR CUSTOM VLSI VIA PATTERN MATCHING

NITE

**Thomas Stephen Chanak**

**Technical Report No. CSL-TR-95-681**

November 1995

This research was supported by the ARPA, under contract DABT 63-94-C-0054

#### NETLIST PROCESSING FOR CUSTOM VLSI VIA PATTERN MATCHING

#### **Thomas Stephen Chanak**

#### **Technical Report: CSL-TR-95-681**

#### November 1995

Computer Systems Laboratory Departments of Electrical Engineering and Computer Science Stanford University Stanford, CA 94305-4055 pubs@shasta.stanford.edu

#### Abstract:

A vast array of CAD tools are available to support the design of integrated circuits. Unfortunately, tool development lags advances in technology and design methodology - the newest, most aggressive custom chips confront design issues that were not anticipated by the currently available set of tools. When existing tools cannot fill a custom design's needs, a new tool must be developed, often in a hurry. This situation arises fairly often, and many of the tools created use, or imply, some method of netlist pattern recognition. If the pattern-oriented facet of these tools could be isolated and unified among a variety of tools, custom tool writers would have a useful building block to start with when confronted with the urgent need for a new tool.

Starting with the UNIX pattern-matching, text-processing tool *awk* as a model, a pattern-action netlist processing environment was built to test the concept of writing CAD tools by specifying patterns and actions. After implementing a wide variety of netlist processing applications, the refined pattern-action system proved to be a useful and fast way to implement new tools. Previous work in this area had reached the same conclusion, demonstrating the usefulness of pattern recognition for electrical rules checking, simulation, database conversion, and more. Our experiments identified a software building block, the "pattern object", that can construct the operators proposed in other works while maintaining flexibility in the face of changing requirements through the decoupling of global control from a pattern matching engine.

The implicit computation of subgraph isomorphism common to pattern matching systems was thought to be a potential runtime performance issue. Our experience contradicts this concern. VLSI netlists tend to be sparse enough that runtimes do not grow unreasonably when a sensible amount of care is taken. Difficulties with the verification of pattern based tools, not performance, present the greatest obstacle to pattern matching tools.

Pattern objects that modify netlists raise the prospect of order dependencies and subtle interactions among patterns, and this interaction is what causes the most difficult verification problems. To combat this problem, a technique that considers an application's entire set of pattern objects and a specific target netlist together can perform analyses that expose otherwise subtle errors. This technique, along with debugging tools built specifically for pattern objects and netlists, allows the construction of trustworthy applications.

#### Key Words and Phrases: CAD, Electrical Rules

© Copyright by Thomas Stephen Chanak 1995

All Rights Reserved

## Acknowledgements

A number of people made helpful contributions during my time at Stanford. My advisor, Professor Mark Horowitz, in addition to providing his guidance and insight, never failed to provide the resources and opportunities I needed to pursue this work. I am especially grateful to him for providing access to his contacts throughout the chip design community, including the people at Digital Equipment Corporation who provided large examples and large machines to run them on, and especially Ed Hudson, who deserves a great deal of credit for leading me toward a rewarding research topic.

I am also indebted to my associate advisor, Professor Teresa Meng, and to Professor Bruce Wooley for reading this thesis and to Professors Oyekunle Olukuton and Stephen Boyd for serving on my oral examination committee.

My peers in CIS and CSL collectively formed as large a portion of my overall experience as any other. John Maneatis has helped, listened, and exhorted so many times in so many circumstances that I cannot imagine how things might have been without him. "Birdie" Amrutur and Russell Kao bravely and graciously served as guinea pigs at times when my work was still taking shape. I would also like to name Don Ramsey, Drew Wingard, Arturo Salz, Clem Portmann, Stefanos Sidiropoulos, Marc Loinaz, Phil Lacroute, and Mike Smith; these are the people who maintained the culture in which I learned so much.

This research was supported by ARPA under contract number DABT63-94-C-0054.

My love to Sylvia, Emily, and Matthew; may we continue on a long adventure together.

# Table of Contents

| Acknowledgements iii                                                                                                                                                                        |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Table of Contents                                                                                                                                                                           |  |  |  |  |

| List of Tables                                                                                                                                                                              |  |  |  |  |

| List of Figures ix                                                                                                                                                                          |  |  |  |  |

| Chapter 1<br>Introduction                                                                                                                                                                   |  |  |  |  |

| 1.1. Motivation11.2. Commonality in Custom Tools31.3. A Concrete Example41.4. Using Patterns to Process Netlists5                                                                           |  |  |  |  |

| Chapter 2<br>The Role of Pattern-Based Processing7                                                                                                                                          |  |  |  |  |

| 2.1. Netlist Processing via Text Processing72.2. Hardwired Code102.3. Netlist-Specific Implementation Methods112.4. Netlist Parsing142.5. Choosing a Paradigm for a Pattern-Oriented Tool15 |  |  |  |  |

| Chapter 3 Pattern Objects                                                                                                                                                                   |  |  |  |  |

| 3.1. Pattern and Action Specification173.2. The Subgraph Pattern/Action Object213.3. The Use of Pattern Objects253.4. Netlist-Specific Pattern Extraction283.5. Summary30                   |  |  |  |  |

| Chapter 4<br>Matching Algorithms and Matching Performance                                                                                                                                   |  |  |  |  |

| 4.1. Subgraph Isomorphism344.2. Algorithms for Subgraph Isomorphisms374.3. Relative Performance474.4. Summary49                                                                             |  |  |  |  |

| Chapter 5                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Debugging and Verifying Pattern-Based Applications51                                                                                                                                                                                                               |

| 5.1. Measures To Counter Routine Bugs525.2. Detecting Unintended Pattern Interaction585.3. Summary67                                                                                                                                                               |

| Chapter 6<br>Conclusions                                                                                                                                                                                                                                           |

| Appendix A                                                                                                                                                                                                                                                         |

| A Pattern Object Implementation's Reference Manual                                                                                                                                                                                                                 |

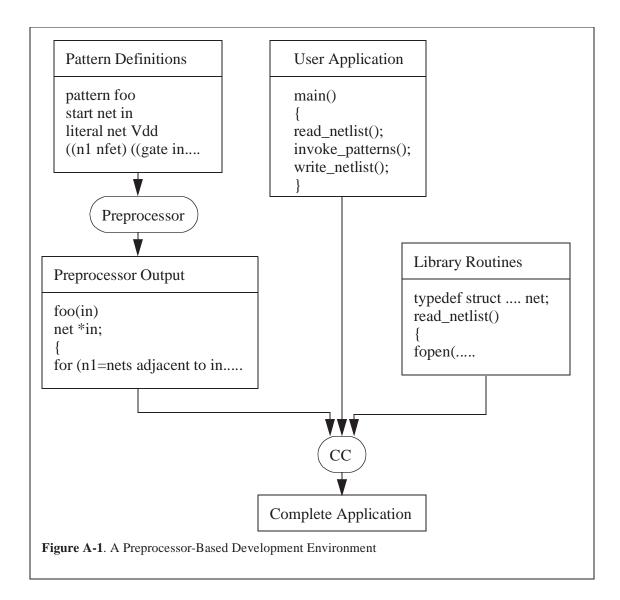

| A.1. Pattern-Based Applications.71A.2. Overall Design of the System72A.3. Netlist Infrastructure73A.3.1 Data Types and Representation74A.3.2 Library Routines76A.4. Writing Patterns79A.4.1 Pattern Specification79A.4.1 Pattern Generation81A.5. A Full Example82 |

| Appendix B<br>Practical Advice for Building a Pattern Object Environment                                                                                                                                                                                           |

| References                                                                                                                                                                                                                                                         |

# List of Tables

| Table 4-1 . Adjacent Edge Counts per Vertex, Sorted | 35 |

|-----------------------------------------------------|----|

| Table 4-2 . Fanout Statistics for Four Netlists     | 37 |

| Table 4-3 . Three-Input Nand Search Profile         | 44 |

| Table 5-1 . Search Statistics for a Buggy Pattern   | 55 |

# List of Figures

| Figure 1-1 . An "AWK for Circuits" Script to Replace Sense Amplifiers with Inverters              |

|---------------------------------------------------------------------------------------------------|

| Figure 2-1 . Transistor stack folding often does not lead to a stack of parallel tran-<br>sistors |

| Figure 3-1 . Alternation Illustrated with a Complementary Pass Gate 19                            |

| Figure 3-2 . Closure illustrated with an inverter                                                 |

| Figure 3-4 . Invoking a Pattern Object                                                            |

| Figure 3-3 . A Pattern to Find Static Latches and Remove the Weak Feedback . 23                   |

| Figure 3-5 . A Netlist Containing a Staticizing Inverter                                          |

| Figure 3-6 . Two Multiple-match cases                                                             |

| Figure 3-7 . A Pattern Implementing Alternation to Constrain Context 26                           |

| Figure 3-8 . Multiple Inverter Configurations via Recursion                                       |

| Figure 3-9 . Pattern to Traverse a Channel-Connected Subgraph (Forever!)28                        |

| Figure 3-10 . Patterns to Find the Width of the Widest Ripple-carry Adder in a Netlist            |

| Figure 3-11 . The Family of Latches Used in MIPS-X                                                |

| Figure 3-12 . Pattern Declarations to Recognize a Latch Family                                    |

| Figure 4-1 . Four graphs, two of which are alike                                                  |

| Figure 4-2 . Context obscures local isomorphism invariants                                        |

| Figure 4-3 . Histogram of Device Fanout                                                           |

| Figure 4-4 . Continued Histogram                                                                  |

| Figure 4-5 . General Brute-Force Algorithm                                                        |

| Figure 4-6 . Static search order for an Inverter                                                  |

| Figure 4-7 . Inverter-searching code                                  |

|-----------------------------------------------------------------------|

| Figure 4-8 . Better Inverter-searching code                           |

| Figure 4-9 . Choosing Search Order in Light of Context                |

| Figure 4-10 . Two search-orders for a 3-input nand gate               |

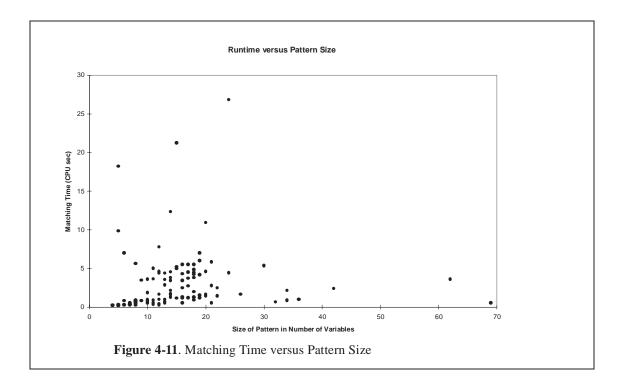

| Figure 4-11 . Matching Time versus Pattern Size                       |

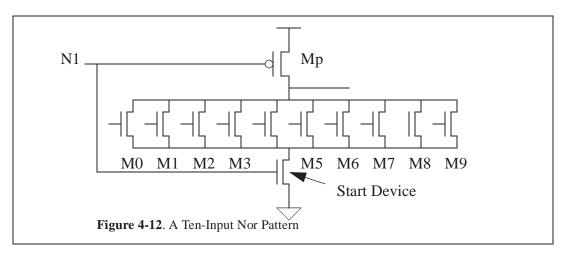

| Figure 4-12 . A Ten-Input Nor Pattern                                 |

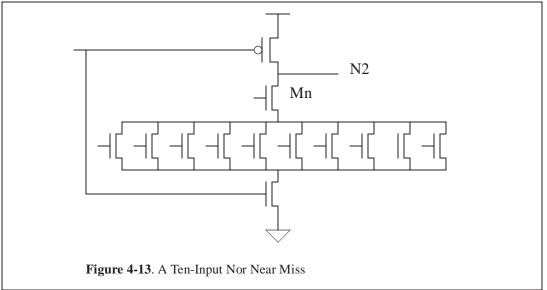

| Figure 4-13 . A Ten-Input Nor Near Miss                               |

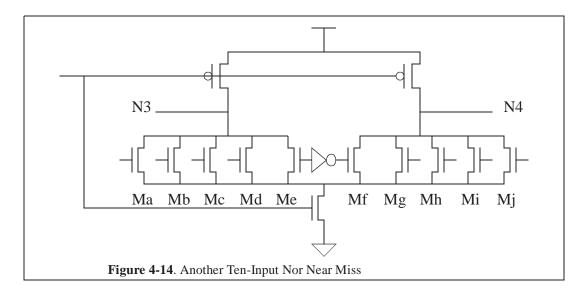

| Figure 4-14 . Another Ten-Input Nor Near Miss                         |

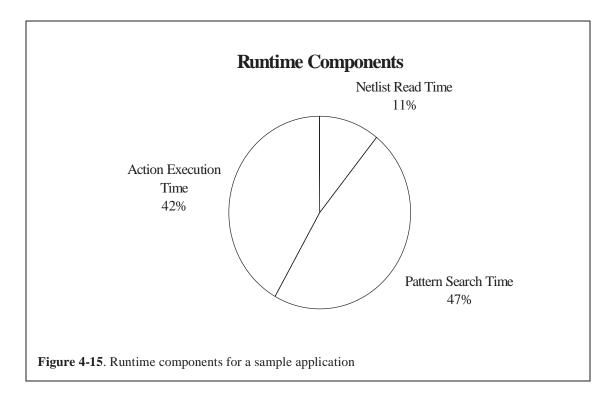

| Figure 4-15 . Runtime components for a sample application             |

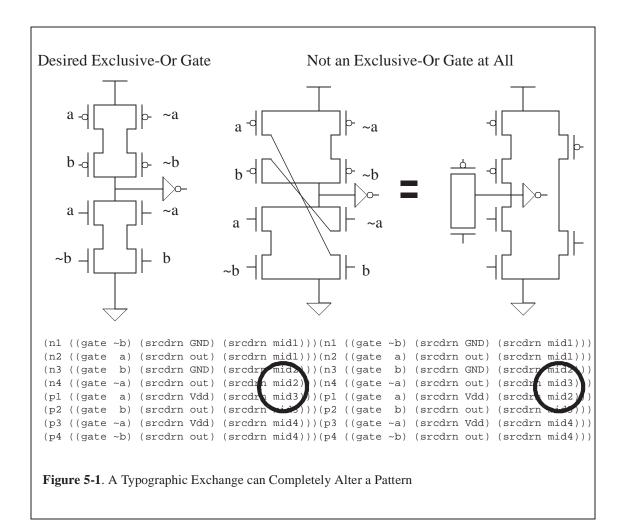

| Figure 5-1 . A Typographic Exchange can Completely Alter a Pattern 52 |

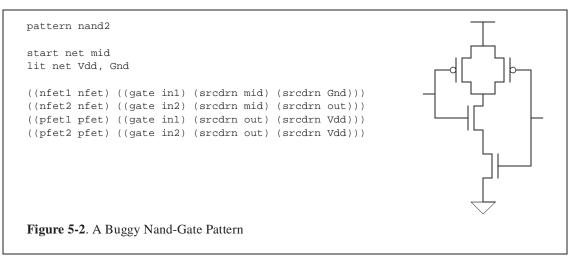

| Figure 5-2 . A Buggy Nand-Gate Pattern 55                             |

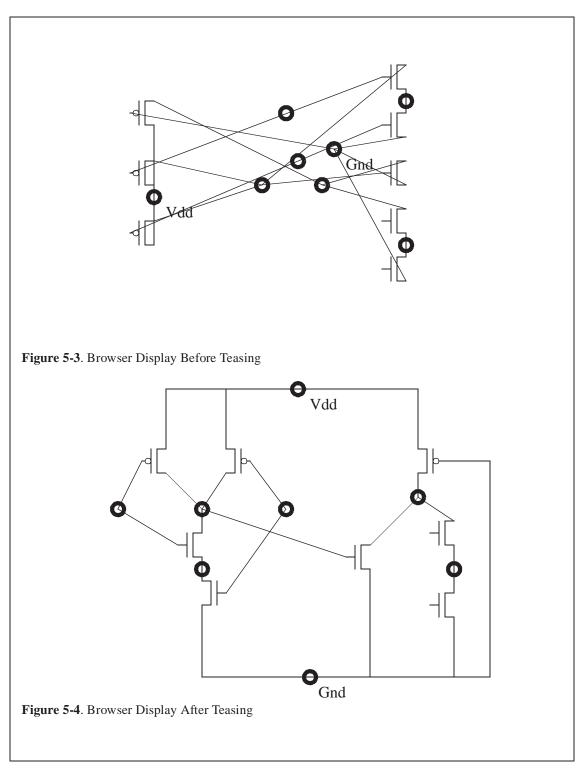

| Figure 5-3 . Browser Display Before Teasing                           |

| Figure 5-4 . Browser Display After Teasing                            |

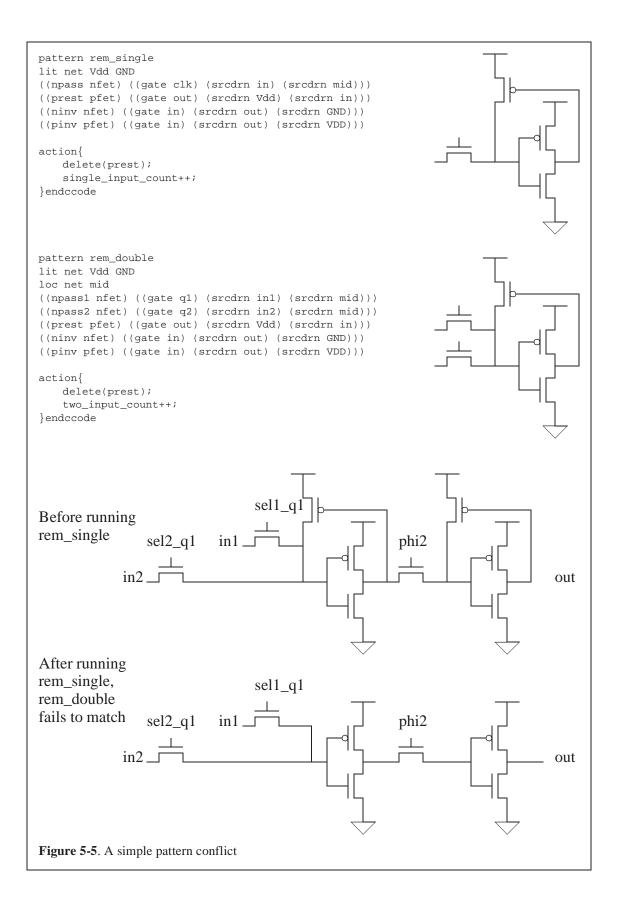

| Figure 5-5 . A simple pattern conflict                                |

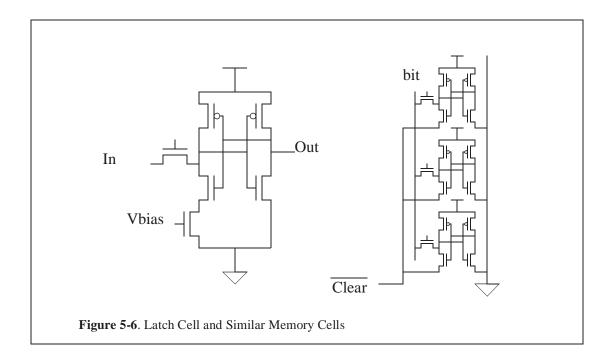

| Figure 5-6 . Latch Cell and Similar Memory Cells                      |

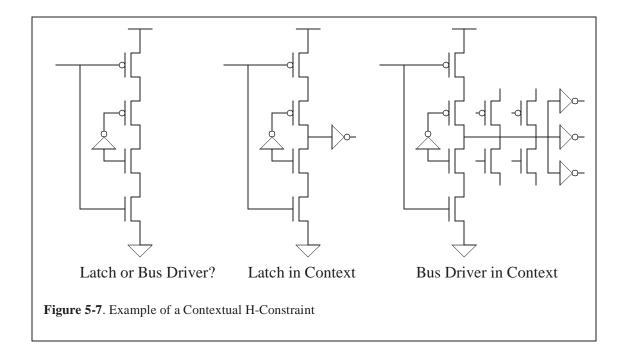

| Figure 5-7 . Example of a Contextual H-Constraint                     |

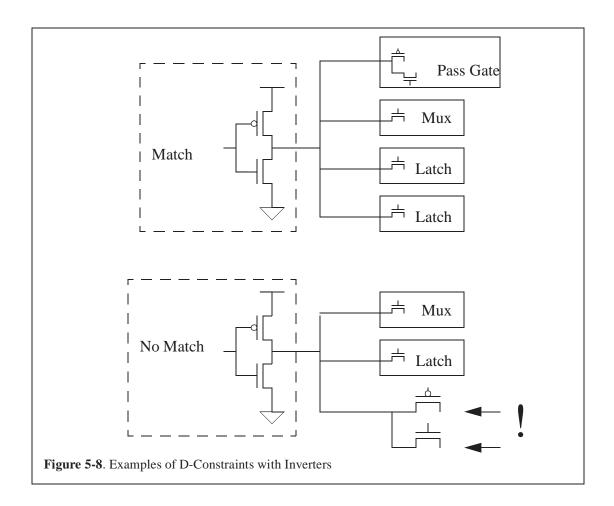

| Figure 5-8 . Examples of D-Constraints with Inverters                 |

| Figure A-1 . A Preprocessor-Based Development Environment             |

| Figure A-2 . A Sample Pattern Specification                           |

| Figure A-3 . Preprocessor Output for nand_check                       |

| Figure A-4 . The procedure toggleDataRead()                           |

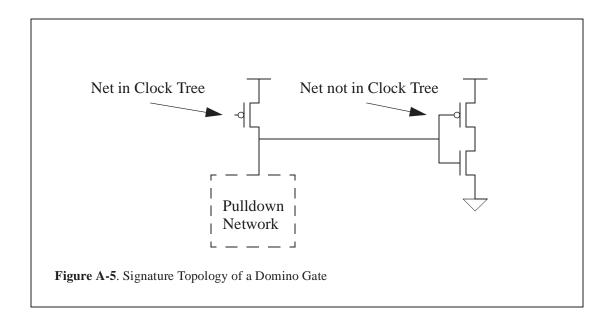

| Figure A-5 . Signature Topology of a Domino Gate                      |

| Figure A-6 . Domino Gate Pattern                                      |

| Figure A-7 . A Tree-following pattern              | 85 |

|----------------------------------------------------|----|

| Figure A-8 . The Main Application File, "tcount.c" | 86 |

| Figure A-9 . A Shell Session for "tcount"          | 86 |

# **Chapter 1**

### Introduction

#### **1.1. Motivation**

The expense and complexity of modern VLSI designs inevitably lead to the involvement of computer assistance in the design process. Device models and numerical methods yield circuit simulation tools like SPICE. Graph-comparison algorithms perform layout-versusschematic verification and geometric algorithms check technological design rules on lithography masks. Optimization techniques like simulated annealing can be applied to nearly any problem for which one can formulate a figure of merit. Tools like these contribute to most any chip design, from high volume memories to small research projects.

Fast product cycles have generated a lot of pressure toward reducing design cost, especially for low-volume designs or enormously complex ones. CAD tools for, among other things, automatic physical placement and routing, synthesis of gate implementations from logical specifications, and generation of test patterns can all reduce the cost of design in both time and designer effort. Most of these advances come about through a similar process: First, make assumptions and/or apply restrictions and/or stylize the form of the result to abstract the problem into a tractable form. Then, optimize the abstraction within the limits of computational feasibility. Especially in the realm of digital design, there are many opportunities to abstract and automate the integrated circuit design process.

The process of abstracting design problems, stylizing the solution space, and optimizing can be taken a long way. Silicon compilers attempt to generate optimal, correct-by-construction mask geometry starting with specifications as abstract as programming languages. If high-quality test vectors and a formal proof of correctness emerge as a by-product, all the better. The ultimate goal for an entire branch of integrated circuit CAD research is complete, turn-key design automation.

Complete design automation makes sense when the design cost matters above all else, either in terms of time or money, but design cost does not dominate all chip designs. There are still high-volume chips whose designs push the edge of technology in order to meet aggressive performance specifications. While large parts of these chips might be handcrafted by expert designers, those designers still need tools of various kinds in order to manage the complexity of large, modern chips. At the same time, significant portions of these designs will not push the technological envelope, and therefore make good targets for design automation.

Unfortunately, the same hand-crafting that advances the state of the art and allows unprecedented performance will invariably invalidate one or more of the pyramid of assumptions and abstractions that hold a monolithic design automation system like a silicon compiler together. Even when portions of a custom design could be automated in isolation, some advanced tools depend on seeing entire designs in order to validate any guarantees they make. In the end, custom chip designers have to give up on aggressive design automation, or at the least coerce their design and their tools to work together in some patchwork fashion.

So, must designers write their own design-automating tools to work within each new custom chip's unique parameters? It would seem ridiculous to reproduce the software engineering effort behind something as sophisticated as a silicon compiler prior to each new chip design, as the effort to produce a silicon compiler is perhaps greater than that needed to design a custom chip, worthwhile only when amortized over many designs. It turns out, however, that custom design teams do indeed produce a new tool set for each new design. The task is not quite as daunting as it seems for two reasons.

• A tool that worked perfectly well on a prior design may no longer function because a new design contains departures from that tool's underlying methodological assumptions. One can often salvage the use of such a tool. The new design's

assumption-breaking exceptional situations may be sparse enough or may appear in narrow enough contexts that they can be "doctored" in an *ad hoc* fashion, allowing the tool to proceed as before. As little as a shell script or a PERL program can perform the required fix up duty.

• More importantly, the CAD problems faced by custom designers are easier than the ones faced by writers of general-purpose CAD tools. They are easier because the designers can operate on both the tools and the design. CAD opportunities are the result of simplifications, abstractions, and constraints, and designers of custom chips have the ultimate ability to impose constraints and policies on their own designs. Tools in this role do not have to solve general cases, they only need to solve the specific instances of problems.

The writers of tools for custom designs might benefit if there were some middle ground between patching together semi-workable tools and building new ones from scratch. If there were some powerful building blocks to start with, which still left the abstraction/ assumption/policy decisions open, tool writers could both create new tools and glue together existing ones more easily. The key would be to choose building blocks which strike good balances between providing power and saddling the tool writer with implicit policy decisions. This thesis proposes one such tool based on topological pattern matching.

#### **1.2.** Commonality in Custom Tools

At one point or another almost all chip designs will be represented in terms of a network of discrete transistors and passive devices, a schematic diagram of sorts which, when in a computer-amenable format, is called a *netlist*. Many of the CAD tools designed or modified for use on custom designs operate primarily on device netlists.

A survey of netlist processing tools like simulators, rule checkers, and database converters shows that many of these tools contain a common component. Netlist processing tools frequently need to isolate exceptional subcircuits, classify subcircuits, or search for certain circuit configurations, all based on their local topologies, in order to direct their computations. A useful method for describing and manipulating subcircuits according to their topologies would be a good starting place for many new tools.

The building block proposed by this thesis is a method for specifying and implementing computations on netlists, especially device netlists. The specification technique can be described as a graph analog to the UNIX tool *awk*.[7] Just as *awk* searches for matches of regular expressions, and executes a code fragment wherever matches are found, this system processes netlists by specifying subcircuit topologies along with code to run whenever the corresponding subcircuits are found.

#### **1.3. A Concrete Example**

A sample application illustrates how a pattern capability might be used in practice. This example will assume that the pattern-oriented building block is provided in the form of an "AWK for Circuits" tool that reads a script of pattern-action pairs an applies them to a netlist.

Many designers will perform a whole-chip simulation in order to verify proper function and interconnection of the completed design at the topmost level. With larger designs, simulators will operate on digital abstractions of signals rather than with voltage and current waveforms in order to run fast enough. Unfortunately, nominally digital designs can contain analog components. An example of an analog circuit in a "wholly" digital chip would be a sense amplifier.

A fast, digital simulator like IRSIM [17] or COSMOS [18] cannot correctly model the functional behavior of some sense amplifiers, let alone their performance. Since top-level simulations typically address functional behavior only as a check on proper module interconnection, IRSIM could perform that functional check if sense amplifiers were replaced for the duration of the simulation with functionally equivalent substitute circuits. With performance parameters like timing set aside, an inverter makes a functional replacement for a sense amplifier, and IRSIM can model inverters. With all sense amplifiers temporarily replaced with inverters IRSIM can run the wholechip functional simulation, but the designer could make a mistake in performing the substitutions. The potential for errors of this kind cannot be dismissed because they are very similar in nature to the module misconnections that the whole-chip simulation guards against in the first place. The substitution has to be completely automated to be trusted.

An "AWK for Circuits" tool could easily implement automatic substitution. A script file like in Figure 1-1 with a pattern-action declaration directs the tool to look for the *pattern*, that is, subcircuits with topology the same as the description of a sense amplifier in the declaration, and for each matching subcircuit in the chip to run the declaration's corresponding *action*, a fragment of code whose function in this case is to remove the sense amplifier transistors from the netlist and insert inverter transistors in their place.

| begin pattern                                                                       |                                                              |  |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------|--|

| nfet2 bit nn bit_b a ne                                                             | pattern,<br>tlist describing<br>nse amplifier                |  |

| end pattern                                                                         |                                                              |  |

| begin action                                                                        | The action, which                                            |  |

| delete n1, n2, pload, etc.<br>insert ninv bit_b GND out<br>insert p                 | removes the sense<br>amplifier devices<br>and substitutes an |  |

| end action                                                                          | inverter                                                     |  |

| Figure 1-1. An "AWK for Circuits" Script to Replace Sense Amplifiers with Inverters |                                                              |  |

#### 1.4. Using Patterns to Process Netlists

Existing methods capable of quickly producing a variety of tools span a spectrum from *unix* shell tools like *awk* or *perl* to engines which can reconstruct netlist hierarchy bottomup. Chapter 2 examines each of these systems for strengths and weaknesses as platforms for building new, custom netlist processing tools. Of these methods, one closely resembling the hypothetical "AWK for Circuits" shows the greatest potential as a tool building platform given some redesign to improve its versatility. The phrase "AWK for Circuits" begins to describe a tool-building platform, but the exact mechanics of specifying topologies and the semantics of an *awk*-like pattern-action declarations carry a number of implications. Chapter 3 addresses the various options and issues on the way to developing a software abstraction called a *pattern object*. Pattern objects represent building blocks that unify the topological processing components of many custom tools and allow the easy development and maintenance of new netlist-processing applications.

Pattern-action declarations and their corresponding pattern objects will imply a matching computation between the pattern and part of a netlist. Previous efforts in this area have raised the concern that the matching process might be a difficult computational problem. An investigation of matching performance has largely erased this concern. While the matching problem is theoretically difficult in the general case, VLSI netlists have structural properties which can be exploited to make the matching process much easier. Chapter 4 outlines the circumstances that could lead to poor matching performance and present matching techniques that reliably run quickly.

Lack of performance or the unwillingness of tool writers to "write patterns" might be suggested as the primary drawbacks to pattern-based processing, but the forerunners of this work have not seen wider acceptance for a different reason: Chapter 5 discusses how, in the presence of netlist-modifying pattern objects, pattern-based applications can be especially challenging to verify. To gain confidence in such applications, methods have been developed which can examine sets of patterns and specific netlists in order to expose the combinations of patterns and netlists which can lead to the most difficult bugs.

## Chapter 2

### The Role of Pattern-Based Processing

When given a new problem to solve, developers have used a number of techniques to implement new netlist processing tools. This chapter focuses on those methods which provide the flexibility needed to adapt to changes in underlying technologies or methods. Of these, the simplest method merely applies text-processing tools to ASCII representations of netlists. Text-tool-based applications, though easy to construct and use, generally cannot address the connective structure in a netlist and therefore have a limited application domain. Faced with more demanding tasks, custom designers either move on to formal, declarative systems which are purposefully geared toward netlists or even resort to custom programming in order to implement solutions. An exploration of the strengths and weaknesses of each method will identify the most promising among them, a pattern-matching method which subsequent chapters will refine and elaborate.

Examples from two problem domains will illustrate the capabilities and weaknesses of each tool-building method throughout the discussion. In one application, an extracted-from-layout netlist will require modification prior to comparison with a reference schematic. A second application area will consist of "sanity checks", automatic analyses of netlists for gross design errors. Sanity checkers will process device netlists in order to detect and report the existence of particular errors.

#### 2.1. Netlist Processing via Text Processing

Some simple netlist CAD problems have an especially easy solution. When a device netlist is in "human-readable" form, some ASCII representation perhaps, a number of flexible tools designed for text processing can be applied to netlists. UNIX shell tools like

*grep*, *sed*, *awk*, *sort*, *uniq*, and so on can accomplish many useful computations when run on flat netlists.

The Berkeley "sim" format for CMOS device netlists provides a good example of a file format that text processing tools can manipulate usefully. In a "sim" file, each line of text represents one device: a transistor, a resistor, or a capacitor. The first letter in each line identifies the type of a device, capacitor versus resistor verses pfet versus nfet, and the following fields list the netlist names that the corresponding device terminals are connected to.

Turning to the sample applications, either *grep* or *awk* could help to prepare an extracted device netlist for comparison to a schematic netlist. During chip layout, contact-programmable cells, parasitic-matching replicas, and even vanity artwork (initials/logos) can create degenerate devices or nets which do not logically belong to the design and therefore should not participate in the LVS check. Many of these degenerate nets and devices can be identified through superficial examination of an ASCII netlist file. For example, devices that have their source and drain terminals shorted together will have identical net names in the corresponding fields in the netlist, so a simple *awk* program can filter these out. As an additional example, *grep* could easily screen out nfets with their gates grounded or pfets with their gates tied to Vdd.

In the sanity-checking domain, several checks can also be done the same way. Some design styles disallow pfets channels connected to Vss or nfet channels connected to Vdd. Either condition would be easy to detect with *awk*. Transistors with non-minimum length or transistors that short the power rails together could be caught by *grep*.

Direct application of text-based utilities solves the easiest problems, but the utility of textbased tools increases as additional information is encoded into net and device names. Selfimposed net naming policies can increase the amount of information available to tools that examine netlists a line at a time. Naming conventions that encode signal information like signalling levels or clock phases, if used universally, enable text-based systems to do additional useful things. The naming policy can be implemented manually by designers or by the tools they use. For instance, the LVS preparation and sanity checking applications could both make use of the name-inheritance system in the circuit extractor in *magic*.

Because the *magic* layout extractor generates net names in a consistent way, text-based tools can detect floating nets in a design. Nets without explicit user labels are assigned synthetic names which are easy to distinguish from user net names. If a designer explicitly labels every net in their design, then "floating" nets (like those in a logo which should be excluded from LVS, or ones that indicate wells which lack contacts) can be detected in two stages: First, wherever a transistor is connected to a net with a synthetic name, either the designer forgot to label that net or the net is not fully connected - perhaps a contact is missing. Once the design has been updated so that no transistors connect to synthetically named nets, any remaining synthetic names (connected to capacitors) will indicate floating nets.

The *magic* name inheritance system also adds information to user-labeled nets. The extraction is hierarchical, so if a net is labeled in a cell toward the bottom of the hierarchy the net's name includes that label and the "path" of cell instance names that leads from the top-of-the-hierarchy cell to the labeling cell. If the same net is labeled in multiple cells, the shortest, topmost-level label takes precedence. This naming behavior allows a useful sanity check when routing Vdd and GND throughout a design. If every cell labels Vdd and GND, and the chip has its power grid fully connected, the only net names containing the strings "Vdd" and "GND" should be Vdd and GND. The occurrence of a net named "Vdd" or "Vss" with a pathname points to a cell instance which was not connected properly. *Grep* can easily find these occurrences.

Preparation of an extracted netlist for LVS has another requirement that pushes the use of text-based tools to the limit. Because of the layout practice of transistor folding, a single transistor in a schematic can be implemented with several parallel transistors in a layout. Before an LVS run, parallel transistors in the extracted netlist should be combined into a single device. Even identifying parallel transistors is tough because each pair of parallel transistors will be described with two different lines of text in two different places in the

netlist file. The solution may not be straightforward, but the *unix* tools are up to the task in the hands of a creative user.

One possible solution to the parallel transistor problem begins with the observation that lexically sorting a ".sim" file almost accomplishes the task of grouping parallel transistors together. All that is needed is a canonical method for assigning source and drain terminals. With the shell tool *sort* as the primary component, detection of parallel transistors could be accomplished with the following steps:

- *Awk* can examine the source and drain fields of each transistor, swapping them if necessary to put them in ascending lexical order. At the same time, coordinate and size fields can be suppressed.

- *Sort* can now arrange the netlist file so that parallel transistors occupy consecutive lines. With coordinates and dimensions suppressed, and source and drain terminals assigned canonically, parallel transistors will actually be identical lines.

- Uniq can now remove, or *awk* can now remove and combine, the parallel transistors.

While the reduction of parallel transistors does not sound like a difficult problem, some significant creativity, brainstorming and debugging were required to produce the above solution. This limitation of these solutions arises primarily from the fact that the text-oriented tools do not "understand" the connectivity that the net names in a ".sim" file imply. Even the associative array capability of *awk* cannot straightforwardly represent and manipulate graphs. The *unix* shell tools are versatile and easy to work with, but their inability to address connectivity limits what they can accomplish when applied to netlists.

#### 2.2. Hardwired Code

Reducing parallel transistors pushes text-based tools to the limit, but the same problem poses little challenge to someone willing to write a small program in a programming language like C. Nothing exceeds the flexibility of custom programming, as all alternative implementation techniques are ultimately implemented with custom programs themselves. Weighing against the flexibility is the problem of starting with absolutely nothing. Other implementation techniques offer infrastructure or capabilities that can be leveraged to produce useful tools with less effort.

The LVS application that requires the reduction of parallel transistors demonstrates the extra work that involved with programming from scratch. The heart of the program, which searches for pairs of parallel transistors and combines them, consists of no more than two nested loops. Before writing these loops, though, a programmer will have to implement a data structure that can represent the netlist and its connections. The program will also need code to parse the input netlist and write out the modified netlist. By the time the program is finished the payload accounts for a small fraction of the overall amount of code.

To reduce the overhead of custom programming, developers will often attempt to reuse code from some previous application. When done in an undisciplined way, this approach sacrifices flexibility in a practical sense by creating brittle code. A better alternative might be a software system which provides infrastructure and functionality designed for modular use in the first place. Some such systems will be described in the next section.

#### 2.3. Netlist-Specific Implementation Methods

To implement tools without starting from scratch, researchers have proposed retargetable tools designed specifically for netlists. These tools seek to provide versatile netlist processing primitives that an end user can assemble into various applications.

Pelz [6] provides one example of a netlist tool-building tool. This system is designed as an interpreter which can execute script-like programs. The programs' statements can invoke various processing primitives on "variables" representing abstract data structures.

Sets rather than graphs constitute the principle data type of the variables manipulated by this particular interpreter. At the beginning of execution certain sets like "all devices" and "all nets" are implicitly defined, and the script can then generate new sets by applying the interpreter's built in primitive operations. These operations include classic set operations like union, intersection, and complement. The interpreter can also iterate over elements of a set, or reduce (count the elements of) sets.

The most important set-building primitives are the two that address the connectivity of the input netlist, CONNECT and HULL. CONNECT generates the set of nets/devices that are adjacent to a given device/net via any of a given set of terminal types. HULL is an iterating generalization of CONNECT which can generate transitive closures. Clever use of CONNECT and HULL can implement several useful graph traversing computations on a netlist. As the interpreter's author designed it specifically for ERC applications, there are many examples from the ERC domain which can demonstrate the utility of the interpreter and its primitives.

Error-checking applications built with the Pelz interpreter are usually designed to produce an "error" set as their output; if that set is empty the netlist passes the check. As an example, consider building the subset of "nets used as inputs to a gate that do not have a path through pfet channels to Vdd" in a CMOS design. A script with the following steps can perform the task:

- A HULL operator narrowed to pfet source and drain terminals is invoked on the net Vdd, generating the set "P2V", all nets connected by pfet channels to Vdd.

- The set "P2V" can be complemented, yielding "NP2V", the set of nets NOT connected by pfet channels to Vdd. None of these should be connected to transistor gate terminals.

- Iterating over all of the nets in "NP2V", the CONNECT operator can generate the set of devices adjacent to each net via gate terminals. Any devices that exist represent violations of the "outputs must have a p-channel path to Vdd" rule. Whenever this set is non-empty, the net used to generate it can be included in the error set.

The interpreter's set operators have enough versatility to implement the path-to-Vdd check and checks like "no asynchronous loops in a gate netlist" or "all scan chains have the same length", but the LVS parallel transistor example catches the system short. There is no way to construct the set of transistors that are in parallel with other transistors. In fact, the interpreter primitives are poorly suited to any task involving the recognition of subcircuits (like logic gates or latches) by topology alone.

An example of another tool-building system that fares better on recognition problems would be *DIALOG*. *DIALOG* [1][2] is a tool designed to implement expert systems that critique designs, in other words, electrical rules checkers. *DIALOG* contains an component called *LEXTOC*, a search engine which can find matches of a pattern topology in a netlist. This pattern matcher would have many applications in itself, but the *DIALOG* system goes a step further. Production rules in *DIALOG* knowledge bases are written as pairs of *LEXTOC* patterns and *DIALOG* primitive calls. This pattern-and-action inference engine could be thought of as "*AWK* for Circuits".

Parallel transistor reduction is an easy problem in *DIALOG*. One *LEXTOC* pattern specifying two parallel transistors and a corresponding action which reduces those transistors will cause the *DIALOG* engine to combine parallel transistors throughout the network. The expressive power of *DIALOG* increases the level of complexity of the problems that can be solved without resorting to C programming. Returning to the LVS application, a problem where transistor folding in the layout creates a need for parallel transistor reduction illustrates the capability of *DIALOG*. Figure 2-1 illustrates the folding of a transistor stack in layout. For the sake of layout density, the resulting circuit will often consist of parallel stacks rather than a stack of parallel transistors. Before LVS, a generalized case of the parallel transistor reduction problem needs to be run on any extracted netlist from layout that uses this trick. The incremental complexity of this new task versus parallel transistor reduction puts it way beyond the reach of text-based tools, and quadruples the complexity of the corresponding hard-wired C code. The DIALOG solution only needs a slightly bigger *LEXTOC* pattern and a slightly longer action. This ability to focus attention on certain topological configurations in a netlist by simply describing those topologies allows a user to easily implement a variety of useful tools.

According to its authors, *DIALOG* production rules can accomplish a full range of electrical rules checks like ratioing guidelines, fanout limits, and clocking compatibility constraints. The system ought to apply to other application domains, but inefficiencies from two sources slows down the *DIALOG* system for large netlists. First, the *LEXTOC* match engine runs slowly, with match times increasing superlinearly with problem size. An improved implementation, *LEXCAL* [1], increases the practical circuit size but does not change the asymptotic behavior, so again circuits above a certain size will be impractical. The *DIALOG* system also has inordinate memory requirements, largely in order to implement its parallel semantics - in *DIALOG*, all matching instances must be found and tracked before any actions are executed. These parallel semantics are required not by the application domain but merely by *LEXTOC*'s default, implicit global control flow.

#### 2.4. Netlist Parsing

It may be possible to go even further than *DIALOG/LEXTOC* in terms of describing and searching for topological configurations in a netlist. Rather than examining netlist topology piecemeal, perhaps the best approach is to parse a netlist in its entirety. If the hierarchical cell compositions that constitute a netlist can be reconstructed bottom-up from a flat design netlist, then tools might address the netlist in the form of a parse tree instead of a graph.

*GRASP* [15] is a tool designed to parse entire netlists. A user of *GRASP* writes a graph grammar which describes the set of legal circuits for a particular design methodology. *GRASP* can then determine whether some netlist conforms to the methodology by attempting to parse it with the grammar. *GRASP* itself attempts no more than recognition of "correct" netlists, but the ability to parse, to reconstruct hierarchy bottom-up in one automatic step would be a wonderful starting place for building new tools.

While promising in concept, *GRASP* lacks flexibility in a subtle way. *GRASP* grammars, like *yacc* grammars, are specified with mutually recursive production rules. *Yacc* requires grammars in the set LR(1) [20] in order to parse efficiently with a shift-reduce algorithm, and *GRASP* has an analogous restriction. While the *GRASP* authors were able to write a suitable grammar for recognizing a "CMOS 2-phase" methodology, rather an ambitious undertaking, not all reasonable methodologies will have a corresponding "fast" grammar. Furthermore, the question of whether some particular graph grammar can be parsed efficiently is not easy to answer by inspection. Therefore, users of a grammar-based tool development system might easily encounter an application where a suitable grammar is rendered unsuitable by the slightest of changes.

#### 2.5. Choosing a Paradigm for a Pattern-Oriented Tool

Text-based tools like *grep*, *awk*, and the rest of the *unix* suite provide a good model for a tool-constructing system by providing versatile primitive operations in well-partitioned modules. By themselves these tools can usefully manipulate netlists, but their design does not really address netlist connectivity. New modular tools, designed in the same spirit as the *unix* suite but specifically geared toward netlists, would allow rapid implementations of tools that would otherwise require the more burdensome task of writing custom programs.

The core of the *DIALOG/LEXTOC* system might be described loosely as an "AWK for Circuits". Of all of the systems described so far, this one appears to be a step in the right direction. The *DIALOG* system as it stands has some minor disadvantages as a retargetable tool-building platform: its action language is geared toward ERC applications, and its

implementation is slow. None of these are insurmountable problems. *DIALOG*'s biggest shortcoming as a building block is that its functionality is not packaged in the most useful way. If the basic concept underlying *DIALOG* were refined in order to place a patternaction paradigm in a versatile, modular, efficient package, the result would allow the rapid development of new netlist processing tools. Such a system will be developed in the next chapter.

# Chapter 3

### Pattern Objects

A system like "*Awk* for Circuits" or the *DIALOG* engine holds great promise as the foundation for new netlist processing tools. To maximize the potential for tool building, the basic pattern/action functionality of these tools should be made available in a useful form. The new capability should uniformly and concisely express useful computations. It should also provide this functionality in an open-ended way which does not make too many implicit assumptions about the nature of future tools. This chapter will identify a software entity that can accomplish all of these things, the *pattern object*.

One could choose a number of ways to design a tool which, loosely stated, "takes a list of patterns (subcircuits) with actions (code fragments) and executes the actions wherever it finds the corresponding patterns in some big netlist." The exact method of specifying the patterns and actions will establish the tool's flexibility, ease of use, and the expressiveness of its input language. The semantics of applying the patterns and actions to a netlist must also resolve potential ambiguous cases. This chapter will examine some possible specification techniques for pattern objects and choose one which makes an adaptable and flexible building block. That choice will turn out not to be an "Awk for Circuits" but rather a lower-level software object which can be used to implement *awk*-like tools, parsers, and other functions all with the same basic component.

#### **3.1. Pattern and Action Specification**

If the goal is to build a pattern-based tool development system, the first issue to address is also the most important one: how should topological patterns be specified? The answer to this question will influence every aspect of a pattern-based system and the applications built with it. *UNIX* tools like *awk, grep, sed, lex,* and *yacc* use patterns in their

specifications and also achieve great versatility, so perhaps their lexical pattern specification techniques can inspire a graph analog. *Awk, sed, grep*, and *lex* in particular use regular expressions to search for matches in a text stream. Regular expressions provide a nice way to specify useful pattern spaces, and the computation required for the implied searching and matching is straightforward.

"Regular expressions" for graphs, (GREs), might be invented by analogy to the usual lexical regular expression (LRE). The atomic GRE objects can be devices or nets, instead of the symbols from an alphabet for an LRE. In an LRE, juxtaposition in the expression implies sequence. In other words, symbols and their matches must appear in the same order. Graph adjacency would be the analogous concept for GREs. A textual description of the GRE would therefore look like a netlist.

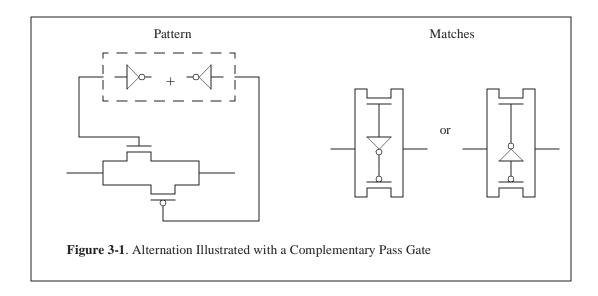

With the components described so far, LREs can specify literal strings, and GREs can specify subgraphs. A single regular expression will match exactly one string or subgraph. The utility of LREs comes in part from their ability to specify whole families, or "languages", of strings. This power of regular expressions lies in two additional operators, the alternation (+ or |) operator and the closure (\*) operator. Alternation, illustrated in Figure 3-1, seems sensible and logical when applied by analog to graphs. The topology can contain one subgraph or another, in this case an inverter connected in either of two directions.

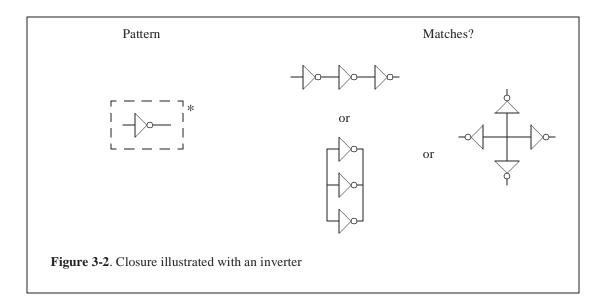

The closure operator will not be quite so easy to redefine in the graph domain. With strings, the symbols have an implied sequence, so that repetition can only mean one thing. Graph adjacency is a matrix, which leaves the meaning of "\*" ambiguous. Figure 3-2 shows the need for a "\*" operator to specify not just the base repeating unit but also the nature of the implied connections. Exactly how to specify this is not clear. In LREs the closure operator plays a role in any expression that specifies an infinite number of matching strings. Without a graph counterpart to "\*" graph patterns will describe a finite number of subgraphs, and could therefore be replaced with multiple subgraph patterns. No useful definition of "\*" suggests itself, so it may be necessary to look elsewhere for a specification method.

Regular expressions represent just one specification model that might extend to the graph domain. The *UNIX* tool *yacc* provides an example of another. Instead of regular expressions with their alternation and closure operators, *yacc* operates on grammars, sets of BNF production rules which hierarchically define the desired "language". *GRASP*, for instance, uses the graph analog of this idea to parse netlists according to a graph grammar.

A graph grammar can describe an infinite numbers of subgraphs, which could lead to concise, expressive declarations. A few production rules can define infinite families of topologies. Between simple subgraphs and graph grammars, grammars certainly have a greater

ability to describe topology. Pattern objects could potentially use either method for describing patterns. While grammars initially appear to be the better choice, there are more factors than topological expressiveness to consider.

A pattern-based system modeled after the paradigm of *yacc*, *awk* or *DIALOG* will have to specify actions as well as topological patterns. In pattern/action systems the pattern topology descriptions and corresponding action descriptions have an intimate relationship. Just as *awk*'s C-based action language has extensions to access a matched line of text and its components, a netlist action language will require some way for the action code to access the particular devices and nets that some corresponding pattern has matched.

For subgraph patterns the pattern description language will be a netlist. The usual method for specifying a netlist involves naming the nets and devices and then describing any connections by referencing those names. When the netlist has a match, the nets and devices from the matching subcircuit can be bound to variables with the same names as the nets and devices in the pattern netlist. Actions written in a programming language could then reference and manipulate the components of a matched subcircuit by naming the corresponding bound variables.

For graph-grammar patterns the pattern description language has just one netlist for each production rule, but the matching subcircuit will be one of a possibly infinite family of parse trees. Instead of the access to variables with one-to-one binding as in the subgraph case, actions for graph-grammar patterns would have to iterate or recurse over a parse tree to access the matching subcircuit's nets and devices.

Graph grammars might make for easier descriptions of a pattern's topology, but the corresponding actions will be much more difficult to write. This factor tips the balance toward simple subgraphs, and along with some practical shortcomings of graph grammars described earlier in Chapter 2 caused the adoption of simple subgraphs as the basis for the pattern object. The later development of netlist-specific pattern extraction (Section 3.4.) vindicated this choice.

#### **3.2. The Subgraph Pattern/Action Object**

With the pattern specification method settled, the next topic will be the pattern and action's semantics. So far, any discussion of how a pattern-and-action system works has tacitly assumed semantics similar to *awk*. In other words, just as *awk* scans an entire text file looking for pattern matches that invoke their respective matches, netlist pattern/action systems presumably scan an entire netlist for matching subcircuits, invoking the corresponding actions for each match found. This section describes another model where the outer control flow is made explicit. These semantics, simpler than those of *awk*, also turn out to be more flexible and capable, and at the same time less ambiguous.

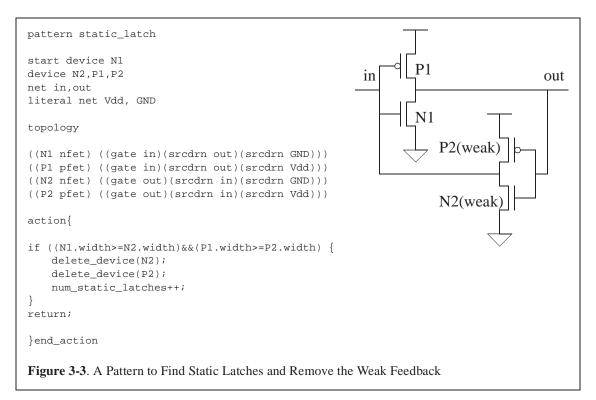

A pattern/action declaration is used to specify a pattern object. The declaration contains a pattern, a subgraph which looks like a small netlist. The declaration will also contain a fragment of programming language code, the action. To define the semantics of a pattern object, one net or device in the pattern netlist must be identified as a logical "start" or beginning of the pattern. An implementation of a pattern object then operates as follows: given a particular net or device from some netlist as a hypothesized match for the "start" net or device of the pattern declaration, search for a match of the remainder of the pattern in the netlist. In the event of a match, bind the matching nets and devices in the netlist to the corresponding names in the declaration, and then execute the declaration's action code. Figure 3-3 and Figure 3-4 together illustrate an entire processing step. Figure 3-3 shows a pattern object declaration, and Figure 3-4 shows a loop in an application's outer control flow which invokes that pattern's implementation. Before describing what this particular pattern object and loop do, the details of pattern declarations in general will be described first.

A pattern and action specification will have four parts. The first names the pattern, the second declares variables, the third describes topology, and the fourth describes the action.

• A pattern's name is used to invoke that pattern, just as the loop in Figure 3-4 invokes the pattern of Figure 3-3.

21

- The variable declaration section assigns names to the nets and devices of the pattern. The names are used in the topology section to describe the pattern's interconnection. Several keywords can precede a net or device name. The keyword "start" indicates the that pattern's logical start point. The keyword "local" applied to a net name asserts that any matching net from the netlist can have no adjacent devices other than the ones specified in the pattern. The keyword "literal" asserts that the matching net or device must be literally the one named. The pattern in Figure 3-3 uses "literal" to indicate that net variables "Vdd" and "GND" can only match the actual Vdd and GND nets in the netlist.

- The topology description is a netlist, written in terms of the names in the declaration section. The netlist is a list of devices, with each device naming its terminals and net connections.

- The action is a code fragment in a general-purpose programming language, C, which can access the matches to the pattern variables by naming those variables. Once the action completes, the search will continue unless the action contains an explicit "return" statement.

Figure 3-3 shows a specification for a pattern and action which identifies weak-feedback staticized latches and removes the feedback. The pattern specifies a four-transistor network that represents a loop of two inverters. The pattern and action make the assumption that of the two inverters in a symmetric configuration, the one made of weaker devices is the staticizing inverter.

In this pattern the device N1 is the declared start device, so the loop in Figure 3-4 simply proposes every device in the netlist as a potential match for N1. When a candidate for N1 leads to a match, the action code executes. Note that the action can access properties of matched devices by naming the corresponding variable, i.e. "N2.width" refers to the width

for (d = /\* all devices in the netlist \*/)

static\_latch(d, Vdd, GND);

Figure 3-4. Invoking a Pattern Object

of the device in the netlist that matched N2. This action compares the widths of the N1 and N2 matches in case the match is encountered in reverse before deleting the feedback devices.

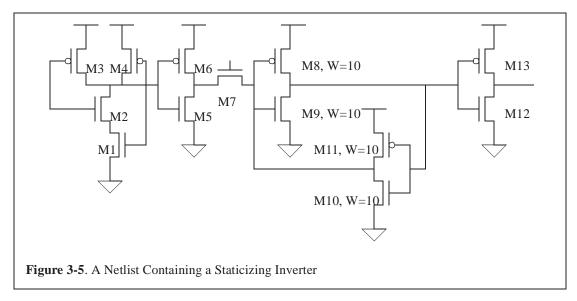

Why explicitly write loops like Figure 3-4? Such decoupling of pattern recognition from outer control flow will turn out to have numerous advantages. Among these advantages, separation of the pattern object from the control flow that invokes that pattern object resolves some ambiguities in the "*Awk* for Circuits" semantics. Multiple patterns each of which matches multiple subcircuits could all have their actions run concurrently, but netlist-modifying actions would lead to questions about what happens first or which action has priority in a conflict. An outer loop invoking the pattern object explicitly serializes and orders the matches and action executions. For example, if the pattern object specified in Figure 3-3 were invoked on every transistor in the netlist of Figure 3-5, the action could possibly execute beginning with either M9 or M10.<sup>1</sup> In either case the opposite inverter is

<sup>1.</sup> This is a bug - the conditions should be <, not <=. The way the pattern is, it would match SRAM cells!

deleted, so that the match can only occur once, so that the variable num\_static\_latches will not increment by two despite the fact that the netlist begins with two complete matches.

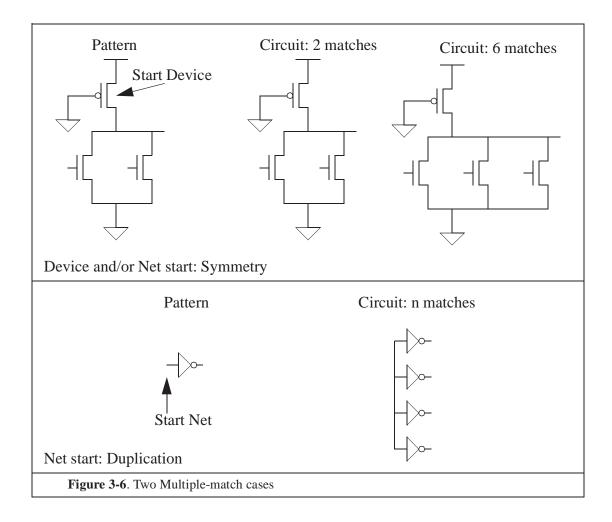

Another explicit control flow option resolves a further semantic ambiguity. A pattern object runs its action if a topological match is found given the start nets/devices. A "start" net might actually border multiple, independent matching subcircuits in a netlist. Even without multiple complete matches, due to symmetry, "start" nets and devices can both lead to multiple possible matches with the symmetric portion in different permutations. Figure 3-6 shows examples of both situations. In practice, two policies find a lot of use: find and run the action on all matches, or find and run the action on only the first match encountered. Since both policies are useful, either can be selected per pattern.

Explicit control flow resolves these potentially ambiguous cases, which is certainly something which needs attention, but there are more reasons to decouple the control flow from the pattern matches. The ability to make explicit choices, such as how to handle multiple matches, increases the flexibility of the pattern capability. The next section demonstrate some of the other possibilities that exist when the user explicitly manages control flow.

## **3.3.** The Use of Pattern Objects

Figure 3-4 illustrates how an application can use a pattern object to implement the "AWK for Circuits" notion of applying an action to every instance of a subcircuit in a netlist. A loop or an iterating function simply invokes the pattern once for each net or device in the entire subject netlist. This exhaustive "pass" is just one of many constructs that can be built with pattern objects.

So far pattern objects have been invoked from an application's outer control loops, but the application and the pattern action's code fragment can use the same programming language. Patterns can invoke patterns just as applications do in their outer loops. The ability of a pattern to call another pattern or even itself opens the door to a variety of useful computations. Consider the transmission gate of Figure 3-1, where the companion inverter could be present in either polarity. To count the transmission gates in a circuit, but only the ones accompanied by a companion inverter, one might write two patterns as in Figure 3-7. The calls in the pass-gate pattern's action implement alternation, as a means of constraining the allowable contexts for pass gates in this application.

```

pattern is_inverter returns "int" default "0"

start net in

start net out

start lit net v Vdd

start lit net g GND

((nfet1 nfet) ((gate in) (srcdrn out) (srcdrn g)))

((pfet1 pfet) ((gate in) (srcdrn out) (srcdrn v)))

pattern action{

return 1;

}endccode

pattern count_passgate

start dev pfet1

start lit net v Vdd

start lit net g GND

((nfet1 nfet) ((gate in1) (srcdrn a) (srcdrn b)))

((pfet1 pfet) ((gate in2) (srcdrn a) (srcdrn b)))

pattern action{

if (is_inverter(in1, in2, Vdd, GND))|is_inverter(in2, in1, Vdd, GND))

pass_gate_count++;

return;

}endccode

Figure 3-7. A Pattern Implementing Alternation to Constrain Context

```

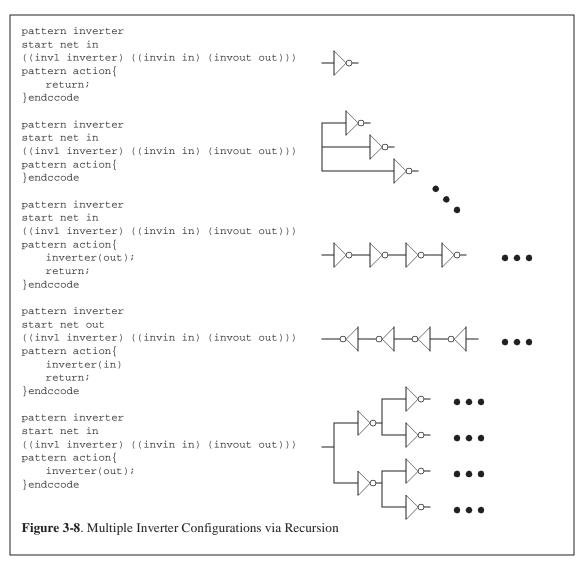

In Figure 3-8 pattern object recursion is used to traverse several configurations of inverters, depending on the presence of a recursive call, the presence of a "return", and specified interconnections. Pattern recursion in various forms can implement depth-first traversal, induction, or even elementary recursive-descent parsing. Implicit in these recursive patterns are the specifications of connection that the regular-expression "\*" operator failed to capture. Recursive pattern objects along with their invoking control flow can therefore manipulate infinite families of topologies without infinite specifications.

For an example of depth-first traversal, Figure 3-9 shows a single pattern containing a single device which can search for "channel-connected" subcircuits, a useful analysis unit for

MOS circuits. To be channel-connected a subcircuit must have a current path between any two nets which passes through transistor channels. (Paths through Vdd and GND do not count.) The pattern object specified in Figure 3-9 will find all nets belonging to the channel-connected subcircuit which includes the start net "init". The pattern traverses a channel-connected component by examining each transistor source or drain connected to a net, including the opposite net in the channel-connected subcircuit, and then continuing the search from those nets. For an induction example, Figure 3-10 outlines patterns for finding the width of the widest ripple-carry adder in a netlist.

```

pattern channel_connect

start net init

start lit net g GND

start lit net v Vdd

(fet1 ((srcdrn init) (srcdrn other)))

pattern action{

if (net_in_answer(other)) return;

include_net_in_answer(other);

channel_connect(other, g, v);

}endccode

Figure 3-9. Pattern to Traverse a Channel-Connected Subgraph (Forever!)

```

### 3.4. Netlist-Specific Pattern Extraction

With recursive control flows, pattern objects can begin to address infinite families of topologies. The problem with flexibly processing netlists in this way is that trying to add a useful payload to the recursive actions quickly comes to resemble the problem of writing actions for graph-grammar patterns. In both cases, actions that accomplish more than recognition are difficult to write. One solution to this problem is to decouple the recognition and processing. For a specific target netlist, payload-carrying pattern actions can be

```

pattern start_adder

start net inl

(( << topology of a half-adder>> ))

pattern action{

width = 1;

continue_adder(cout, Vdd, GND);

return;

}endccode

pattern continue_adder

start net cin

(( <<topology of a full adder>> ))

pattern action{

width++;

if (width>max_width) max_width = width;

continue_adder(cout, Vdd, GND);

return;

}endccode

```

Figure 3-10. Patterns to Find the Width of the Widest Ripple-carry Adder in a Netlist

produced from recognition-only patterns semi-automatically. The process contains the following steps:

- Write a graph grammar or a set of recursive pattern objects that recognizes an infinite number of topologies.

- Run the recognizing pattern on the target netlist. The output will be a series of netlists, one for each match found.

- Use a graph-comparing algorithm like *Gemini* to reduce the list of netlists found to a list of the distinct netlist topologies found.

- Transform the list of distinct netlists into a list of pattern declarations, each ready for a payload action to be inserted manually.

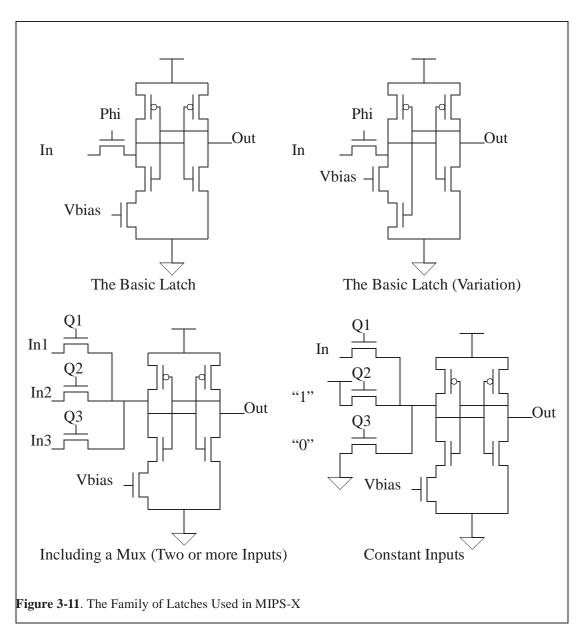

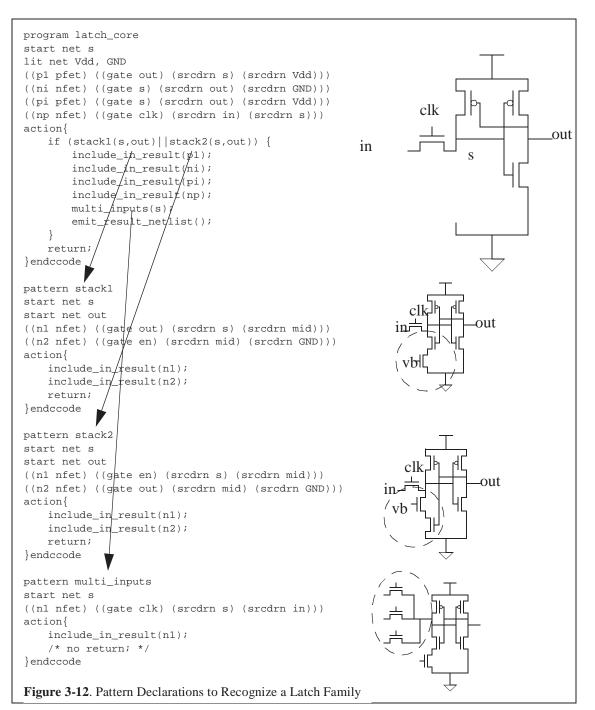

The process can be illustrated with the basic latch cell used throughout the RISC microprocessor MIPS-X. Figure 3-11 shows two variations of the basic cell, and also how a multiplexor is often merged with the basic cell. Not only might there be multiple pass transistors to implement the mux, but there is also a possibility that one or more of the mux inputs will be a constant, Vdd or GND. Each of these variations counts as a different topology, because the base cell already contains Vdd and GND. The topologies are distinct, and so perhaps are the appropriate payload actions for a given application.

The pattern set in Figure 3-12 can recognize all of the latches in the family illustrated in Figure 3-11. Four patterns work together: the first matches the core of the latch, the next two identify one of the two transistor stack permutations, and the last matches possible multiple inputs. These patterns recognized 1083 latches in the MIPS-X design. Of these, there were 18 different topologies - one, two, and three input latches, with the multiple input types occurring with various combinations of inputs tied together or to Vdd or to GND. The number of distinct latch topologies is certainly small enough that writing actions for each one by hand is not too much to ask of a tool developer.

With pattern extraction, grammar-like pattern expressiveness can be combined with straightforward action writing. To achieve this combination, attention must focus on a

single netlist, and unfortunately the process is only semi-automatic. These drawbacks do not prevent the pattern extraction procedure from being useful. In addition to the latchfamily application just described, this procedure has helped with the reverse engineering of unfamiliar netlists and has helped to track down errors through many different netlists and applications.

### 3.5. Summary

The basic *DIALOG* engine comes close to providing a reasonable platform for tool development, but the pattern object offers the same capability in a more versatile package.

*DIALOG* actions consist of a small set of primitives oriented specifically toward ERC applications, while the C language actions of pattern objects extend their application domain to other classes of CAD tasks. The additional flexibility gained by decoupling pattern invocation control flow from the pattern match engine also allows both a greater degree of user management and the possibility of using that control flow to help specify topology.

On top of a restricted set of action primitives and the limitations of its backward-chaining global control flow, *DIALOG* suffered from the poor performance of *LEXTOC*. Performance can be a critical parameter, as designers working on multi-million transistor designs have little use for an implementation technique that produces slow applications. While this shortcoming may account for the fact that *DIALOG* has not seen widespread use, the next chapter will demonstrate that pattern object implementations exist which can run fast enough to discount performance as a limitation of pattern-based tool development.

## **Chapter 4**

## Matching Algorithms and Matching Performance

The previous chapter established a formalism for specifying netlist operations with patterns and actions. Underlying any implementation that can execute pattern/action netlist operations is the ability to search for matches of a topological pattern in some larger netlist.

To find matches of some pattern in a graph is to solve the theoretical problem of subgraph isomorphism, a problem which is known to be computationally expensive in the general case.[11] This potential for long runtimes has lead Pelz [6] to explore the range of tools can be built with operations less powerful than pattern matching, lead the DIALOG [1] authors to implement compiled pattern matchers, and lead Ohlrich [11] to produce sophisticated subgraph isomorphism algorithms for *Subgemini*.

Fortunately, VLSI netlists have properties, sparsity especially, that render the matching problem easier than in the worst case. As a consequence, typical *Subgemini* runtimes grow linearly with the size of the subject netlist, rather than exponentially.[11]

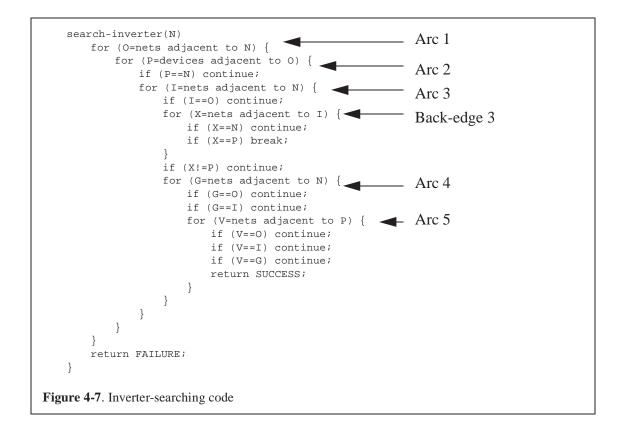

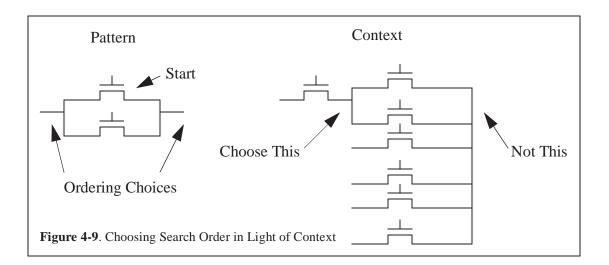

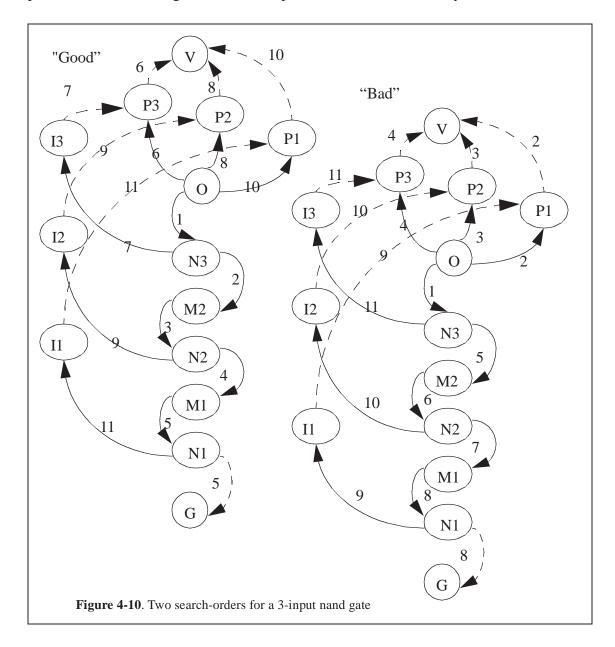

Despite the sparse nature of device netlists, initial experiences with a preliminary pattern matcher saw matching runtimes varying by factors of over a thousand for the very same netlist and pattern, depending on subtleties in the direction in which the search proceeded. With such a span of performance at stake it appeared necessary to write or "tune" patterns with performance continually in mind. The need to be mindful of search difficulty while writing patterns threatened to counteract the benefits of using patterns. Fortunately, less naive matching algorithms consistently perform well on typical netlists and patterns with-out requiring user direction or imposing unreasonable restrictions.

This chapter will begin by illustrating the difficulty of graph comparison in general, and then show how the problem simplifies for typical VLSI device netlists. Finally, the use of heuristics or the subgemini algorithm will be discussed as a means of releasing pattern writers from the responsibility of performance tuning.

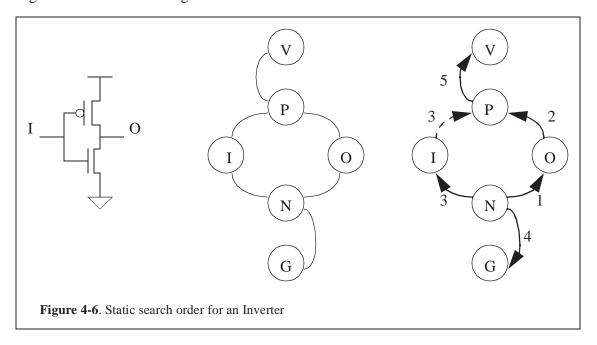

#### 4.1. Subgraph Isomorphism

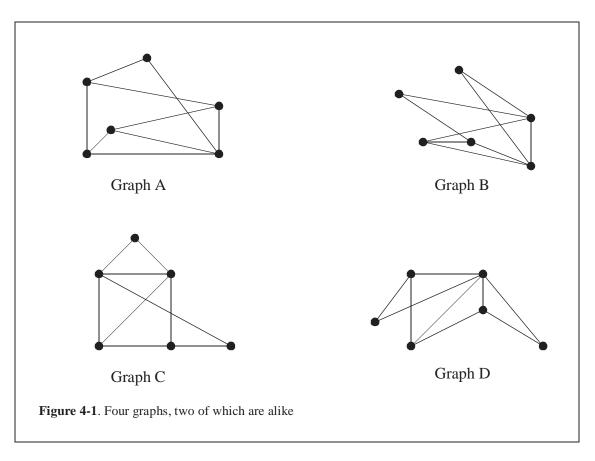

What is so difficult about finding matches of some smaller graph in a larger graph? A first step toward appreciating the theoretical difficulty of subgraph isomorphism would be to look at the simpler problem of graph isomorphism. Computing graph isomorphism amounts to comparing two graphs to determine whether they are instances of the same graph or not. Figure 4-1 shows four small graphs, only two of which are the same (isomorphic). On as small of an example as this, superficial inspection fails to make an easy determination of isomorphism. As graphs grow, comparison will usually involve systematic trial and error, as even the simpler problem of graph isomorphism is computationally hard. The number of hypothetical assignments between the components of two graphs under comparison grows factorially with the size of the graphs, and the test of each hypothesized match is a complex task in itself.

Comparing graphs might require exponential time in the most general case, but some algorithms run faster in the average case. Many successful graph isomorphism algorithms exploit local graph properties called isomorphism invariants. For instance, for a vertex of one graph to correspond to a given vertex in another, both vertices must have the same number of incident edges. Table 4-1 shows the edge-adjacency counts for the vertices in the graphs of Figure 4-1 sorted in increasing order. A glance at this list can instantly rule out graphs A and D as matches for either one another or graphs B or C. Adjacency counts like these are cheap to compute and can help a great deal toward quickly showing that different graphs do not match.

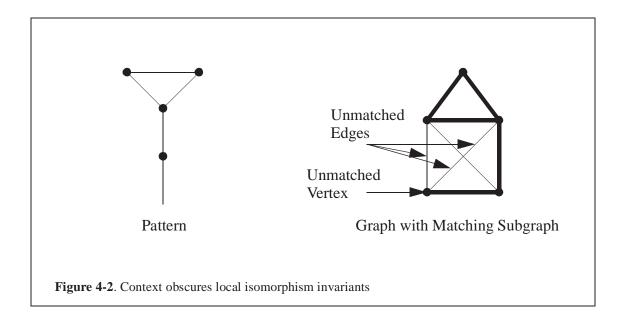

Turning back to the initial problem of *sub*graph isomorphism, the matching problem is confounded further still. A matching subgraph, in context, will likely have incident edges or vertices from the surrounding graph which do not belong to the subgraph, as illustrated

| Table 4-1. Adjacent Edge Counts per Vertex, Sorted |         |         |         |  |  |  |  |

|----------------------------------------------------|---------|---------|---------|--|--|--|--|

| Graph D                                            | Graph C | Graph B | Graph A |  |  |  |  |

| 2                                                  | 2       | 2       | 2       |  |  |  |  |

| 2                                                  | 2       | 2       | 3       |  |  |  |  |

| 3                                                  | 3       | 3       | 3       |  |  |  |  |

| 3                                                  | 3       | 3       | 3       |  |  |  |  |

| 3                                                  | 4       | 4       | 3       |  |  |  |  |

| 5                                                  | 4       | 4       | 4       |  |  |  |  |

in Figure 4-2. Before a subgraph matching problem resembles a graph matching problem, it must be determined which of the edges and vertices in a graph form a candidate for a matching subgraph. Without this determination local isomorphism invariants are difficult to find and use. What was already a computationally difficult problem, graph isomorphism, has only been made worse when generalized to subgraph isomorphism.

A search for subcircuits in a netlist constitutes a subgraph isomorphism problem. Fortunately, subcircuit matches can be found in large VLSI netlists reasonably quickly despite the innate difficulty of the general problem. Characteristics of both typical patterns and typical VLSI netlists simplify the problem enormously:

- Many practical patterns will contain nets which are "local" to that pattern matches of this pattern are expected to appear in the netlist exactly as they appear in the pattern, with no additional adjacent devices. In these cases a useful local isomorphism invariant has been made available.

- Netlists are bipartite graphs, with nets and devices as vertices and terminal connections as arcs. The usual VLSI devices, transistors, resistors, capacitors, and so forth, have a fixed, small number of terminals, never more than four. This property constrains the perplexity of VLSI graphs.

- Devices and terminal connections are both labeled, for instance, "nfet", "pfet", "npn", "resistor", "gate", "emitter", "source", "drain", and so on.

- While a net can potentially have enormous numbers of adjacent devices, there are usually few such nets, and those nets are easily identified, "special" nets: power rails, clocks, and biases, for instance. In most device netlists, non-"special" nets have a

small average fanout that does not increase with the size of the netlist. This observation indicates that the perplexity of VLSI graphs is empirically less than for the most general type of graph.

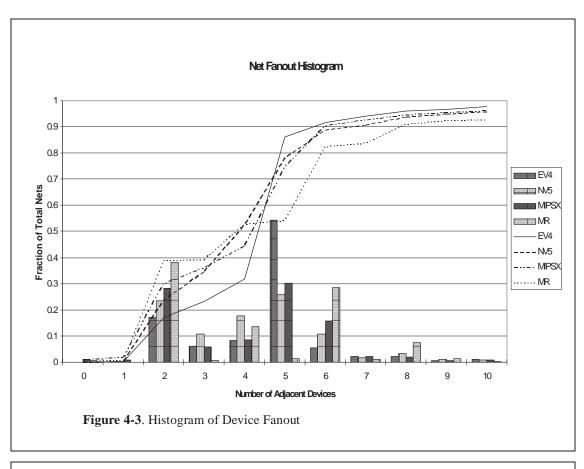

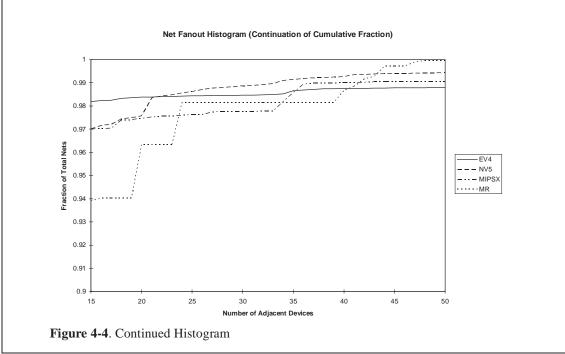

Of these characteristics, it is largely the sparsity of VLSI netlists (discounting power rails and clocks) that enables matching algorithms to achieve good average performance. To quantify the average sparseness of VLSI device netlists, fanout statistics from four designs

|                                               | Design    |                |                |                |

|-----------------------------------------------|-----------|----------------|----------------|----------------|

|                                               | MR        | MIPSX[10]      | NV5[9]         | EV4[8]         |

| Description                                   | Router    | Microprocessor | Microprocessor | Microprocessor |

| Total Number of Devices                       | 7143      | 43540          | 740716         | 1695691        |

| Total Number of Nets                          | 2867      | 18572          | 31224          | 662214         |

| Average Number of Adjacent<br>Devices per Net | 7.47      | 7.02           | 7.11           | 7.68           |

| Excluded Nets                                 | Vdd, GND, | Vdd, GND,      | VDD, VSS,      | Vdd, VSS, CLK  |

|                                               | reset_b   | Phi1, Phi1_b,  | Phi1*, Phi2*,  |                |

|                                               |           | Phi2, Phi2_b,  | Phi3*, Phi4*   |                |

|                                               |           | Vbias          |                |                |

Table 4-2. Fanout Statistics for Four Netlists