## **HIGH-SPEED BICMOS MEMORIES**

**Drew Eric Wingard**

**Technical Report No. CSL-TR-95-659**

January 1995

This research has been supported by ARPA contract N00039-91-C-0138. The author also acknowledges support from a National Science Foundation Graduate Fellowship.

#### **HIGH-SPEED BICMOS MEMORIES**

#### **Drew Eric Wingard**

#### **Technical Report: CSL-TR-95-659**

January 1995

Computer Systems Laboratory Departments of Electrical Engineering and Computer Science Stanford University Stanford, California 94305-4055

#### **Abstract**

Existing BiCMOS static memories do not simultaneously combine the speed of bipolar memories with the low power and density of CMOS memories. Beginning with fundamentally fast low-swing bipolar circuits and zero-power CMOS storage latches, we introduce CMOS devices into the bipolar circuits to reduce the power dissipation without compromising speed and insert bipolar transistors into CMOS storage arrays to improve the speed without power nor density penalties.

Replacing passive load resistors with switched PMOS transistors reduces the amount of power required to keep bipolar decoder outputs low. The access delay need not increase because the load resistance is quickly reduced via a low-swing signal when the decoder could switch. For ECL NOR decoders, we apply a variable BiCMOS current source that is simplified by carefully regulating the negative supply. We also develop techniques that improve the reading and writing characteristics of the CMOS-storage, emitter-access memory cell.

A 16K-word 4-bit asynchronous CSEA memory was fabricated in a 0.8-µm BiCMOS technology and accesses in 3.7ns while using 1.75W. An improved 64Kx4 design is simulated to run at 3.4ns and 2.3W. Finally, a synchronous 4Kx64 CSEA memory is estimated to operate at 2.5ns and 2.4W in the same process technology.

<u>Key Words and Phrases:</u> static memories (SRAM), BiCMOS circuit techniques, low-swing signalling, CSEA memory cell, pulsed circuits

Copyright © 1994

by

Drew Eric Wingard

## Acknowledgments

I must start off by thanking my advisor, Prof. Mark Horowitz. He sets seemingly impossibly high standards by example, and challenges his students to accomplish more than they thought possible. I will never forget our meetings, where he would often point out the shortcomings in my ideas before I was halfway through revealing them — of course I will especially remember the few (but increasingly more frequent) times when I was actually right. On top of the delight of intellectual challenge, he is a truly nice person who encourages his students (again by example) to expand their horizons at Stanford by pitching in and helping other researchers in areas where our group is strong.

I would also like to thank my associate advisor, Prof. Bruce Wooley, who provided so many interesting research attractions and distractions. The best examples of each were the sigma-delta chip, with Brian Brandt and the kind folks at TI, and my "endless" Cadence purgatory. At least Bruce had to read this thesis! I am greatly indebted to Prof. John Gill, who had the unenviable task of chairing my orals committee and reading a thesis outside his field. Thanks also to Prof. Greg Kovacs, who sat on my orals committee.

A number of people and organizations helped with this research. Don Stark was distracted from his own thesis for long enough to do some substantial layout, and essentially all of the verification, of the fabricated SRAM. Mark Horowitz spent more long nights helping than any of us care to remember. The staff of Texas Instrument's Semiconductor Process and VLSI Design Laboratories built and helped test that memory. In particular, I would like to thank Harvey Davis, Lisa Dyson, Eng Born, and Bob Garcia for mask generation, die assembly, and testing assistance and Tom Holloway for fabrication. Ashwin Shah, David Scott, Bob Hughes, and Pallab Chatterjee supported this project within TI. Furthermore, Jay Glanville (then at Seiko Instruments), the Integrated Systems Laboratory at USC/ISI, and Jim McVittie and Steven Taylor at Stanford's IC Lab helped debug and modify the design errors. This research was also supported by a National Science Foundation Graduate Fellowship, and by Advanced Research Projects Agency Contract No. N00039-91-C-0138.

Eight years is a long time to work on anything. For me, it felt more like working on everything. Faces and projects that I'll remember include Brian and the sigma-delta, John Shott *et al.* and the Stanford BiCMOS project, Mike Smith, John Maneatis, Don Ramsey, Tom Chanak, Phil Lacroute, *et al.* and TORCH, and Marc Loinaz, Peter Lim, and the OaCIS stockers.

I've also been fortunate to run into a bunch of people to have fun with: the CIS softball team, the basketball@blaze group, the birthday club (Brian & Jan, Greg & Joan, Paul, Dave, Brian L., Walter, and Pete), and the "boys" of the Oak Grove Hotel — Ajay, Chris, Erich, Ike, Joost, Larry, and Wolf.

My family deserves recognition for supporting me both emotionally and financially, and especially for never getting tired of hearing, "I'll be done in another <year|month|week>." My best friend, Eric Freeman, put forth virtually all of the effort to keep in touch while I convinced myself that I was too busy to call. I'd also like to thank Tracey Sealer for convincing me to go to graduate school in the first place.

My most memorable experience that I'll take away from Stanford began when I volunteered (once again) to work on something other than my thesis. And ended up getting much more involved than I would have ever dreamed — but not with the project. Instead, I fell in love. Laura Schrager has shown me more patience and support than I could have ever hoped, and so I must thank her most of all. Forever.

# **Table of Contents**

| Acknowledgments                                    | iii |

|----------------------------------------------------|-----|

| Table of Contents                                  | V   |

| List of Tables                                     | ix  |

| List of Figures                                    | xi  |

| Chapter 1 Introduction                             | 1   |

| Chapter 2 High Speed Static Memory Subsystems      | 5   |

| 2.1 Static Memory Basics                           | 5   |

| 2.1.1 Fast SRAM Organization and Conventions       | 7   |

| 2.1.2 Decoders                                     | 9   |

| 2.1.3 Column Read/Write Circuits                   | 11  |

| 2.1.4 Banks                                        | 11  |

| 2.2 CMOS Static Memories                           | 13  |

| 2.2.1 CMOS Static Memory Cells                     | 14  |

| 2.2.2 Complete CMOS SRAMs                          | 16  |

| 2.2.3 Reducing CMOS SRAM Delay                     |     |

| 2.3 Bipolar Static Memories                        | 20  |

| 2.3.1 Bipolar Static Memory Cells                  | 22  |

| 2.3.2 Complete Bipolar SRAMs                       | 24  |

| 2.4 BiCMOS Static Memories                         |     |

| 2.4.1 BiCMOS Design Styles                         |     |

| 2.4.2 Complete BiCMOS SRAMs                        | 29  |

| 2.5 Summary                                        | 31  |

| Chapter 3 Low-swing BiCMOS Decoders                | 35  |

| 3.1 Bipolar Decoder Power Dissipation              |     |

| 3.2 Pre-decoding for Diode Decoders                |     |

| 3.3 Diode Decoder with Switched PMOS Load Resistor |     |

| 3.3.1 Basic Operation                              |     |

| 3.3.2 Switched PMOS Load Design Considerations     |     |

| 3.3.3 Reference Generation                         |     |

| 3.3.4 Address Line Sharing                         | 46  |

| 3.3.5 Results                                                                                                                                 | 47                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 3.4 Pulsed Diode Decoders                                                                                                                     | 49                               |

| 3.4.1 Basic Operation                                                                                                                         | 50                               |

| 3.4.2 Capacitively-pulsed Diode Decoders                                                                                                      | 52                               |

| 3.4.3 NMOS Capacitor Diode Decoders                                                                                                           | 54                               |

| 3.4.4 Summary                                                                                                                                 | 56                               |

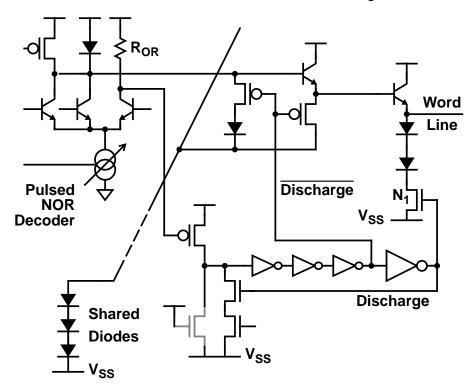

| 3.5 Pulsed NOR Decoders                                                                                                                       |                                  |

| 3.5.1 Basic Operation                                                                                                                         | 59                               |

| 3.5.2 Pulsed Current Source                                                                                                                   | 60                               |

| 3.5.3 Pulsed Address Buffers and Address Line Drivers                                                                                         | 62                               |

| 3.5.4 Bank Selection                                                                                                                          | 66                               |

| 3.5.5 Reference Generation                                                                                                                    | 68                               |

| 3.5.6 Summary                                                                                                                                 | 70                               |

| 3.6 Word Line ECL-CMOS Converter                                                                                                              | 71                               |

| 3.6.1 Low-Power Word Line Level Converter                                                                                                     | 72                               |

| 3.6.2 Use in Pulsed Word Line Discharge                                                                                                       | 73                               |

| 3.7 Summary                                                                                                                                   | 75                               |

|                                                                                                                                               |                                  |

| Chapter 4 Sense and Write Techniques for CSEA Memories                                                                                        | 77                               |

|                                                                                                                                               | -                                |

| 4.1 CSEA Basics                                                                                                                               |                                  |

| 4.1 CSEA Basics         4.2 Single-ended Bit Line Sensing                                                                                     |                                  |

|                                                                                                                                               | 81                               |

| 4.2 Single-ended Bit Line Sensing                                                                                                             |                                  |

| <ul><li>4.2 Single-ended Bit Line Sensing</li><li>4.2.1 Simplified Sensing</li></ul>                                                          |                                  |

| <ul><li>4.2 Single-ended Bit Line Sensing</li><li>4.2.1 Simplified Sensing</li><li>4.2.2 Effects of Emitter and Bit Line Resistance</li></ul> | 81<br>82<br>84<br>86             |

| <ul> <li>4.2 Single-ended Bit Line Sensing</li></ul>                                                                                          | 81<br>82<br>84<br>86<br>91       |

| <ul> <li>4.2 Single-ended Bit Line Sensing</li></ul>                                                                                          | 81<br>82<br>84<br>86<br>91<br>91 |

| <ul> <li>4.2 Single-ended Bit Line Sensing</li></ul>                                                                                          |                                  |

| <ul> <li>4.2 Single-ended Bit Line Sensing</li></ul>                                                                                          |                                  |

| <ul> <li>4.2 Single-ended Bit Line Sensing</li></ul>                                                                                          |                                  |

| <ul> <li>4.2 Single-ended Bit Line Sensing</li></ul>                                                                                          |                                  |

| <ul> <li>4.2 Single-ended Bit Line Sensing</li></ul>                                                                                          |                                  |

| <ul> <li>4.2 Single-ended Bit Line Sensing</li></ul>                                                                                          |                                  |

| <ul> <li>4.2 Single-ended Bit Line Sensing</li></ul>                                                                                          |                                  |

| <ul> <li>4.2 Single-ended Bit Line Sensing</li></ul>                                                                                          |                                  |

| <ul> <li>4.2 Single-ended Bit Line Sensing</li></ul>                                                                                          |                                  |

| <ul> <li>4.2 Single-ended Bit Line Sensing</li></ul>                                                                                          |                                  |

| <ul> <li>4.2 Single-ended Bit Line Sensing</li></ul>                                                                                          |                                  |

| Chapter 5 Results                 |     |

|-----------------------------------|-----|

| 5.1 An Experimental 64K CSEA SRAM | 114 |

| 5.1.1 Cell Design                 | 114 |

| 5.1.2 Organization                | 115 |

| 5.1.3 Measured Results            |     |

| 5.2 Proposed 256K CSEA SRAM       |     |

| 5.2.1 Results                     |     |

| 5.3 A Synchronous 256K CSEA SRAM  |     |

| 5.4 Summary                       |     |

| Chapter 6 Conclusion              |     |

| 6.1 Future Work                   | 130 |

| Chapter 7 Bibliography            |     |

# **List of Tables**

| Table 1-1 | Process Characteristics     | 3    |

|-----------|-----------------------------|------|

| Table 5-1 | 4K×64 SRAM Power Variation  | .127 |

| Table 5-2 | SRAM Performance Comparison | .128 |

# **List of Figures**

| Figure 2-1  | External SRAM Interface                            | 7   |

|-------------|----------------------------------------------------|-----|

| Figure 2-2  | Internal SRAM Organization                         | 9   |

| Figure 2-3  | Basic Decoder Structure                            | .10 |

| Figure 2-4  | Banked SRAM Organization                           | .13 |

| Figure 2-5  | A CMOS NAND Gate                                   | .14 |

| Figure 2-6  | A 6T CMOS Memory Cell                              | .15 |

| Figure 2-7  | Simplified CMOS SRAM Read Access Path              | .17 |

| Figure 2-8  | An ECL NOR Gate                                    | .21 |

| Figure 2-9  | Schottky Barrier Diode Load Memory Cell            | .22 |

| Figure 2-10 | Bipolar Decoders                                   | .25 |

| Figure 2-11 | Bipolar SRAM Read Access Path                      | .27 |

| Figure 2-12 | BiCMOS SRAM Read Access Path                       | .32 |

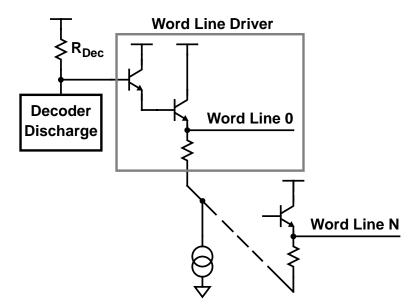

| Figure 3-1  | Simplified Word Line Driver                        | .36 |

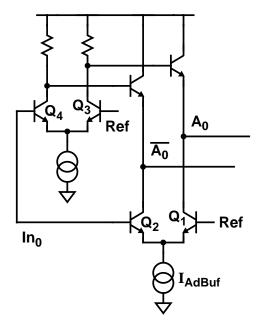

| Figure 3-2  | A Push-pull Address Buffer                         | .38 |

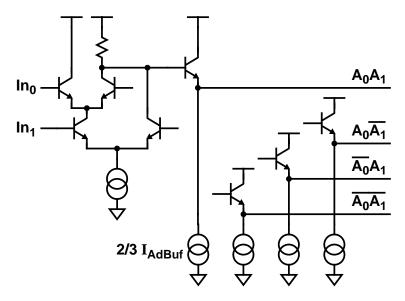

| Figure 3-3  | A Pre-decoding Address Buffer                      | .39 |

| Figure 3-4  | A PMOS Load Diode Decoder                          | .40 |

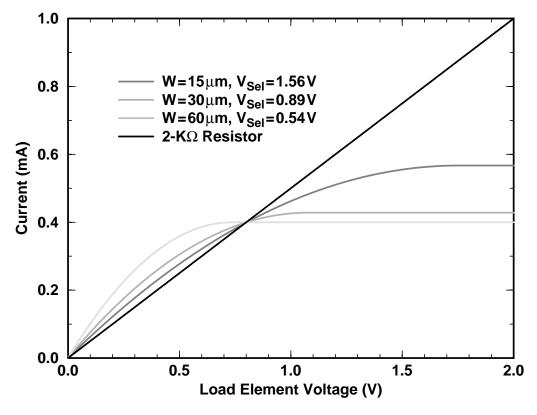

| Figure 3-5  | PMOS Load Characteristics                          | .43 |

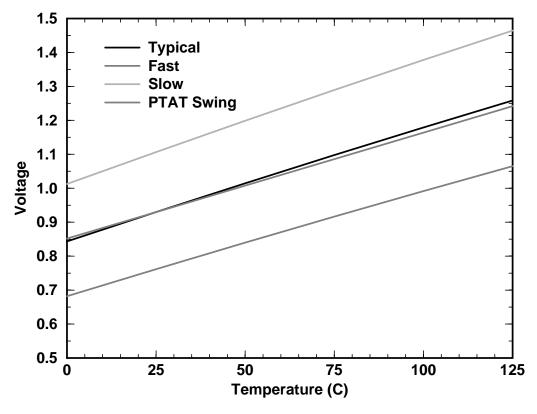

| Figure 3-6  | PMOS Load Gate Swing Over Process and Temperature  | .44 |

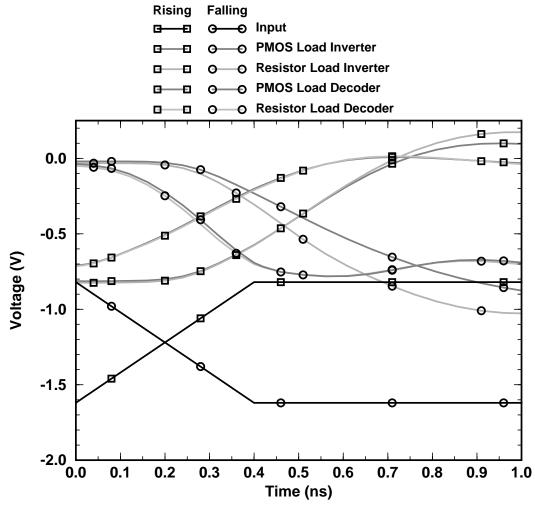

| Figure 3-7  | Gate Switching Waveforms for PMOS Loads            | .45 |

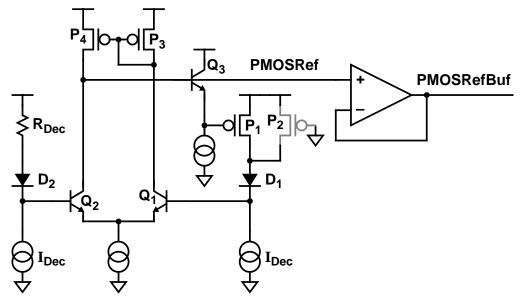

| Figure 3-8  | PMOS Load Reference Generator                      | .46 |

| Figure 3-9  | Address Buffer with Segmented Address Lines        | .47 |

| Figure 3-10 | Advantages of Pulsed Signalling for Diode Decoders | .51 |

| Figure 3-11 | A Capacitively-Pulsed Diode Decoder                | .52 |

| Figure 3-12 | A NMOS Capacitor Pulsed Diode Decoder              | .54 |

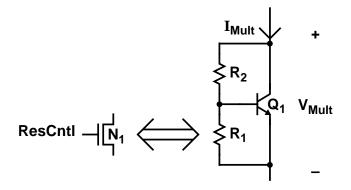

| Figure 3-13 | An Adjustable V <sub>BE</sub> Multiplier           | .55 |

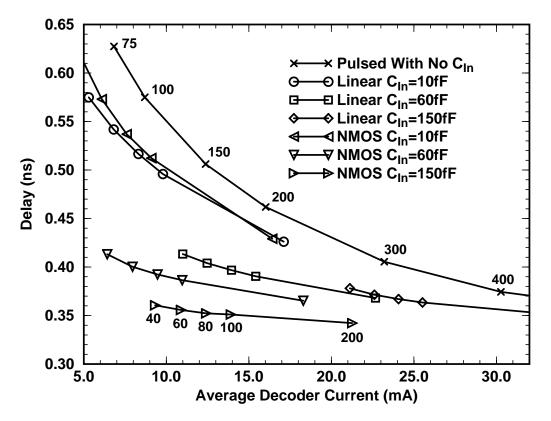

| Figure 3-14 | Power/Delay Comparison of Pulsed Diode Decoders    | .57 |

| Figure 3-15 | A Pulsed NOR Gate                                  | .59 |

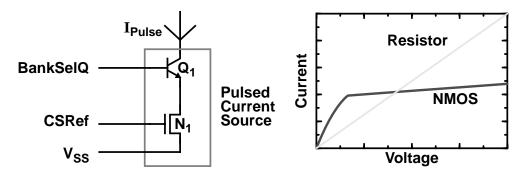

| Figure 3-16 | Variable Level Shift for Pulsed Current Sources    | .61 |

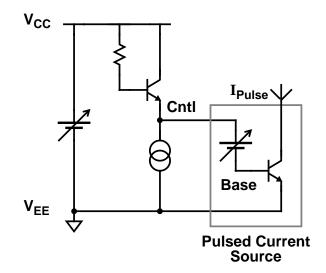

| Figure 3-17 | A Pulsed Current Source                            | .61 |

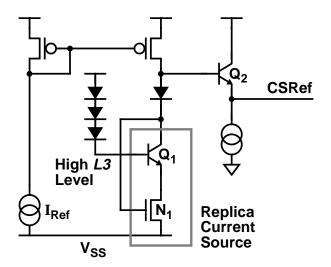

| Figure 3-18 | Pulsed Current Source Reference                    | .63 |

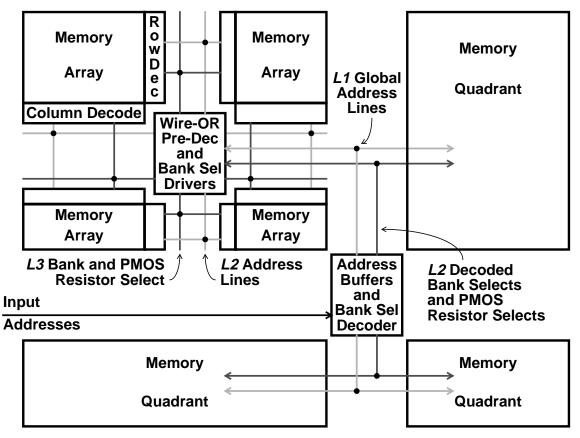

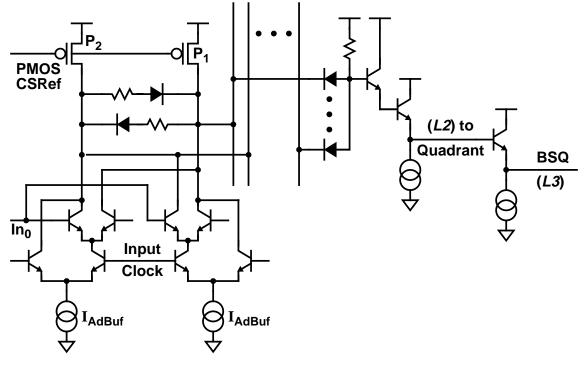

| Figure 3-19 | Pulsed Address Line Routing                        | .65 |

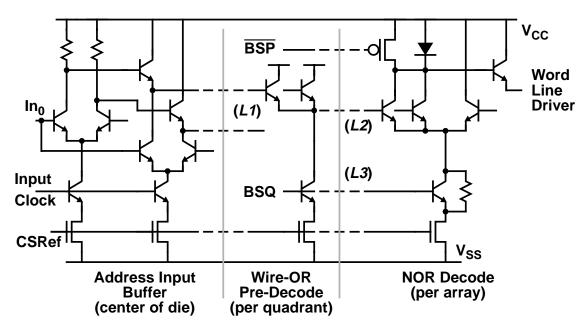

| Figure 3-20 | A Pulsed Address Buffer with Pulsed Address Lines  | .65 |

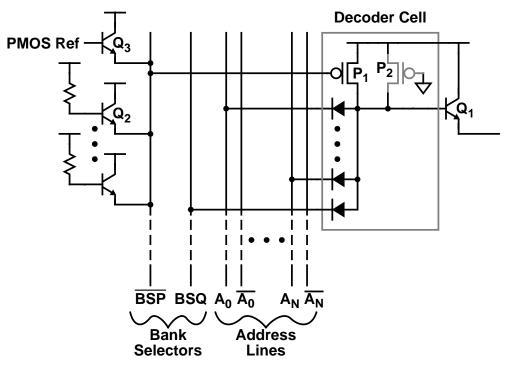

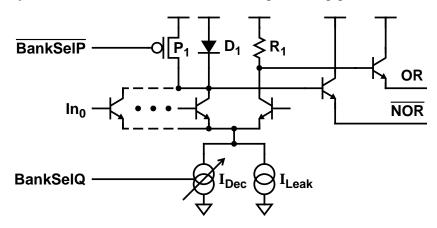

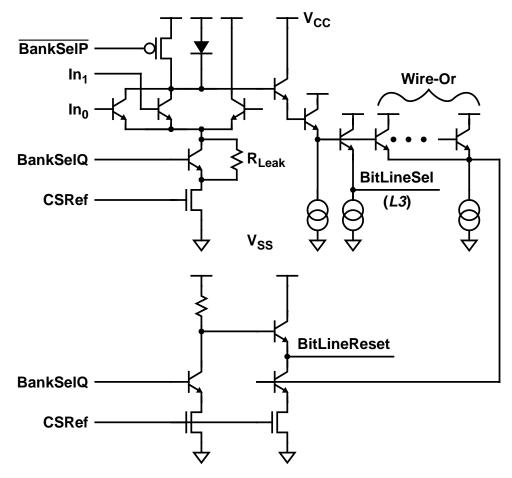

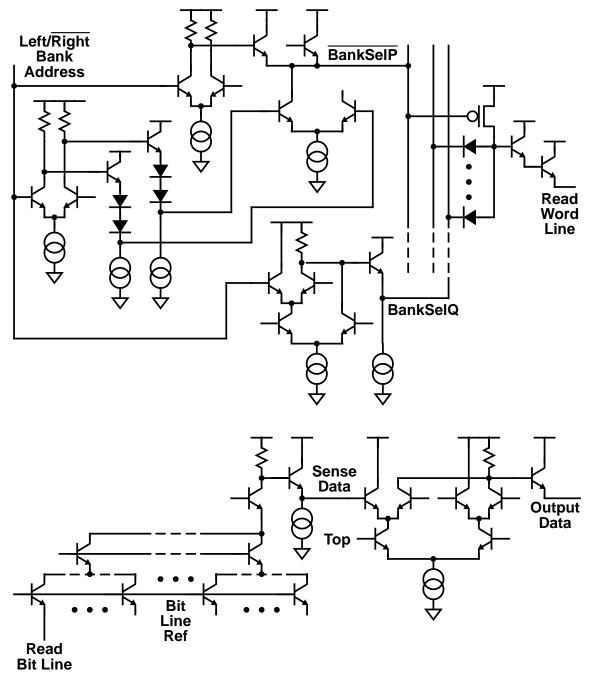

| Figure 3-21 | A Pulsed Bank Selection Decoder                    | .67 |

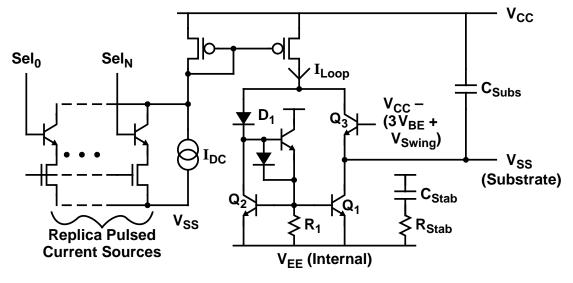

| Figure 3-22 | A V <sub>SS</sub> Generator                        | .69 |

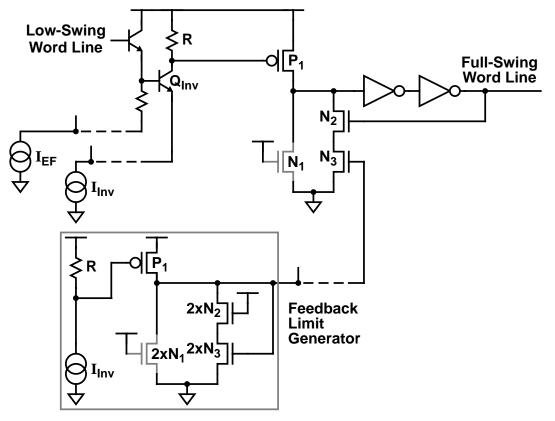

| Figure 3-23 | A Word Line Level Converter                               | 73  |

|-------------|-----------------------------------------------------------|-----|

| Figure 3-24 | A Level Converter-Based Pulsed Word Line Discharge System | 74  |

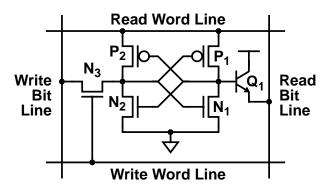

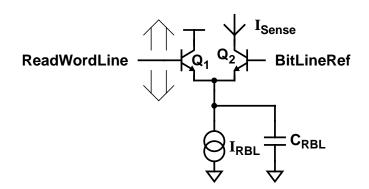

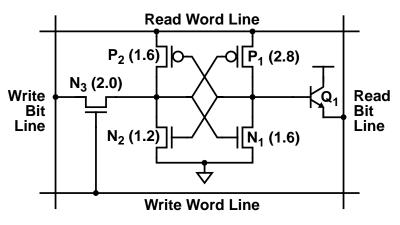

| Figure 4-1  | CMOS-Storage, Emitter-Access Memory Cell                  | 78  |

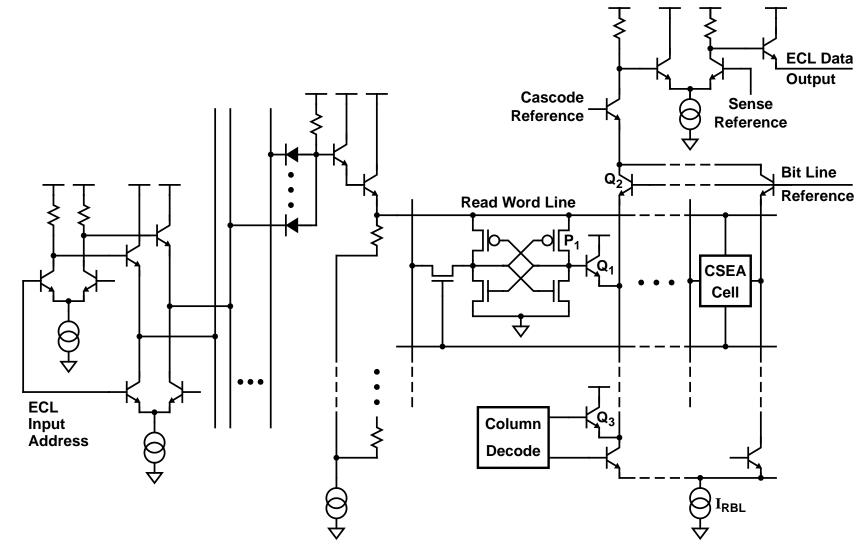

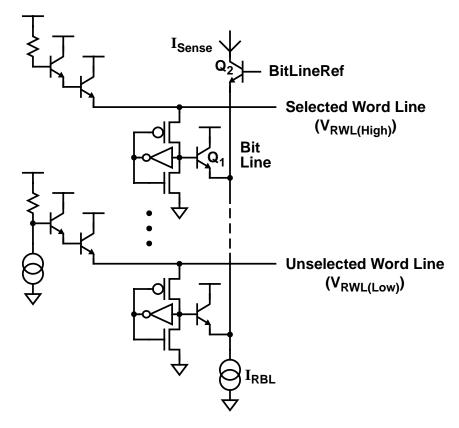

| Figure 4-2  | CSEA Memory Read Access Path                              | 80  |

| Figure 4-3  | CSEA Cell Bit Line Sensing Model                          | 83  |

| Figure 4-4  | Model for Worst-Case Reading Zero                         | 84  |

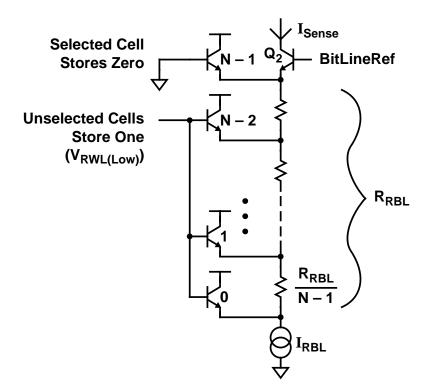

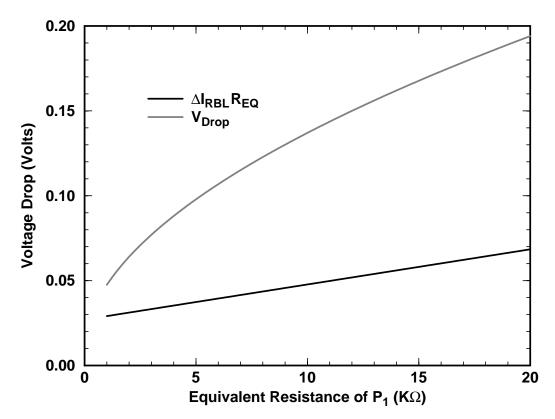

| Figure 4-5  | Read Word Line Swing Variation                            | 87  |

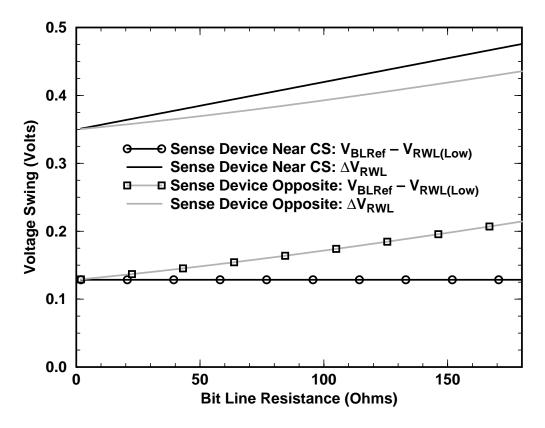

| Figure 4-6  | $V_{\text{Drop}}$ Dependence on $R_{P1}$                  | 90  |

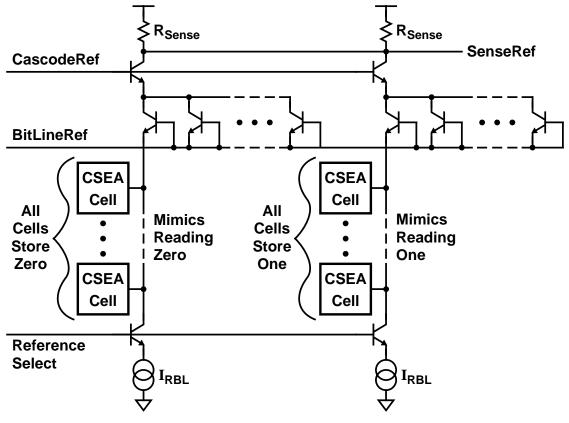

| Figure 4-7  | Sense Amplifier Reference Circuit                         |     |

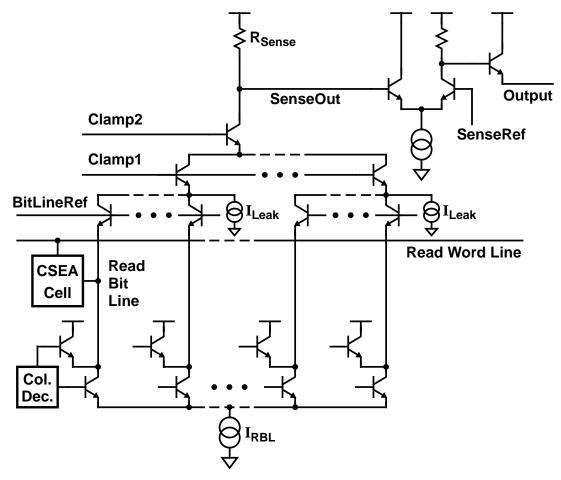

| Figure 4-8  | A Two-Level Cascode Sense Amplifier                       | 95  |

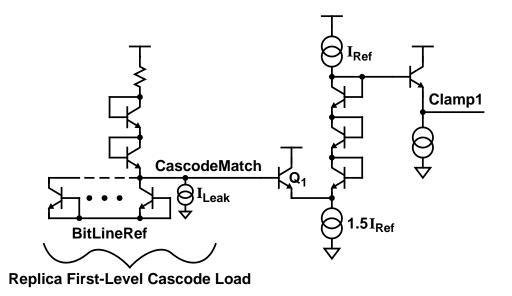

| Figure 4-9  | Clamp1 Reference Generator                                | 97  |

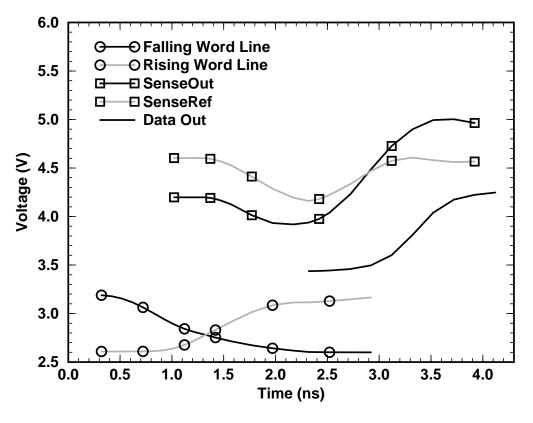

| Figure 4-10 | Sense Path Performance with Supply Noise                  | 98  |

| Figure 4-11 | Oversimplified Bit Line Sense Model                       | 99  |

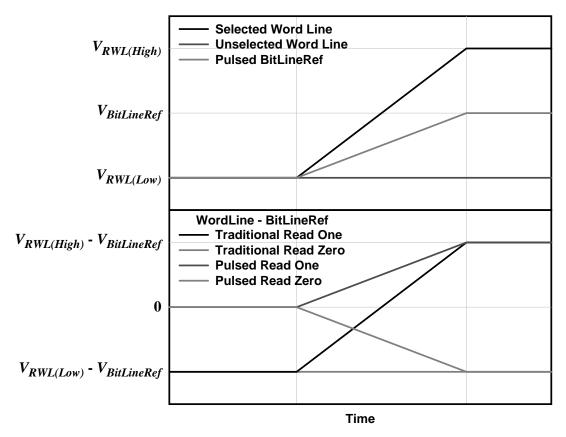

| Figure 4-12 | Comparison of Switching Waveforms                         | 100 |

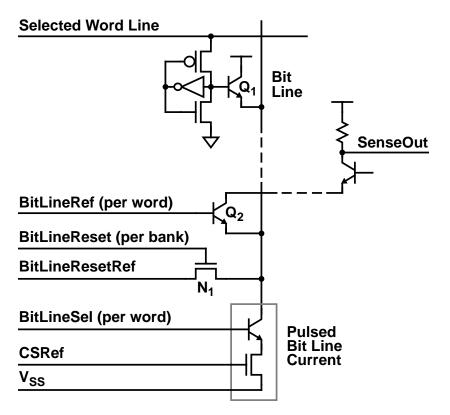

| Figure 4-13 | A Pulsed CSEA Bit Line                                    | 102 |

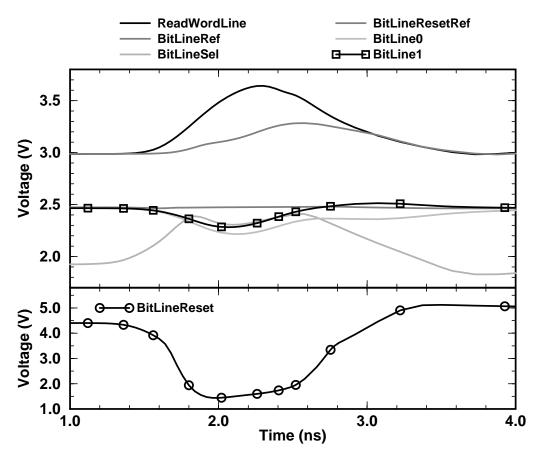

| Figure 4-14 | Simulated Pulsed Bit Line Waveforms                       | 103 |

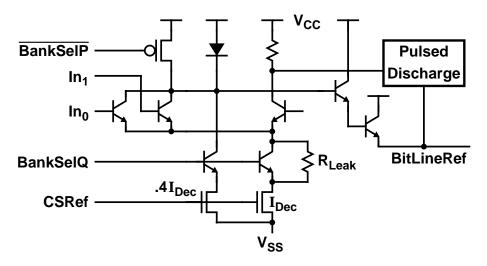

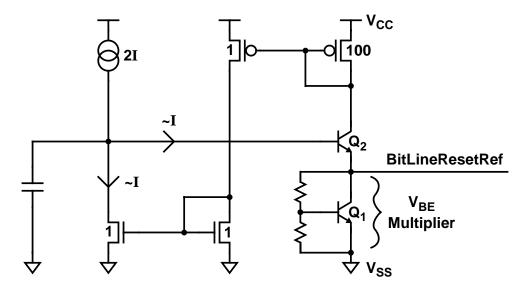

| Figure 4-15 | Pulsed Bit Line Reference                                 | 105 |

| Figure 4-16 | Pulsed Bit Line Control Circuits                          | 105 |

| Figure 4-17 | Pulsed Bit Line Reset Reference                           | 106 |

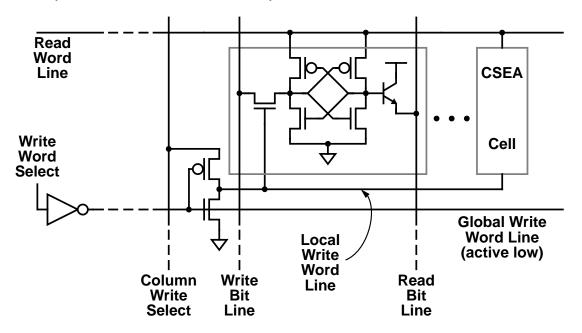

| Figure 4-18 | Write Qualification Circuit                               | 110 |

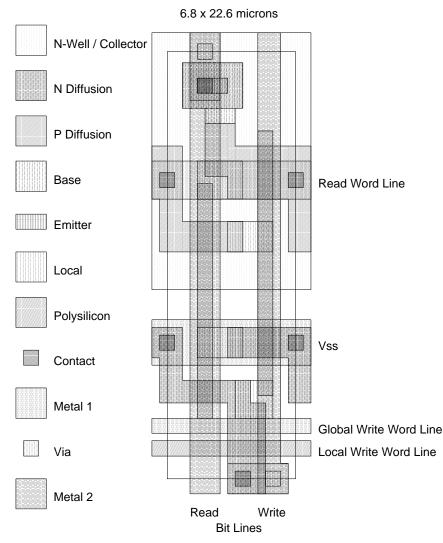

| Figure 5-1  | Fabricated CSEA Memory Cell                               | 115 |

| Figure 5-2  | CSEA Cell Layout                                          | 116 |

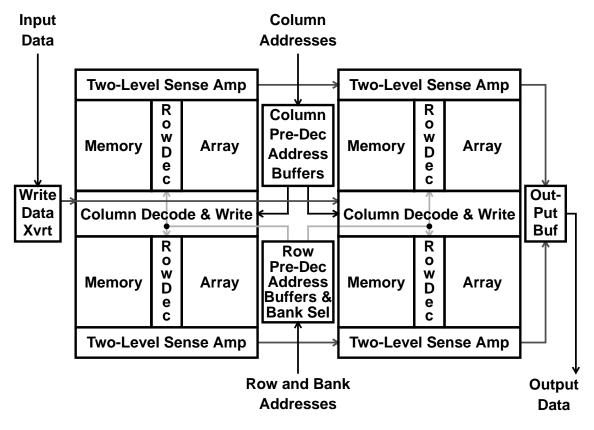

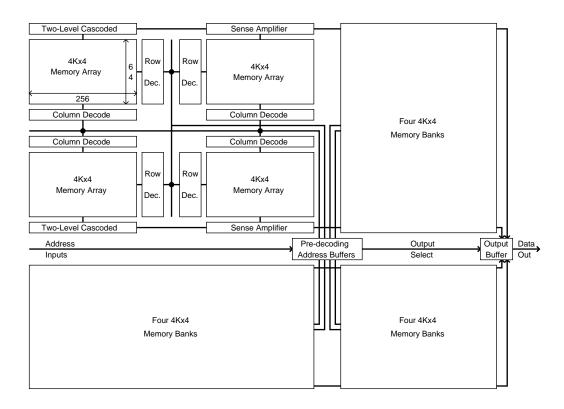

| Figure 5-3  | 16K×4 SRAM Organization                                   | 117 |

| Figure 5-4  | Critical Access Path for 16K×4 SRAM                       | 119 |

| Figure 5-5  | Chip Photomicrograph of 16K×4 CSEA SRAM                   | 120 |

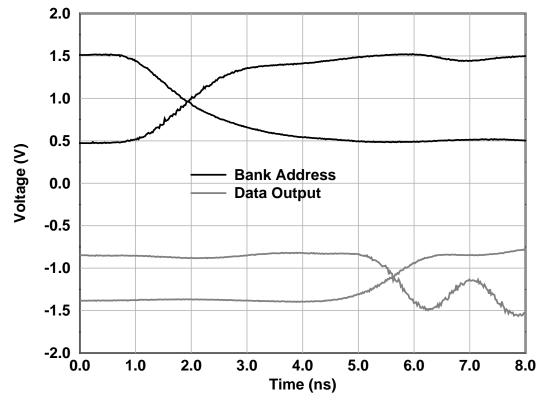

| Figure 5-6  | Oscillograph of Bank-switching Read Access                | 121 |

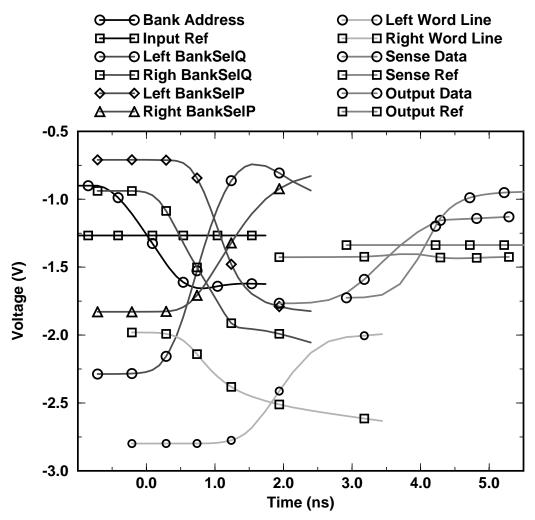

| Figure 5-7  | Simulated Switching Waveforms for 16K×4 SRAM              | 122 |

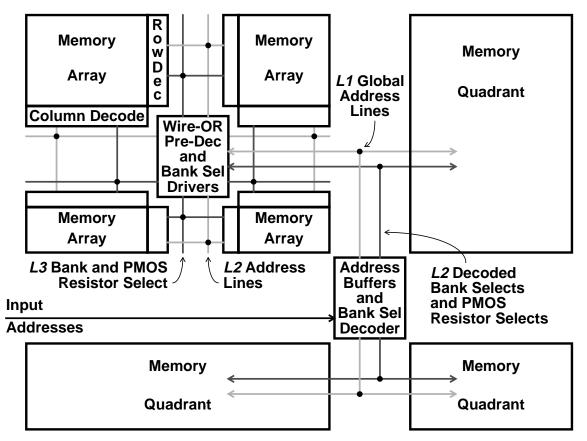

| Figure 5-8  | 64K×4 SRAM Organization                                   | 123 |

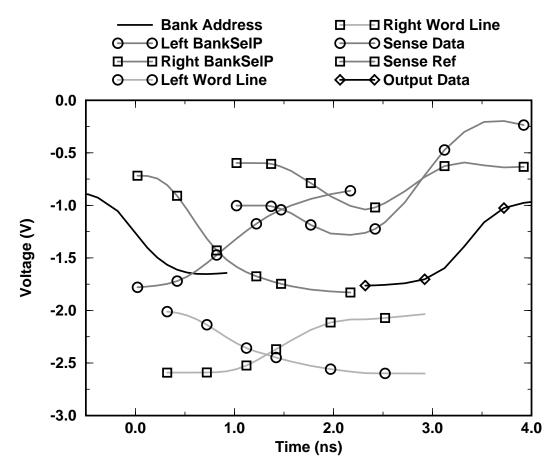

| Figure 5-9  | Simulated Switching Waveforms for 64K×4 SRAM              |     |

| Figure 5-10 | Pulsed Address Line Routing                               | 126 |

## Chapter 1

## Introduction

Changes in integrated circuit processing technology provide new challenges, and sometimes new opportunities, for SRAM designers. A case in point is BiCMOS. This relatively new technology, which integrates components from both bipolar and CMOS processes, offers the opportunity to design systems with the high switching speed of ECL bipolar circuits or the low power dissipation and high density of CMOS circuits. The challenge of BiCMOS circuit design is to achieve high speed, high density, and low power, simultaneously. The field of fast SRAMs provides an excellent arena in which to compare BiCMOS circuit designs, since SRAMs are simple to design, perform a useful function, and are very easy to compare. At the lower power end of the spectrum, a number of BiCMOS SRAMs achieve faster access than CMOS designs at nearly equivalent power and density [1 2 3]. However, at the other end, the BiCMOS memories with nearly-bipolar access times dissipate much more power than their CMOS counterparts [4 5]. This dissertation explores the use of BiCMOS technology to build very high-speed SRAMs at power and density levels appropriate for integration onto single-chip computers.

This thesis comprises six chapters. Since SRAM design is a highly developed field, this thesis builds upon many ideas from previous work. Chapter 2 provides background material for understanding the content and context of this work. After discussing SRAM organizational issues that affect performance, the chapter focuses on the performance characteristics of static memories fabricated in the major silicon-based integrated circuit technologies. In particular, the chapter zeroes in on the advantages and disadvantages of CMOS, bipolar, and BiCMOS memories in terms of speed, power, and capacity.

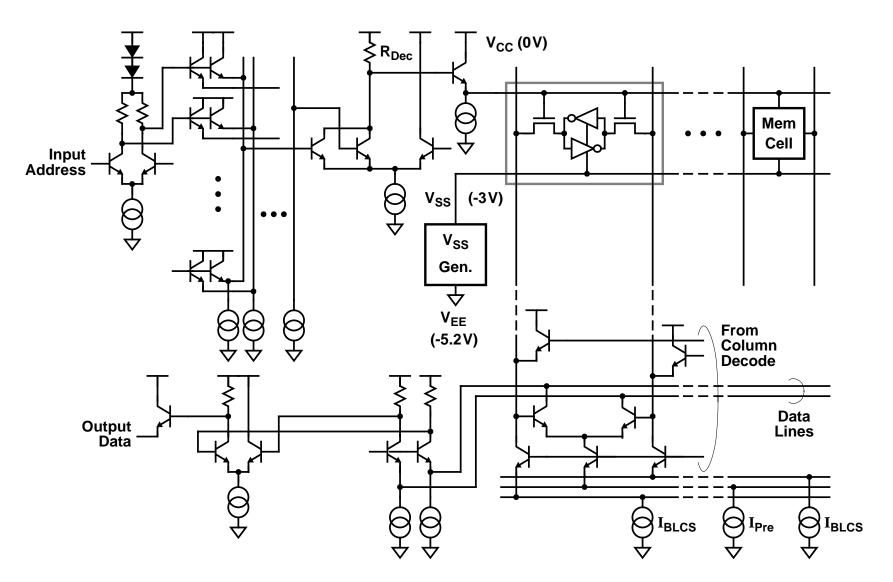

A major speed advantage of bipolar memories arises from the fast switching offered by low-swing bipolar decoders. Unfortunately, the power dissipation of bipolar decoders is prohibitive for many high-capacity applications. Chapter 3 introduces new techniques that reduce the power of low-swing decoders without substantially increasing the delay. By replacing the standard decoder load resistor with a switched PMOS transistor, gate currents and load resistances may be simultaneously varied so that a decoder gate dissipates much less current when it is unselected. If decoder selection is sufficiently rapid, then active transitions are not delayed. The chapter demonstrates this approach for improving the power dissipation of diode *AND* and ECL *NOR* decoders. For ECL *NOR* decoders, the switched PMOS load is combined with a new pulsed current source to reduce the average power of the decoder *NOR* gate. The pulsed signalling needed by such a gate has speed as well as power advantages, but places stringent requirements on the pulsed current sources and their supplies. To address this issue the chapter proposes a new on-chip supply generator that uses the capacitance of the memory arrays to supply the transient charge required by the current pulses. Finally, the chapter introduces a low-power ECL-CMOS level converter that is appropriate for providing pulsed word line discharge currents that improve both memory access time and power.

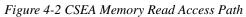

Another significant component of the access time in most BiCMOS memories results from the delay in amplifying the low-swing decoded address into sufficiently large voltages to access a CMOS memory cell. The CMOS-storage emitter-access (CSEA) memory cell, which has been previously integrated [6], is accessed with a low-swing word line, and thus has the potential for faster access. However, the CSEA cell requires careful design to overcome the limitations of its single-ended read port and full-swing write port. Chapter 4 describes techniques that provide fast and robust CSEA sensing and writing. A primary concern of low-swing single-ended reads is the effects of transient supply variation on the bit lines. The chapter opens with an analysis of the noise margin of CSEA bit line sensing in the presence of array parasitics and supply noise; the analysis shows that CSEA sensing can be robust due to the high read current supplied by the CSEA memory cell. However, the bit lines are only part of the problem, since the large amount of multiplexing required for large SRAMs leads to the use of very low-swing signalling elsewhere in the sense path. The chapter introduces a new two-level cascode sense amplifier that improves access time by reducing the capacitance on long global wires while maintaining excellent signal integrity in the presence of supply noise. For pulsed CSEA memories, a better solution is proposed that improves the delay by effectively beginning each access with the bit line close to its switching point. This method is especially applicable for wide access widths, where the column overhead of the pulsed sensing is reduced. Finally, the chapter attacks the write performance issues, by applying the word line ECL-CMOS level converter of Chapter 3 and a modified divided word line technique to provide fast writes with large noise margin and small cell area.

Chapter 5 puts together the work of Chapters 3 and 4 by exploring the design of several different CSEA SRAMs. It reports experimental results of a  $16K \times 4$  CSEA memory that delivers 3.7-ns read access time in a 0.8-µm BiCMOS process technology [7 8]. This technology provides 0.8-µm NMOS and PMOS channel lengths with silicided polysilicon and diffused regions, a 7-GHz  $f_T$  NPN bipolar transistor, and 3 levels of tungsten metallization. Important process characteristics are summarized in Table 1-1. Because this was the fabrication technology for the experimental memory, it is also used throughout this thesis as the process for circuit exploration and simulation; in this way fair comparisons are possible between fabricated and simulation-based designs. While the  $16K \times 4$  memory utilizes several of the design techniques of this thesis, the  $64K \times 4$  simulation-based design of Section 5.2 provides faster (3.4ns) and more robust reads due to the incorporation of improved circuits from Chapters 3 and 4. This performance level is achieved at much lower power than has been reported for bipolar memories. The pulsed circuit techniques of this thesis offer additional speed and power advantages for synchronous static memories. Chapter 5 describes a complete pulsed BiCMOS memory that offers 2.5-ns access time at a power dissipation of less than 3W. These designs show the performance advantages that can be achieved by combining CMOS transistors into low-swing ECL-style logic gates.

| Parameter                     | Value         |

|-------------------------------|---------------|

| Minimum NPN Emitter           | 1.6µm × 0.8µm |

| ΝΡΝ β                         | 100           |

| NPN $f_T$                     | 7GHz          |

| NMOS/PMOS Minimum Gate Length | 0.8µm         |

| NMOS/PMOS t <sub>ox</sub>     | 20nm          |

| Contacted First Metal Pitch   | 2.8µm         |

| Contacted Second Metal Pitch  | 2.8µm         |

| Contacted Third Metal Pitch   | 3.2µm         |

Table 1-1 Process Characteristics

The final chapter summarizes the contributions of this thesis. It also suggests a few areas where additional research could advance these results.

## Chapter 2

## **High Speed Static Memory Subsystems**

This thesis focuses on circuit design techniques for high performance BiCMOS static memories. In order to provide a framework for understanding the techniques and the issues behind them, this chapter provides an overview of high-speed SRAM design. The chapter discusses basic SRAM structures and terminology, and provides historical perspective on the circuits used in SRAMs. In particular, the design of SRAMs in CMOS, bipolar, and BiCMOS technologies is described, because the techniques of Chapters 3 and 4 borrow and expand upon circuits and concepts from each of the three technologies.

The chapter's organization reflects these goals. Section 2.1 introduces the architectural structure and function of a typical SRAM as well as the SRAM terminology used in this thesis. Section 2.2 discusses high-speed memories built exclusively from CMOS transistors. While its extremely low static current memory cell and high packing density once provided its principal advantages, new circuit techniques and faster devices have rapidly closed the access time penalty versus bipolar and BiCMOS designs. Section 2.3 describes the fastest silicon memories currently built — those constructed from high-speed bipolar technology. While density and power considerations prevent the use of bipolar memories in most systems, low-swing access techniques developed for these SRAMs are widely and increasingly being applied to other technologies. SRAMs built using the hybrid technology BiCMOS are the topic of Section 2.4. The additional design flexibility inherent in BiCMOS has produced a wide variety of performance tradeoffs, including some SRAMs with nearly-bipolar speed and nearly-CMOS power and density.

## 2.1 Static Memory Basics

All computer memories have a mechanism for storing their data, but *static* memories are unique because they utilize active devices that are connected in a positive feedback loop to retain their data. The active feedback allows static memories to hold their data as long as

power is applied. In contrast, *dynamic* memories typically store their data as charge on a capacitor, and since the charge may leak away, the data can be lost unless it is *refreshed* (i.e. re-stored). All of the memories of this thesis are *random-access memories* (RAMs), which says that external circuitry may access the stored data in an arbitrary order. Some other types of static memories, such as queues, do not allow random access. Furthermore, a RAM supports both *writing* (i.e. updating) and *reading* (i.e. interrogating) the stored data at roughly equal speeds and in an arbitrary ordering. The memories described in this thesis are thus all termed static RAMs, or SRAMs.

RAMs are typically compared on the basis of four performance metrics:

- Capacity how many bits of data the memory may store at once

- Power how much power the memory requires to operate

- Read Access Time how much delay exists between the time when the system presents an address to the memory and the time when the memory presents the read data back to the system

- Write Cycle Time how much delay exists between the time when the system presents both data to be written and the address at which to write and the time when the memory is prepared to accept further read or write requests from the system

SRAMs have performance advantages over other memories which make them suitable for certain applications. First, SRAMs that are fabricated in CMOS technologies can have very low standby power, so CMOS SRAMs are very attractive for low-power applications such as battery-powered systems; dynamic memories suffer the disadvantage of power-consuming refresh cycles. Second, SRAMs usually offer significantly faster access and cycle times than other memories. This advantage makes SRAMs popular for high-speed buffer memories and cache memories. A final advantage is that SRAMs are readily built in the same technologies used for building large digital circuits such as microprocessors, so SRAMs are increasingly used as fast on-board memories for high-integration digital integrated circuits. These advantages outweigh the principal disadvantage of SRAMs: they tend to have lower capacity than dynamic memories, due to the larger number of active devices in an SRAM memory cell and the wires required to connect them.

#### 2.1.1 Fast SRAM Organization and Conventions

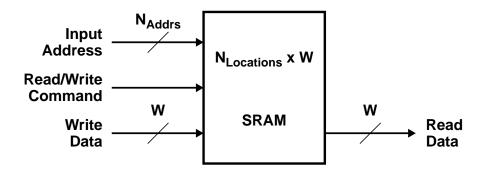

An SRAM presents a simple interface to the system designer. A simplified view of this interface appears in Figure 2-1. An SRAM appears to implement a linear array of  $N_{Locations}$  storage locations, each of which can contain a single W-bit quantity of data (i.e. a *word*). The word is the fundamental unit of data communication between the system and the SRAM, since all bits in a word are read or written simultaneously. This memory is said to be *organized* as  $N_{Locations}$  words by W bits, and has a total memory capacity of  $N_{Bits}$  bits, where  $N_{Bits}$  is simply:

$$N_{Bits} = N_{Locations} W \tag{2-1}$$

The interface features three types of inputs and one type of output. The  $N_{Addrs}$ -bit wide input address field specifies which one of the  $2^{N_{Addrs}}$  (i.e.  $N_{Locations}$ ) memory locations is being accessed. The single-bit command field determines whether the current access reads or writes the selected location. The W-bit write data field supplies the new data that is to be written into the selected location if the command field specifies writing. Finally, the W-bit read data field outputs the contents of the selected memory location during read commands.

Figure 2-1 External SRAM Interface

The internal structure of a static memory is composed largely of memory cells, which each hold one bit of data and thus form the fundamental unit of storage. One can view an SRAM memory cell as a black box with three classes of connections to the outside world, or *ports*:

• Power Ports — These terminals supply constant voltage potentials that the cell uses to maintain its stored value and source and/or sink current when the cell

communicates through its other ports. These ports usually are omitted from block diagrams and schematics because they convey no signalling information and connect every cell together. There are typically two such ports per cell.

- Selection Ports These ports select a given cell to be read and/or written, usually via a change in voltage potential. This thesis consistently draws the physical wires that connect the selection ports of memory cells as horizontal lines and terms them *word lines*; a word line is a wire that selects (at least) one word's width of bits. There is usually one such port per cell.

- Communication Ports Values read from or written to the memory cell pass through the communication ports. This thesis consistently terms the wires that connect these memory cell ports as *bit lines* because they allow the transmission of the stored single-bit values into and out of the cell; bit lines appear as vertical lines in SRAM diagrams. There is typically one communication port per cell, but it often involves a pair of differential bit lines that communicate complementary data values.

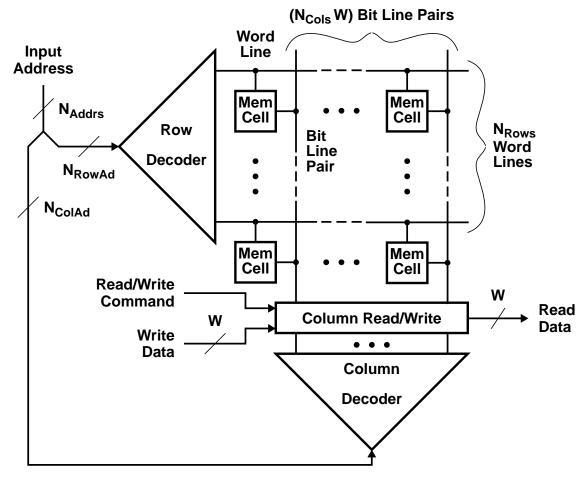

The memory cells are designed to tile into two-dimensional arrays, with the word lines connected to each cell in a row, and the bit lines connected to each cell in a column. While the external organization would suggest a memory array  $N_{Locations}$  words tall by one word wide, physical constraints that arise from the fact that  $N_{Locations}$  is typically many thousand times larger than W require an internal organization with an aspect ratio much closer to unity. As depicted in Figure 2-2, the tall thin logical array may be folded into a nearly square physical array such that a single word line selects multiple words simultaneously.

The blocks outside the memory array convert the address, command, and data values presented by the controlling system into the appropriate word line and bit line signalling required to access the array. In particular, the *row decoder* selects the word line that contains the desired word, while the *column* decoder selects the requested word from among those selected by the word line. By constraining the number of rows per array ( $N_{Rows}$ ) and the number of words per column ( $N_{Cols}$ ) to each be powers of two, the addresses for the row and column decoders are trivially generated by simply routing  $\log_2 N_{Rows}$  bits of the input address to the row decoder, and the remaining  $\log_2 N_{Cols}$  bits to the column decoder. Meanwhile, the command and write data inputs direct the *column read/write* circuitry to either sense the read data from, or write the input data to, the bit lines of the selected word. Both the decode and column read/write circuitry deserve additional mention, since they greatly affect the overall SRAM performance.

Figure 2-2 Internal SRAM Organization

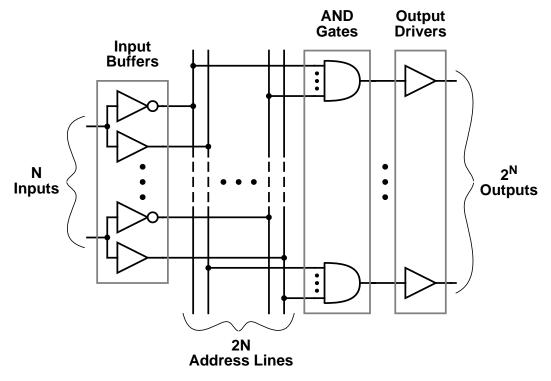

### 2.1.2 Decoders

Decoders perform a logically simple function that turns out to be fairly complicated to implement in a high-performance way. The goal is quite straightforward: given an *N*-bit input address, select whichever of the  $2^N$  output lines is identified by the address. Given true and complemented versions of each address bit, decoding reduces to simply a *N*-input *AND* gate for each output line; the correspondence between output lines and addresses is programmed by choosing which version of each input bit (i.e. true or complemented) to connect to the inputs of each *AND* gate. High-speed decoder design is more complex because as the memory capacity increases, the number of address bits rise so the number of inputs per *AND* gate (i.e. the gate *fan-in*) increases. Since increased *fan-in* gates have higher delay, most large SRAM decoders use multiple stages of *AND* logic that each have lower delay due to reduced *fan-in*. In addition, increasing capacity also increases the number of memory cells affected by each decoder output, which is to say that the gate *fan-out* goes up. Increasing *fan-out* further complicates the design, since the delay of logic gates

increases with *fan-out*. Many SRAMs add additional gain stages to their decoders to quickly drive large loads.

While the decoding structures described later in this chapter, and in Chapter 3, have many differences, they all follow the basic structure of Figure 2-3. The *input buffers* increase the signal strength of the *N* input addresses to drive the capacitance of the decoder gates, while generating (at least) true and complemented versions of each input on the *address line* outputs. For multi-stage decoders, the input buffers typically include the first decoding stage and thus produce *pre-decoded* address lines, where each line represents a logical conjunction of two or more inputs.<sup>1</sup> The address lines select the desired decoder *AND* gate, which in turns selects a *driver* that increases the signal strength to handle the large *fan-out* of the array (for row drivers), or generates control signals for the column read/write circuitry.

Figure 2-3 Basic Decoder Structure

<sup>&</sup>lt;sup>1</sup>The number of bits pre-decoded by each input buffer is often two, because the four wires needed to communicate the four possible states of two bits is no more than what is required to send both true and complement versions of two addresses; beyond three bits of pre-decoding the number of required wires grows rapidly, increasing both the required routing area and the total decoder wiring capacitance.

## 2.1.3 Column Read/Write Circuits

The column read/write circuits also have a simple logical description that is substantially more difficult to implement for large, high-speed SRAMs. On a read access, the column decoder directs the read/write circuits to steer the bit line data from the selected word to the *output buffer*, which drives the read data to the system. The logic that steers one of many inputs to the output is known as a *multiplexer*. As the memory capacity increases, both the number of inputs to each multiplexer and the number of cells on each bit line rise. The increased capacitance is especially difficult on the bit lines, since the read current from a memory cell is typically not high enough to rapidly charge the parasitic capacitance from hundreds or thousands of other memory cells on the same bit line. As a result, fast SRAMs often use low-swing signalling for reading their bit lines; the basic idea is to begin each read with the differential bit lines at the same potential, and then to amplify the difference between the bit lines that develops once the word line selects the memory cell. Unfortunately, the sense amplifier typically requires too much power and physical space to implement with each bit line pair. Thus, the sense amplifiers typically operate on the outputs of the multiplexers. However, this arrangement adds the large capacitance of the multiplexer onto the bit line capacitance, which slows the access. Instead of paying this access penalty, many memories break the multiplexer into stages with reduced capacitance and insert a sense amplifier between the first and second stages; for very large memories the intermediate multiplexer capacitance is often high enough that adopting low-swing signalling between multiplexers (with additional sense amplifiers) provides higher performance.

On a write access, the input write data must be steered to the bit lines of the selected word; because this logic steers one value to one of many places, it is known as *demultiplexing*. While most CMOS SRAMs once used the same bidirectional pass transistors to accomplish both multiplexing and demultiplexing, many fast SRAMs now have parallel paths so that the read path may use smaller swings than the write path and so the memory may begin a write access as soon as a previous read has cleared the bit lines. The write circuits typically get little benefit from low-swing signalling, since the devices that drive the demultiplexer and the bit lines can be much larger than the devices attached to the bit lines, so traditional buffering works quite well.

## 2.1.4 Banks

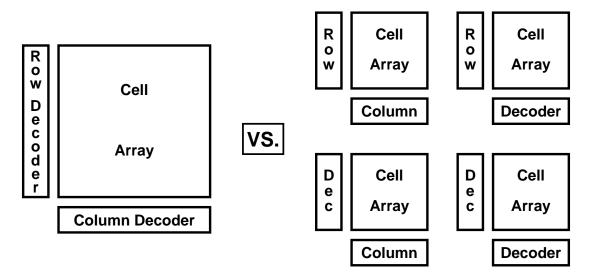

While both decoders and read/write circuits may be modified to maintain certain performance parameters as memory capacity increases, intrinsic problems with the memory array itself eventually begin to reduce the performance. This performance degradation arises from several factors. All the memory cells on the selected word line attempt to charge their bit line capacitance, independent of whether the bit lines are part of the selected word. Thus, very long word lines waste lots of power in charging unselected bit lines. A second factor is the intrinsic delay of the wires that form the word and bit lines; as the arrays grow, so does both the resistance of these wires and the capacitance that loads them. As a result, the distributed wire *RC* delay grows as the square of the array dimensions, which slows the access time. Finally, the number of cells on a bit line begins to slow the access, since there are practical limits to how small a bit line swing may be reliably sensed.

Rather than tolerate the performance limitations of large arrays, SRAM designers avoid these problems by using several smaller arrays (often termed *banks*). For example, Figure 2-4 depicts a large memory array which is then broken into four smaller arrays. The smaller arrays have higher performance because they feature fewer cells per word line and bit line. However, there is a penalty to this approach: the required amount of decoding increases. In the figure, the number of decoder gates doubles, since the number of both word and bit lines doubled when the arrays were split apart. Furthermore, the *fan-in* of the decoders increases. Considering the row decoders in the example, the individual decoder blocks control half as many word lines as those in the large array, which requires one less bit of decoding. However, these decoders also must select between the four banks, since only one word line should be selected at once to reduce the power in unselected cells; this extra decoding requires two additional bits of decoding, so the decoder *AND* gates in the four-bank case each have one more input than those of the single array.

The increased decoding that results from banked SRAM designs limits the memory performance in several ways. The increased decoder *fan-in* slows the access. The increased die area devoted to decoding reduces the memory capacity. Finally, for technologies such as ECL where the basic decoder dissipates static power, the decoding power increases in proportion to the number of decoders. As a result, designing large and fast SRAMs requires complex analysis to determine the appropriate array sizing and organization to maximize performance. The next sections look at these tradeoffs for CMOS, bipolar, and BiCMOS SRAMs.

Figure 2-4 Banked SRAM Organization

## 2.2 CMOS Static Memories

SRAMs implemented in CMOS technologies dominate the marketplace, because CMOS memories offer low power and high capacity solutions. Traditionally, CMOS SRAMs were much slower than the bipolar alternatives, but rapid improvement in CMOS device performance due to technology scaling and innovative circuit design technique shave greatly narrowed the gap. This section describes the design of fast CMOS SRAMs, with an emphasis on understanding the advantages of CMOS technology that will be exploited by the circuits of this thesis.

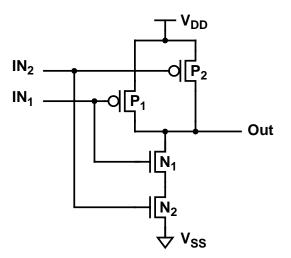

*Complementary* MOS (CMOS) circuit technology takes advantage of the insulating gate terminal and near-zero "off" current of the Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) to implement logic gates that dissipate nearly-zero static power. By utilizing n-channel and p-channel MOSFETs (i.e. NMOS and PMOS transistors), which have opposite threshold voltages, classic CMOS circuits implement switch networks that guarantee that no current paths exist between the power supplies once the inputs transition; the action of the switches connects the output to one of the supplies while isolating the output from the other supply. For example, in the CMOS *NAND* gate of Figure 2-5, the output is high ( $V_{DD}$ ) if either input is high, since one or both of PMOS transistors P1 and P2 are conducting and the output is isolated from the low supply ( $V_{SS}$ ) by at least one of the series-connected NMOS devices. The output is low only if both inputs are low, where the only conducting path is to  $V_{SS}$  via N1 and N2.

Figure 2-5 A CMOS NAND Gate

The output levels of CMOS gates are the two supply voltages  $V_{SS}$  and  $V_{DD}$ , so switching outputs swing the entire supply range. Such large signal swings are the primary source of the increased delay in CMOS circuits versus bipolar ones, since for a fixed device current it requires twice as long to charge a capacitor twice as much voltage. However, the large swings also guarantee that the next stage of logic sees inputs that are close enough to the supplies to turn off one device type, so idle CMOS circuits use no power.

The density advantages of CMOS result in part from its low power dissipation. While competing technologies may also implement millions of components per die, their power consumption levels are too high for the heat-removal capabilities of standard packaging. This is not to say that all CMOS dies are low-power. The advantage of CMOS is that gates only require power when they switch, which is to say when they are accomplishing useful work. Competing technologies where the basic gates require static power are at a disadvantage because in most digital systems, and certainly all SRAMs, most of the circuitry is idle at any given moment. The next subsection introduces the simple circuit that occupies most of the space, while requiring little of the power, of many CMOS and BiCMOS SRAMs: the 6T CMOS memory cell.

## 2.2.1 CMOS Static Memory Cells

The fastest CMOS SRAMs use six-transistor (6T) CMOS static memory cells because the other alternatives have slower cell rise times and thus longer write times. The cell area penalty for the 6T cell is substantial, roughly 50% over the competing cell types, but is still only about  $76\mu m^2$  in a 0.8- $\mu m$  technology, which permits enough capacity for many

applications. Furthermore, because the 6T cell requires only bulk PMOS and NMOS devices, 6T cell-based SRAMs are often implemented on the same integrated circuit as other parts of the system that uses the SRAM, which improves system integration.

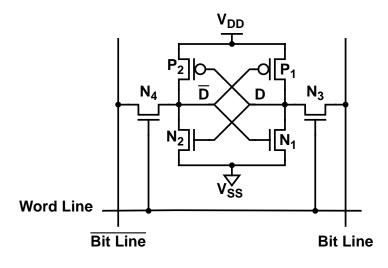

The 6T cell itself is quite simple. Two CMOS inverters with each inverter's output connected to the other inverter's input (*cross-coupled*) create a very stable, nearly zero power latch that is the basis for the memory cell shown in Figure 2-6. The latching operation is very simple: if node D is higher than the switching threshold of the N2-P2 inverter then NMOS device N2 pulls down node  $\overline{D}$ , in turn causing P1 to pull node D higher. This positive feedback action forces  $D = V_{DD}$  and  $\overline{D} = V_{SS}$ , (neglecting any effects of N3 and N4). We say that the memory cell stores one when node D is high and  $\overline{D}$  low. Similarly, if the cell stores zero then D is low and the positive feedback forces  $\overline{D}$  high. The leakage current in such a latch is very small. In common bipolar memories the storage current per memory cell is less than  $10^{-15}$  Amps (1 femtoAmp), so the idle current of a megabit memory array is less than 1 nA. Thus CMOS memory arrays require very little standby power.

Figure 2-6 A 6T CMOS Memory Cell

The latched value is both altered and read through the NMOS access devices N3 and N4. Because PMOS transistors have higher on resistances than NMOS devices of the same size, it is simplest to flip the cell state by overpowering a PMOS device by pulling down its drain with the NMOS access device on the same side. This memory cell is written by raising the word line, often to  $V_{DD}$ , and pulling the bit line down to  $V_{SS}$  on the cell side that needs to be low. For instance, if a cell storing one is to be flipped then node D needs to drop so the bit line driver pulls BitLine to  $V_{SS}$  which causes access transistor N3 to fight P2. N3 easily drops D low enough for P2 to begin turning on and then the latching action will rapidly finish flipping the internal cell nodes.

External circuitry can read the cell by raising the word line without driving either bit line. The cell access transistors then discharge one bit line towards  $V_{SS}$  and charges the other towards  $V_{DD} - V_{Th}$ . The high capacitance of the bit line presents a problem in reading the cell: when the word line first rises, the bit lines do not immediately change so they appear like voltage sources. If a read access begins with a bit line voltage that is too low, the access device will fight its PMOS device and may inadvertently flip the cell on a read access. Since NMOS transistors pull down more strongly than up, it is difficult to overpower an NMOS inverter device with the NMOS access transistor. Thus, higher bit line potentials are much less likely to unintentionally write a cell. The situation is often improved by making N1-N2 have higher drive strength (i.e. larger W/L) than N3-N4, which makes it impossible to disturb the cell value with a high bit line potential. Thus, the column read/write circuits must ensure that the bit lines are at safe (i.e. relatively high) levels before the word line rises to begin a read access.

A 6T CMOS cell can provide very fast read access, since the cell begins pulling on the bit line as soon as the word line rises past  $V_{Th}$ . The issues in making CMOS SRAMs go fast have much more to do with quickly raising the word line, and rapidly sensing the bit lines.

## 2.2.2 Complete CMOS SRAMs

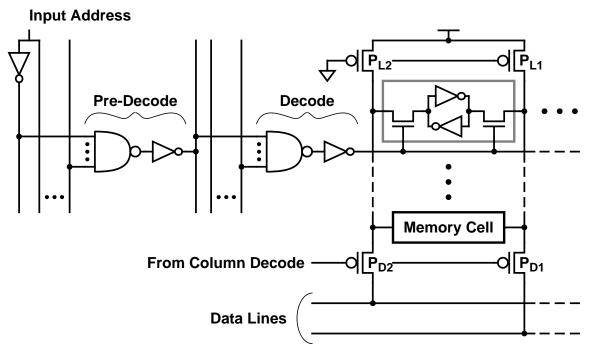

The read access path of current megabit-class CMOS SRAMs have many (twenty or more) address pins and therefore require lots of decoding. As a result, CMOS decoders often utilize three or more stages of decoding to avoid the delay associated with ten-input series MOS transistor gating. For the sake of clarity Figure 2-7 presents a simplified view of a CMOS read path that retains the major circuit types present in fast CMOS SRAMs.

The input buffer generates true and complemented versions of each address bit, which are used to drive pre-decoded address lines. This pre-decoding is typically performed in two or three bit groups by a CMOS *NAND* gate followed by a inverter, with the inverter providing load-driving capability (using large device width) as well as the required logical inversion to implement the pre-decode *AND* function. The pre-decoded address lines are typically heavily loaded because they run the entire height of the row decoder and therefore have substantial wire capacitance along with the loading from the gate capacitance of the row decoders.

Figure 2-7 Simplified CMOS SRAM Read Access Path

Multi-input *NAND* gates also form the row decoder, often using small devices to minimize the loading on the address lines. The row decoder output is complemented and increased in drive capability by one or more inverters to control the heavily-loaded word line and thus access the memory cell.

The column decoder is implemented like the row decoder, and controls the column multiplexer to select which pair of bit lines are connected to the shared *data lines* via PMOS transistors PD1 and PD2. The bit line load transistors PL1 and PL2 are weak PMOS devices that prevent the bit lines from dropping to unsafe levels (where newly-selected cells might be accidentally written) during reads; they are weak enough to be easily overpowered during intentional cell writes. A memory cell on a selected word line and selected bit lines pulls a current  $I_{Read}$  from the bit line on the low side of the cell. This current discharges the bit line capacitance, as well as the connected data line capacitance, until the bit line voltage drops enough that the bit line load will source  $I_{Read}$ . Meanwhile, the bit line load on the complementary bit line charges its data line towards  $V_{DD} - V_{Th}$ . The voltage difference between the data lines is detected by the sense amplifier. The output of the sense amplifier goes to the output buffer, which increases the drive strength of the signal and completes the access.

#### 2.2.3 Reducing CMOS SRAM Delay

The *critical path* through a large SRAM would normally pass through the row decoder, word line driver and then the sense amp; the column decoder has a little more time to accomplish its task, so it normally does not delay the read access. A fast SRAM therefore requires rapid word line decoding and driving, as well as quick bit line sensing.

Minimizing the word line delays requires effectively integrating the logical decode function with the large *fan-out* requirements. Since each row address bit can select every word line, each address bit has a total *fan-out* of the number of word lines times the loading on each word line  $C_{WL}$  divided by the input buffer's input loading  $C_{IB}$ , i.e.

$$fan-out = 2^{N_{Rows}} \frac{C_{WL}}{C_{IB}}$$

(2-2)

The actual *fan-out* is higher because the decode gates utilize series gating, which provides lower output drive per unit of input capacitance than do inverters. CMOS inverter chains provide minimum load driving delays when the number of stages is set so that the *fan-out* per stage is approximately e [9]. This explains why large row decoders for fast SRAMs often use ten or more inverting gates to turn a row address into a word line transition. With so many gates to work with, such decoders typically further reduce delay by distributing the decode function among multiple gates beyond one level of pre-decoding.

A common method to improve the speed of CMOS logic chains is to use synchronous (i.e. *clocked*) design styles, which begin each access in a fixed *reset* state and then conditionally transition to the active state. For fast SRAMs, only one decoder output should ever be selected so the number of transitions in a clocked decoder is fairly small and thus power dissipation does not change much. More importantly, the transistors in the clocked gates may be sized to minimize the delay of the active-going transition, since the reset transition is generated via the clock and is thus independent. For instance, if the NMOS devices in the row decoder's *NAND* gates are increased in width versus the PMOS' width, the *NAND* output will begin falling at a lower input value (and hence earlier in the input's rising transition) and will supply more current and thus discharge its load more rapidly. If the NMOS/PMOS width ratio is increased such that the total input load is constant, then the PMOS width must decrease and thus the rising delay will increase. If a PMOS device is added in parallel with the other PMOS transistors with its gate activated by the reset clock, the rising delay is improved without sacrificing the fast falling delay. CMOS logic gates with extra reset transistors form the basis for designs using *post-charge* logic [10 11] or the similar *self-resetting* circuits [12 13]. In order to let the selection devices be as wide as possible for a given input capacitance, these techniques make the deselection devices too weak to meet the required deselection delay. Instead, additional reset devices are added in parallel to the weak transistor and are activated by a delayed version of the selection signal output from the same gate; in other words, after the gate fires (i.e. switches to a selected state), its own output is fed back to reset the gate after a fixed delay (usually a few inverter delays), or *post-charged*.

The *RC* delay of the word lines is very significant for large CMOS SRAMs, which often have several thousand cells per row. The *divided word line* technique [14] reduces this delay by allocating two word lines for each row. The higher-resistance *global* word line runs the entire length of a row, and connects only to a set of buffers distributed along the row. The buffers drive much shorter *local* word lines that connect to the access transistors of the memory cells. This technique minimizes delay by reducing the capacitance of the long wires. The local word line buffers typically provide an additional level of decoding that ensures that only one local word line is high, and thus that only a subset of the cells on a row are selected.

Decoding the address inputs and driving the word lines takes about half the access time. The remaining delay is spent sensing the stored data and driving the output pins. The primary techniques used to reduce CMOS sensing delays involve extensive use of low voltage swing circuits to minimize the time required to charge the large capacitances present on the shared bit and data lines. The load problem is greatest on the bit lines, where one NMOS access device must move a wire connected to the drain terminal of every other access device on that bit line, as mentioned in Section 2.1.1. In order to minimize the delay, the bit line load devices become much stronger *clamp* devices, only active during reads, that guarantee that the bit line begin an access at very nearly the same potential. The clamp transistors also limit the bit line read swings to minimize the bit line recovery time while ensuring that the sense amplifier has enough differential swing to resolve. Fast SRAMs minimize the delay will reduce as the sense amplifier sensitivity increases. Clocks are often used to activate the clamp devices to rapidly restore the bit line voltages following write cycles.

Because there are often thousands of columns in a SRAM, there is also a delay problem due to the high level of multiplexing required on the shared data lines. In order to reduce this delay, many SRAMs utilize several levels of data lines (and hence multiplexing) with sense amplifiers connecting each level to the next, which allows the SRAM to improve the delay both by reducing the total capacitance in the access path and by reducing the voltage swings along each stage in the path.

The resulting CMOS SRAMs deliver access times that are much closer to those of bipolar SRAMs than is possible using traditional full-swing CMOS circuits [15]. The penalty of low-swing signalling is increased power dissipation, since the increased-sensitivity sense amplifiers use substantially more power than the full-swing circuits that they replace. However, as the next section shows, fast CMOS SRAMs use substantially less power than their bipolar counterparts, primarily due to the lack of static current in the memory cells.

## 2.3 Bipolar Static Memories

This section describes the design of bipolar SRAMs, which have delivered the fastest access and cycle times of any silicon-based technology [16 17 18 19 20]. Bipolar decoding and sense techniques used in these memories are the basis for some of the new techniques presented in this thesis.

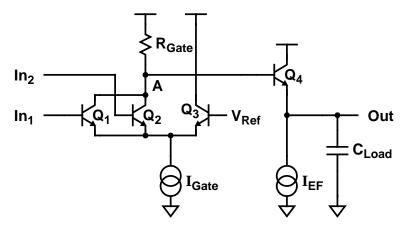

The low-swing ECL bipolar logic circuits that implement the decoders are particularly interesting because they offer much faster switching speeds than CMOS circuits, although they use static current sources that substantially increase their power dissipation. In order to better understand the speed advantage of bipolar circuits, consider the ECL *NOR* gate of Figure 2-8. Bipolar junction transistors (BJTs) transistors Q1, Q2, and Q3 form a simple current switch that performs the desired logical function: the shared current ( $I_{Gate}$ ) is switched into the load resistor ( $R_{Gate}$ ) if either input is higher than the reference ( $V_{Ref}$ ), and  $I_{Gate}$  thus flows through Q3 only if both inputs are below  $V_{Ref}$ . The *emitter follower* formed by Q4 and  $I_{EF}$  isolates  $R_{Gate}$  from the output capacitance ( $C_{Load}$ ), and so the gate delay is dominated by the *RC* term arising from  $R_{Gate}$  times the capacitance at the shared collector node (A). For a fixed  $I_{Gate}$  (i.e. fixed gate power), the *RC* delay is proportional to the gate swing ( $V_{Swing}$ ), since

$$V_{Swing} = I_{Gate} \mathsf{R}_{\mathsf{Gate}} \tag{2-3}$$

Thus, ECL circuits switch faster as  $V_{Swing}$  is reduced. Practical considerations limit the minimum swing to be about 700mV in most ECL systems, which is much smaller than the

3-V to 5-V swings common in CMOS systems. This speed advantage comes at the expense of power dissipation, since  $I_{Gate}$  and  $I_{EF}$  flow continuously, rather than only when the gate is switching.

Figure 2-8 An ECL NOR Gate

The emitter follower supplies a lesser portion of the bipolar speed advantage. The high forward current gain ( $\beta$ ) of the BJT makes the emitter follower an excellent buffer for driving large *fan-out*. While output ringing considerations under high-gain conditions typically limit the  $I_{EF}/I_{Gate}$  ratio at traditional ECL logic swings to around five, this signal strength improvement is achieved without using a level-restoring gate, so the delay is reduced. The emitter follower delay is typically one third that of a level-restoring gate, so emitter followers greatly improve the delay of high *fan-out* structures like decoders.

Besides its use for rapidly driving large loads from relatively low power gates, the emitter follower also provides a key ECL logical function: the outputs of several ECL gates (with emitter follower outputs) may be connected together, resulting in a shared output that is high if any of the gate outputs are high. This interconnection of emitter follower circuits thus performs the logical *OR* function and is called a *wired-or* because the function is performed simply by *wiring* the gate outputs together. The wired-or is better than an *OR* function built with current-switching stages because it is faster (runs at emitter follower rather than current switch speeds) and requires fewer devices.

Because the output of an emitter follower is one  $V_{BE}$  below its input, emitter followers implement a level shift that enables the use of stacked ECL current switches that do not saturate. This thesis labels signals that have been through  $N V_{BE}$  drops as LN. Thus, node A in the Figure 2-8 is L0, while the gate output is L1. A two-level stack of current switches with L1 inputs on the top level would thus require L2 inputs on the bottom level to avoid saturating the BJTs in the bottom stack.

With this background in place, the speed advantages of the bipolar memory cell, with its low-swing word line and high read current will be clear. Unfortunately, the static power dissipation of the cell makes it unsuitable for most high-capacity SRAMs.

### 2.3.1 Bipolar Static Memory Cells

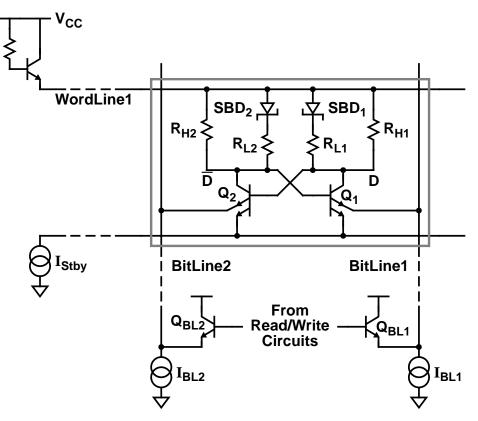

The fastest bipolar SRAMs use the *Schottky Barrier Diode (SBD) load* memory cell [16], which is depicted in Figure 2-9. The SBD load cell stores its data in a latch formed by the multi-emitter transistors Q1 and Q2, and the load resistors  $R_{H1}$  and  $R_{H2}$ . Assuming that both bit line-connected cell emitters conduct no current and that node D is higher than  $\overline{D}$ , most of the current  $I_{Stdby}$  flows through Q2, causing a  $I_{Stdby}R_{H2}$  drop from the word line, WordLine1, to  $\overline{D}$ . Since Q1 conducts almost no current,  $R_{H1}$  supplies only the base current for Q2 and hence D is at about the same potential as WordLine1. Thus the cell latches into a state with a voltage difference between internal cell nodes of about  $I_{Stdby}R_{H}$ , assuming this value is less than the turn-on voltage of the SBD.

Figure 2-9 Schottky Barrier Diode Load Memory Cell

In order to read the cell, the word line driver raises WordLine1 by about 0.8V, which would tend to raise both D and  $\overline{D}$  by the same amount in the absence of the bit line circuits. The external bit line circuits consist of pull-down current sources  $I_{BL1}$  and  $I_{BL2}$ , and common emitter BJTs QBL1 and QBL2 that prevent the off-side cell transistor from turning on during reads. Because the bases of QBL1 and QBL2 are set at roughly the midpoint of the WordLine1 swing, the cell transistor whose base voltage is higher (Q2 in this case) conducts most of  $I_{BL}$  while, on the other bit line,  $\overline{D}$  is lower than the reference and thus QBL1 steers most of the current. In this way BitLine2 charges to one  $V_{BE}$  below WordLine1, while BitLine1 is clamped by QBL1; the bit line voltage difference is readily sensed using a differential pair to finish the read access.

The preceding assumes that the  $I_{BL}$  running through Q2 does not greatly affect D and D; the purpose of the SBDs is to make this true. In order to minimize the power required to keep the cells latched,  $I_{Stdby}$  should be set as low as the following restrictions allow;  $I_{Stdby}$ is typically around 10µA. A small  $I_{Stdby}$  implies a large value for R<sub>H</sub> (tens of kΩ), and if the cell read current  $I_{BL}$  had to flow through R<sub>H</sub> this would limit  $I_{BL}$  to be a small multiple of  $I_{Stdby}$  in order to prevent bipolar saturation in the cell. Because a large value of  $I_{BL}$ (roughly 1 mA) is desired to rapidly move the heavily-loaded bit lines, SBDs are added to the cell in parallel with R<sub>H</sub> to supply the cell read current without much added voltage drop. In other words, the SBDs allow a much larger ratio of  $I_{BL}$  to  $I_{Stdby}$  than would otherwise be possible. SBDs are chosen over junction diodes because they have a lower turn-on voltage than the BJT's  $V_{BE}$ , which prevents the transistor supplying the read current from becoming saturated, and because SBDs require less cell area than junction diodes.

For read to standby current ratios approaching  $\beta$  the base current of Q2 during a cell read is large enough to cause significant drops across its base resistor R<sub>H1</sub>. This tends to decrease the voltage difference between D and D. R<sub>L1</sub> and R<sub>L2</sub> add a resistive component to the SBD load curves that somewhat limits the reduction in voltage margin, but poor matching of component values limit the usefulness of this approach. This decrease in the high cell voltage during reads therefore limits the practically achievable active to standby current ratios, and leads to significant standby power in large bipolar memory arrays.

Peripheral circuits write the cell by raising the word line to its selected value, and pulling current from the cell transistor whose collector node should be low. If that side of the cell already happens to be low then the cell state does not change. However, flipping the cell requires pulling current from the transistor with the low cell potential on its base, so the base of that bit line's clamp device must be lowered so the bit line is free to drop enough to

turn on the cell transistor. Meanwhile, the other clamp device should raise the other bit line so no read current flows through the other cell transistor. For example, to write a cell that stores one to zero, QBL2 raises BitLine2 so Q2 does not supply  $I_{BL}$ , while QBL1 lets BitLine1 drop until Q1 turns on. Once Q1 turns on,  $I_{BL}$  discharges D until it drops below  $\overline{D}$ , at which point  $I_{Stdby}$  switches to Q1 and thus  $\overline{D}$  rises to complete the write.

The read current supported by the SBD load cell is much larger than that of a 6T CMOS cell, and hence provides faster bit line sensing, especially with the excellent voltage sensitivity of bipolar differential amplifiers. Furthermore, rapid cell reads and writes require only low-swing signals, which makes the cell a good match for extremely-fast ECL bipolar decoders.

### 2.3.2 Complete Bipolar SRAMs

The peripheral circuits of a bipolar SRAM require careful design to deliver the fast access permitted by the memory cell. After detailing two options for the decoding function, this section discusses an example implementation of a bipolar SRAM access path.

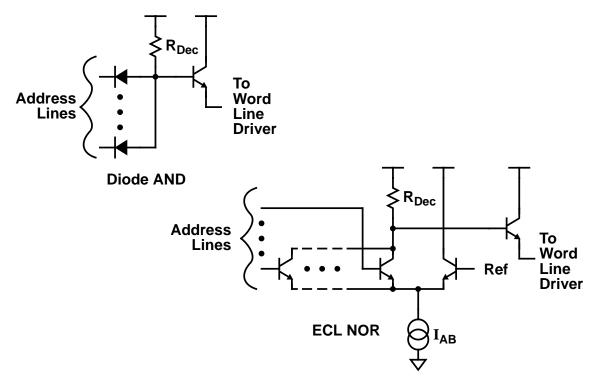

Traditional bipolar decoders fall into two categories based upon the basic decoding gate. Because the logical *AND* function implemented by a decoder would require many-level series stacking to construct from standard ECL structures, bipolar decoders are typically built either from ECL *NOR* gates with complemented inputs or *AND* gates built using diode logic.

The diode *AND* gate that implements the *diode decoder* [21] is shown in Figure 2-10; it implements the *AND* function because the output is low if any of the inputs are low. Like ECL gates, the diode decoder uses a resistor to passively pull the output to the high state and therefore requires static current to keep its output low. Unlike an ECL gate, however, this static current is supplied through the input diodes so the output of a diode decoder begins to change as its inputs change, rather than once the inputs cross a threshold. The diode decoder therefore offers the potential of lower delay than the (ECL gate-based) *NOR* decoder, assuming equivalent input transition times. However, the decoder output swing is determined by the input swing since there is no level-restoring gate.

The figure also shows the ECL *NOR* gate that is the basis of a *NOR* decoder. While it normally requires extra inverters on the inputs of a *NOR* gate to implement the *AND* function, the address lines of a decoder usually have both true and complemented versions of each address, so the input inversion reduces to simple rewiring. Since the *NOR* inputs are active

#### Figure 2-10 Bipolar Decoders

low (i.e. a decoder is selected only if all of its inputs are low), pre-decoding the address lines can be performed by a simple wired-or structure; for instance, the four wired-or conjunctions of two addresses generate only one low (i.e. selected) address line. Simple pre-decoding is the main advantage of *NOR* decoders, although its level-restoring gate structure also allows smaller swings on the heavily-loaded address lines than on the gate outputs. These advantages are balanced by potentially increased delay due to the two level-restoring gain stages of the *NOR* decoder (one each in the input buffer and the *NOR* gate) versus only one for the diode decoder. Furthermore, the *NOR* decoder needs increased power dissipation because it requires separate current to pull down both the address lines and the decoder internal node, while the diode decoder uses the same current for both.

Both decoders provide fast, low-swing outputs, but do this at the expense of substantial power dissipation. Since nearly all decoder outputs must be low, the total decoder gate current ( $I_{Dec}$ ) is roughly

$$I_{Dec} = \frac{N_{Rows} V_{Swing}}{\mathsf{R}_{\mathsf{Dec}}}$$

(2-4)

for each decoder type, where  $V_{Swing}$  is the decoder output swing and  $R_{Dec}$  is the load resistance.  $R_{Dec}$  must be fairly low for fast access, so the decoding power is often the second largest component of bipolar SRAM power dissipation after the memory cells. Chapter 3 introduces techniques that greatly improve the power dissipation of low-swing decoders.

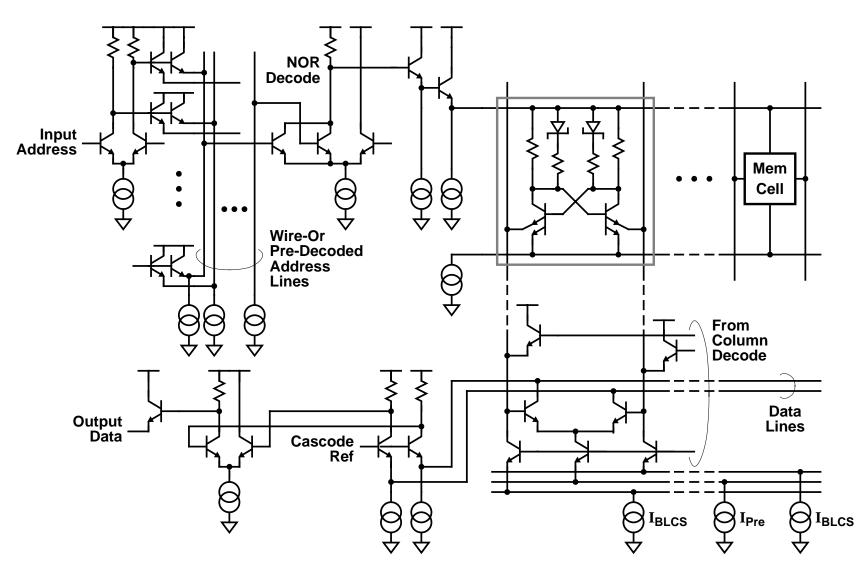

Figure 2-11 depicts the read access path of a typical high-speed bipolar SRAM, consisting of input buffers with pre-decoded outputs, *NOR* decoders, Darlington word line drivers, SBD load memory cells, bit line decoders and pre-amplifiers, cascode sense amplifiers, and output buffers. A brief description of each circuit follows.

Each input buffer consists of an ECL inverter with complementary outputs connected to pre-decoded wired-or address lines. This wired-or structure produces very fast predecoded outputs, since the delay is increased only by the extra parasitic capacitance of the second emitter of each emitter follower on the inverter. Many technologies allow sharing of the collector and base regions of the followers to minimize this capacitance.

The pre-decoded address lines drive the ECL *NOR* decoder gates. Pre-decoding makes these decoders faster because of reduced base-collector and collector-substrate capacitance on the decoder output node. A decoder output controls a pair of cascaded emitter followers that drives a word line across the memory cell array. Such a connection of emitter followers is often called a *Darlington* pair and is capable of rapidly driving large capacitances because the effective current gains of each stage are multiplied. The pull-down current source in the middle of the Darlington helps speed the falling transition, which is otherwise discharged only by the base current of the second BJT.

The stored data values for memory cells on the selected word line are sampled only if the cell is also connected to a selected bit line pair. The column decoder selects a pair of bit lines by steering  $I_{BLCS}$  into both bit lines and  $I_{Pre}$  into their differential pair. Meanwhile, both bit line clamp devices are set to a base potential midway in the word line swing. As described in Section 2.3.1, a voltage difference develops on the bit lines due to the cell state; this difference causes the *pre-amplifier*, (i.e. the differential pair), to pull different currents from the data lines, which are shared with the other unselected columns. The sensed currents may be turned back into voltages with a resistor, but the large loading on the data lines (due to potentially very many unselected pre-amplifiers) would give a large delay if the resistors were attached directly to the data lines.

BJTs with reference voltages on their bases and inputs at their emitters, in what is known as a *cascode* configuration [22], provide large output current differences with very low input swings (60mV per decade of current). Since the data line delay is roughly  $C_{DL}V_{Swing}/I_{Pre}$ , the cascode sense amplifier greatly reduces the data line voltage swings and thereby minimizes the data line delay, while providing a lower-capacitance output node that has greatly-reduced *RC* delay. The differential output of the sense amplifier then goes through emitter followers to a final ECL output buffer, which restores the read data to normal ECL voltage levels and, when the data must be driven off-chip, increases the drive strength of the signal to rapidly drive a 50- $\Omega$  transmission line.

Bipolar SRAMs deliver very fast access due to their low-swing signalling and the excellent voltage sensitivity and current drive capabilities of bipolar transistors. However, the static power dissipated by the memory cell and the peripheral circuits prevents the use of this technology for most large memories. BiCMOS SRAMs, which are the subject of the next section, offer the opportunity to combine the best of CMOS and bipolar SRAMs to come up with superior solutions.

## 2.4 BiCMOS Static Memories

By incorporating NMOS, PMOS and NPN BJT devices on the same integrated circuit, BiCMOS process technology offers the promise of hybrid SRAM solutions that combine the low power and high capacity characteristics of CMOS with the fast access and cycle times of bipolar memories. While existing **BiCMOS** SRAMs achieve speed/power/capacity combinations that neither CMOS nor bipolar designs can match, BiCMOS designs do not deliver bipolar speeds at CMOS power levels. Existing BiCMOS memories bridge the gap between CMOS and bipolar to deliver intermediate speed at [3 23 24 25 26 27 28 29 30 31 32 33 34 35 36]. intermediate power After describing two basic BiCMOS design styles, as well as the interfacing problem, the section details the brief history of fast BiCMOS static memories.

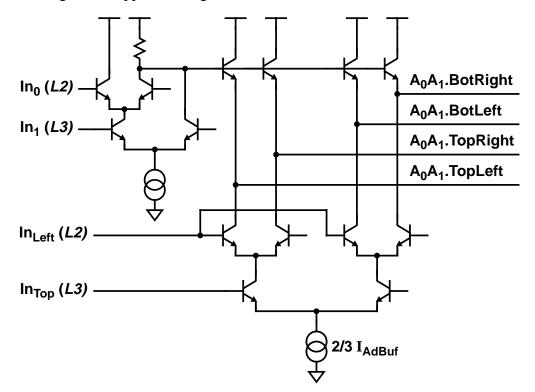

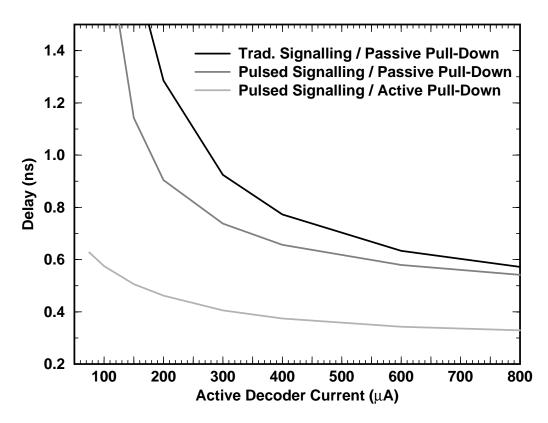

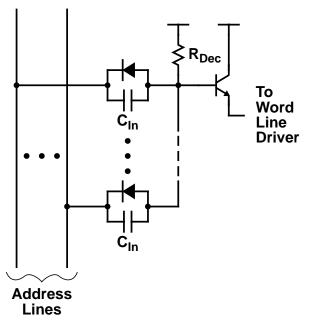

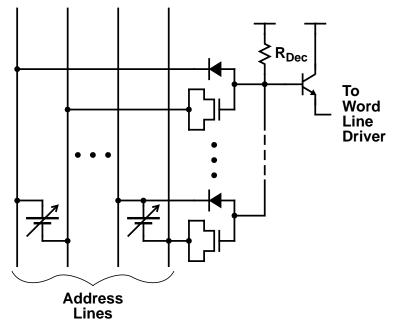

## 2.4.1 BiCMOS Design Styles