# **INFORMATION TO USERS**

The most advanced technology has been used to photograph and reproduce this manuscript from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book. These are also available as one exposure on a standard 35mm slide or as a  $17" \ge 23"$  black and white photographic print for an additional charge.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

University Microfilms International A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 313/761-4700 800/521-0600

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

Order Number 8912882

**Incremental VLSI compaction**

•

Carpenter, Clyde William, Ph.D. Stanford University, 1989

Copyright ©1989 by Carpenter, Clyde William. All rights reserved.

# **INCREMENTAL VLSI COMPACTION**

A DISSERTATION SUBMITTED TO THE DEPARTMENT OF COMPUTER SCIENCE AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

> By Clyde W. Carpenter November 1988

© Copyright by Clyde W. Carpenter 1989

• •

All Rights Reserved

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

ü

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy.

Mark A

(Principal Adviser)

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy.

Im M John I

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy.

Jeffrey D. Ullman

Approved for the University Committee on Graduate Studies:

Dean of Graduate Studies

üi

### **INCREMENTAL VLSI COMPACTION**

Clyde W. Carpenter, Ph.D. Stanford University, 1989

### Abstract

VLSI compaction is the translation from a high level description of a circuit down to the detailed layout needed for fabrication. A compactor tries to make as compact a layout as possible without violating any design rules. An incremental compactor allows one to edit a schematic or change layout constraints and quickly see the effects of the change.

An incremental compactor has to incrementally generate and solve the constraints needed to enforce the design rules. This dissertation presents an algorithm that uses adjacency lists to generate and incrementally update a minimal complete set of the spacing constraints needed to keep adjacent tiles in a layout from interfering with each other. The base algorithm creates clockwise threaded lists of non-overlapping, fixed-size tiles. The algorithm is complicated by the need to handle wires, overlapping tiles, and various different spacing rules. In near linear time it generates an average of 1.2 spacing constraints per tile. The adjacency lists allow fast, efficient updates when tiles are moved, deleted, or inserted.

This dissertation also presents three algorithms to solve the constraints once they are generated. In addition to minimizing area, these algorithms also minimize the total wire length. One of them calculates the sum of the wire-pull weights on each subtree of a directed spanning tree of active constraints to decide which subtrees need to be moved. This weighted tree provides enough information to make incremental changes in time proportional to the size of the change instead of to the size of the circuit. Wirelength minimization improves the layout but gives compaction a slightly worse than linear expected time.

# Acknowledgements

This material is based upon work supported under a National Science Foundation Graduate Fellowship. This work was supported in part by the National Science Foundation under Grant DMC8451822 and in part by the Defense Advanced Research Projects Agency under contracts MDA903-83-C-0335 and N00014-87-K-0828.

# **Table of Contents**

| Abstract                         | iv |

|----------------------------------|----|

| 1. Introduction                  | 1  |

| 1.1. Background                  | 3  |

| 1.2. Generating Constraints      | 4  |

| 1.3. Solving Constraints         | 8  |

| 2. Generating Constraints        | 11 |

| 2.1. Adjacency Lists             | 11 |

| 2.2. Single Color Case           | 13 |

| 2.2.1. Growing Tiles             | 14 |

| 2.2.2. Shrinking Tiles           | 16 |

| 2.2.3. Changing Tiles            | 17 |

| 2.3. Wires                       | 18 |

| 2.4. Overlapping Tiles           | 20 |

| 2.4.1. General Case              | 21 |

| 2.4.2. Restricted Case           | 23 |

| 2.5. Multiple Colors             | 24 |

| 2.5.1. Fuzzy Edges               | 26 |

| 2.5.2. Growing Tiles             | 27 |

| 2.5.3. Shrinking Tiles           | 29 |

| 2.5.4. Summary                   | 31 |

| 2.6. Quick Loading               | 31 |

| 2.7. Complexities                | 33 |

| 2.8. Summary                     | 36 |

| 3. Solving Constraints           | 38 |

| 3.1. Simple Compaction           | 38 |

| 3.1.1. Incremental Compaction    | 40 |

| 3.1.2. Summary                   | 42 |

| 3.2. Wire-Length Minimization    | 43 |

| 3.2.1. Balance Algorithm         | 45 |

| 3.2.2. Slack Algorithm           | 48 |

| 3.2.3. Balance and Slack Timings | 50 |

| 3.3. Tree Compaction             | 51 |

| 3.3.1. Simplex Algorithm         | 51 |

| 3.3.2. Tree Weight Algorithm     | 53 |

| 3.3.3. Incremental Compaction    | 55 |

| 3.4. Summary                     | 57 |

| 4. Implementation             | 59  |

|-------------------------------|-----|

| 4.1. Tcmp                     | 59  |

| 4.2. Technology File          | 60  |

| 4.3. Tile Data Structure      | 63  |

| 4.4. Compaction               | 64  |

| 4.4.1. Incremental Compaction | 68  |

| 4.5. Results                  | 70  |

| 4.5.1. Translations           | 74  |

| 4.5.2. Adjacency Lists        | 75  |

| 4.5.3. Compaction             | 79  |

| 4.6. Summary                  | 83  |

| 5. Conclusions                | 85  |

| 5.1. Future Work              | 87  |

| Appendix A. Semi-Merged Tiles | 88  |

| A.1. Growing and Shrinking    | 89  |

| A.2. Quick Load               | 91  |

| Appendix B. Adjacency Lists   | 94  |

| B.1. Top Edge Up              | 94  |

| B.2. Bottom Edge Up           | 96  |

| B.3. Quick Load               | 97  |

| Appendix C. Examples          | 98  |

| References                    | 104 |

# **List of Figures**

| Figure 1-1 RAM Cell Stick Diagram and Layout                  | 1  |

|---------------------------------------------------------------|----|

| Figure 1-2 Constraints: Alignment, Wire, Spacing              | 5  |

| Figure 1-3 A Every Pair B. Sorted Every Pair                  | 5  |

| Figure 1-4 A. Shadowing B. Scan Line                          | 7  |

| Figure 1-5 Corner Stitching: Tile Addition                    | 8  |

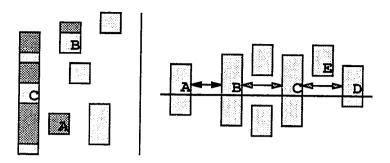

| Figure 2-1 A. Adjacencies B. Visibilities                     | 11 |

| Figure 2-2 A. Adjacency Pointers B. Non-Nil-Ended List        | 12 |

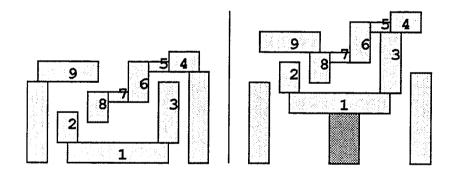

| Figure 2-3 Concave Left Turnaround                            | 13 |

| Figure 2-4 Before and After Breaking a Left List              | 14 |

| Figure 2-5 Before and After Breaking a Right List             | 15 |

| Figure 2-6 Before and After Growing a Tile                    | 15 |

| Figure 2-7 Final Search for Top Adjacencies                   | 16 |

| Figure 2-8 Before and After Shrinking a Tile                  | 16 |

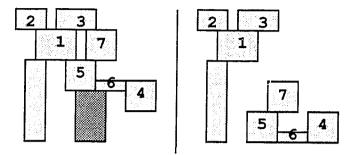

| Figure 2-9 Locating Where to Insert a Tile                    | 18 |

| Figure 2-10 Wire Adjacencies                                  | 19 |

| Figure 2-11 Constraints With Pass-Throughs                    | 21 |

| Figure 2-12 Fixing Negative Length Wires                      | 21 |

| Figure 2-13 A. Insert on Left or Right? B. Cannot Insert Wire | 22 |

| Figure 2-14 Constraints Without Pass-Throughs                 | 23 |

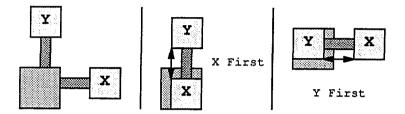

| Figure 2-15 Compaction-Order Effects on Overlap               | 24 |

| Figure 2-16 A. Spacing and B. Overlap Bleed-Throughs          | 25 |

| Figure 2-17 A. Locate Off By Bloat B. Shrink Slip Through     | 26 |

| Figure 2-18 A. Crossed Constraints B. Up Pointer Conflict     | 27 |

| Figure 2-19 A Complex Around-the-Corner Search                | 28 |

| Figure 2-20 Five-Color Rule                                   | 28 |

| Figure 2-21 Temporarily Cached Missing Constraint             | 29 |

| Figure 2-22 Temporary Extra Adjacency                         | 30 |

| Figure 2-23 Shrink Shadow: Skip Tiles C and D                 | 31 |

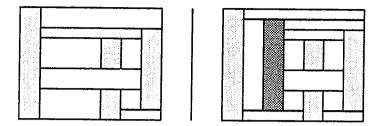

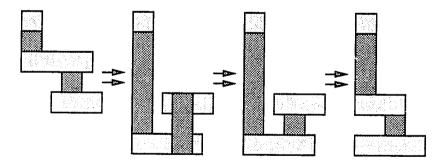

| Figure 2-24 Quick Load Steps: Locate, Swap, Search            | 32 |

| Figure 2-25 Final Searches for Three Tiles                    | 34 |

| Figure 2-26 Visible Turnaround Range                          | 34 |

| Figure 2-27 Grow and Shrink Worst Cases                       | 36 |

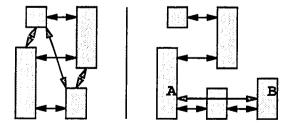

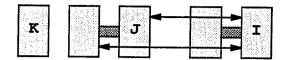

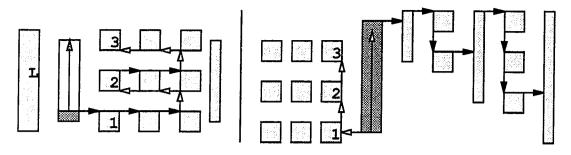

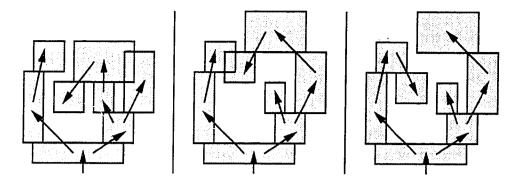

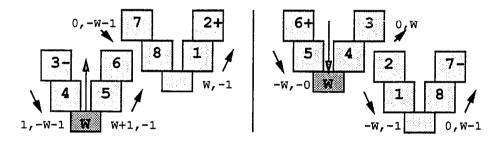

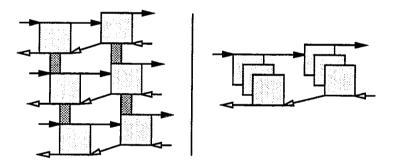

| Figure 3-1 Group Deletion Movement Order                      | 41 |

| Figure 3-2 Tile Insertion Movement Order                      | 41 |

| Figure 3-3 Tile Deletion Movement Order                       | 42 |

| Figure 3-4 A. Flow and B. Weight Analogies                    | 43 |

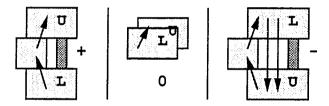

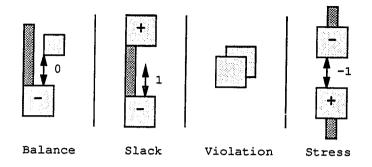

| Figure 3-5 Possible Wire Lengths and Stresses                 | 44 |

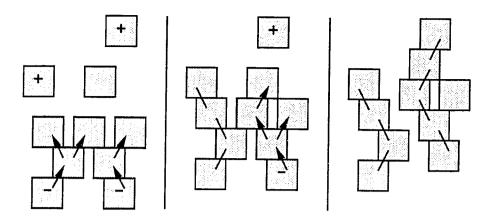

| Figure 3-6 Four Minimization Algorithm Types                  | 45 |

| Figure 3-7 Two Balance Algorithm Tile Movements               | 46 |

|                                                               |    |

| Figure 3-8 Stress Reduction: Three Added Stress Paths               | 46  |

|---------------------------------------------------------------------|-----|

| Figure 3-9 $O(m^2)$ Repeated Verses 2 <i>m</i> Total Tile Movements | 47  |

| Figure 3-10 Two Slack Algorithm Tile Movements                      | 49  |

| Figure 3-11 Two Simplex Constraint Violation Fixes                  | 52  |

| Figure 3-12 Two Tree Weight Negative Subtree Movements              | 53  |

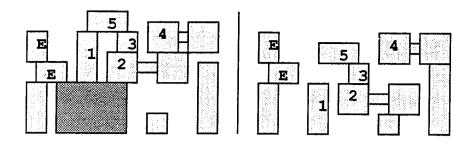

| Figure 3-13 Two Subtrees Orphaned by a Tile Deletion                | 55  |

| Figure 3-14 Two Movements Caused by a Tile Insertion                | 56  |

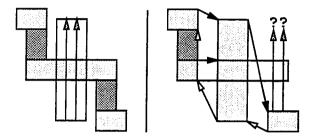

| Figure 3-15 Three X-Y Steps from One Change                         | 57  |

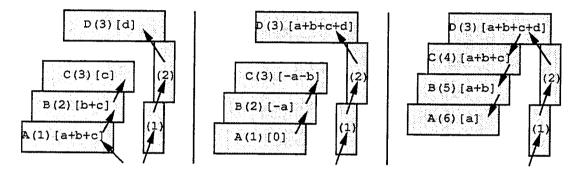

| Figure 4-1 Graft Effects on (Height) and [Weight]                   | 67  |

| Figure 4-2 Cuts: Negative and Positive Fragments                    | 68  |

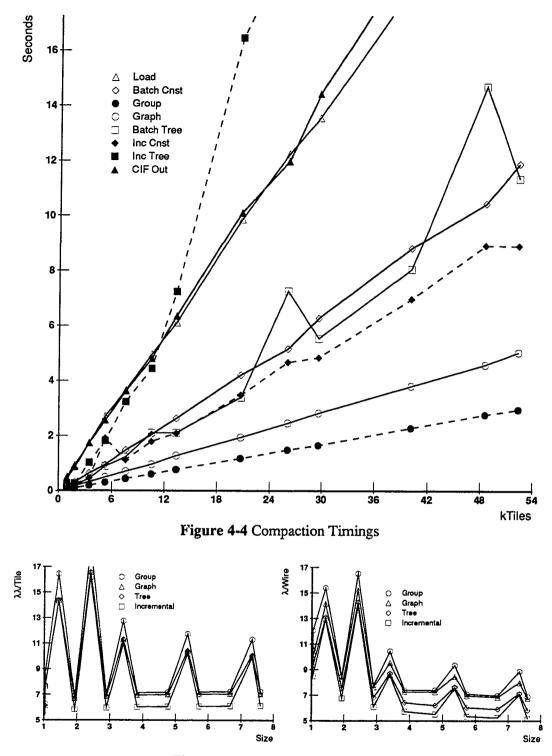

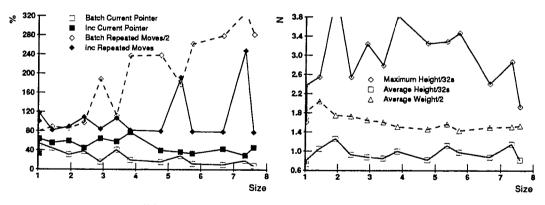

| Figure 4-3 Benchmark Results                                        | 71  |

| Figure 4-4 Compaction Timings                                       | 73  |

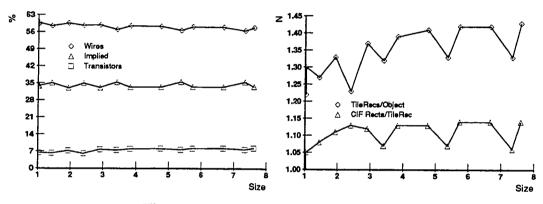

| Figure 4-5 Area and Wire Lengths                                    | 73  |

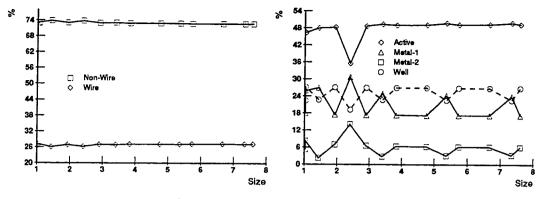

| Figure 4-6 Object Types and Translations                            | 74  |

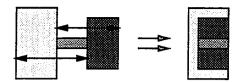

| Figure 4-7 Tile Types and Planes                                    | 75  |

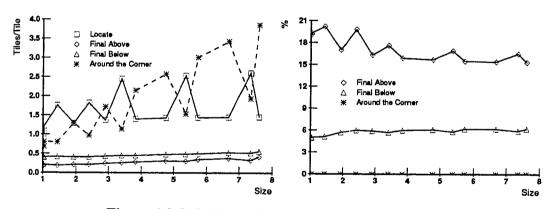

| Figure 4-8 Quick Load Search Distances and Successes                | 75  |

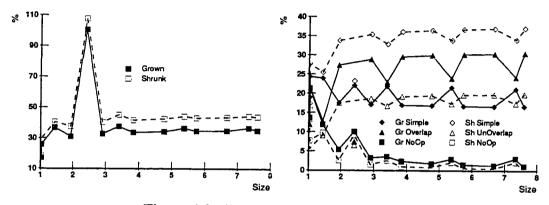

| Figure 4-9 Tiles Grown/Shrunk and Types                             | 76  |

| Figure 4-10 Grow/Shrink Stats and Semi-Merges                       | 77  |

| Figure 4-11 Grow/Shrink Search Distances and Successes              | 77  |

| Figure 4-12 Shrink Skip Reasons and Adjacencies                     | 78  |

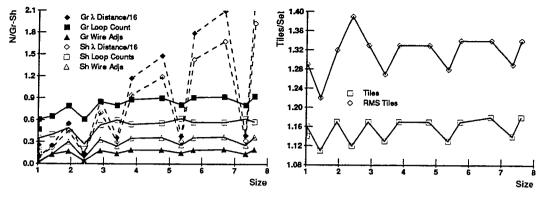

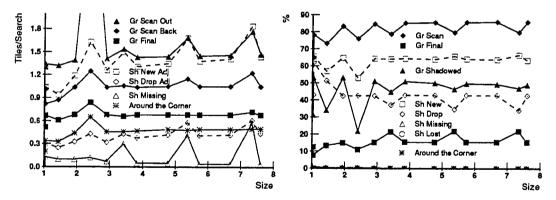

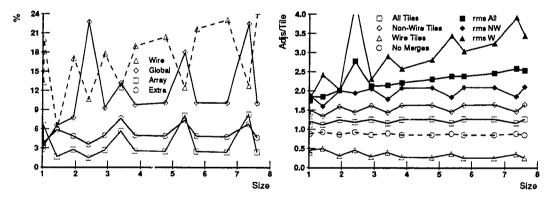

| Figure 4-13 Group and Graph Constraints                             | 80  |

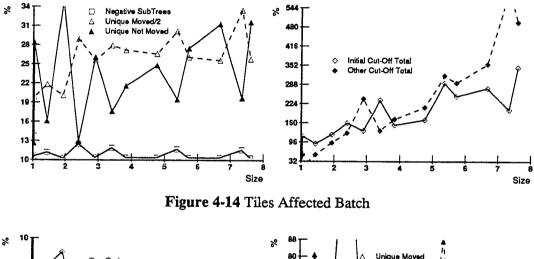

| Figure 4-14 Tiles Affected Batch                                    | 80  |

| Figure 4-15 Tiles Affected Incremental                              | 80  |

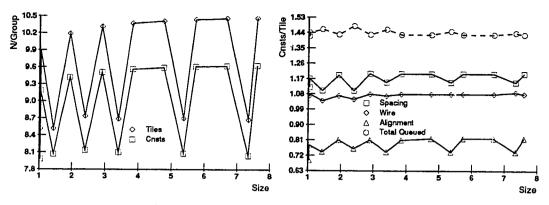

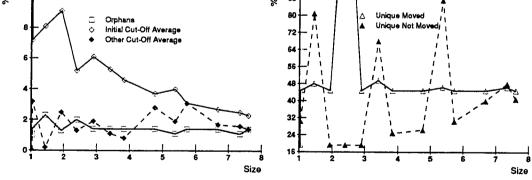

| Figure 4-16 Batch and Incremental Stats                             | 81  |

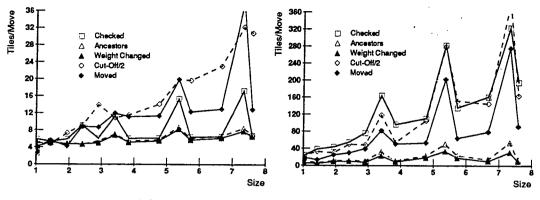

| Figure 4-17 Batch and Incremental Moves                             | 82  |

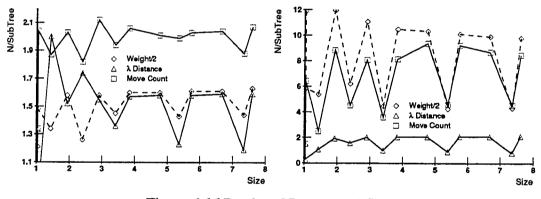

| Figure 4-18 Tree Queue Effects and Stats                            | 82  |

| Figure A-1 Semi-Merging Tiles                                       | 88  |

| Figure A-2 Tile L's Four Right Adjacencies                          | 89  |

| Figure A-3 Vanishing Corners: 8 to 4                                | 90  |

| Figure A-4 Violated Over-Restrictive Adjacencies                    | 91  |

| Figure A-5 A. Proper Load Order B. Shadowed Endpoints               | 92  |

| Figure A-6 Four Double Merge Cases                                  | 92  |

| Figure B-1 Four L and U Nil/Non-Nil Cases                           | 94  |

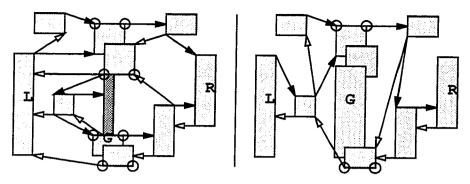

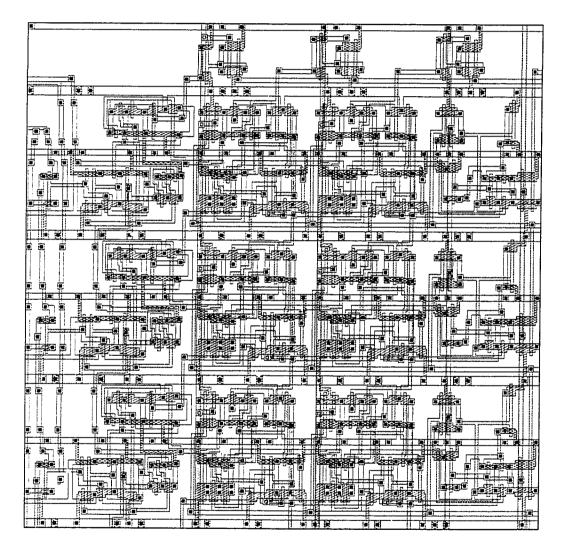

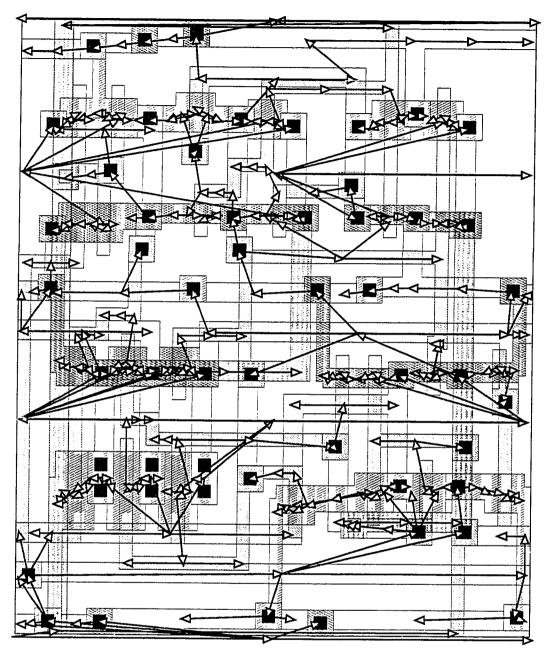

| Figure C-1 4x4 Multiplier: 344x336λ, 10.5k                          | 98  |

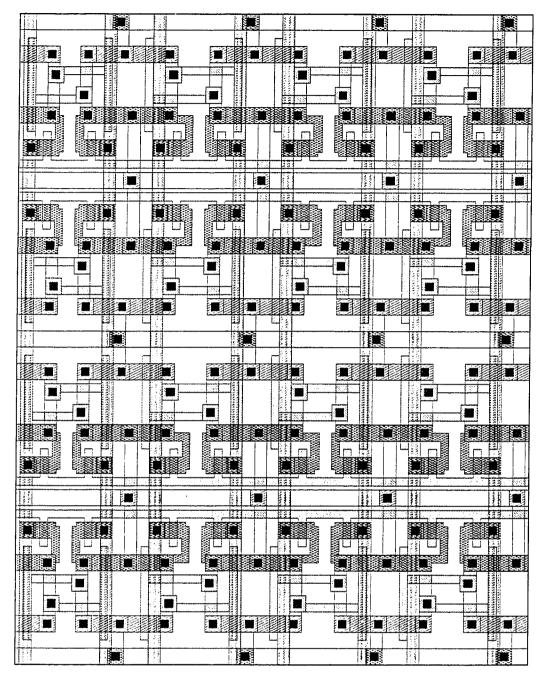

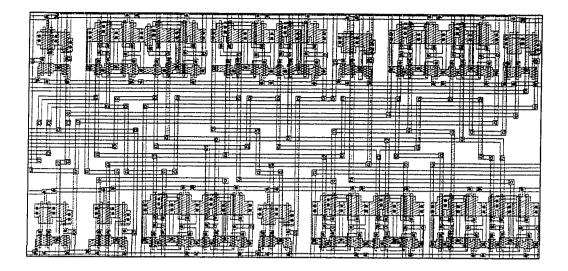

| Figure C-2 4x4 Ram: 127x160λ, 3.5k                                  | 99  |

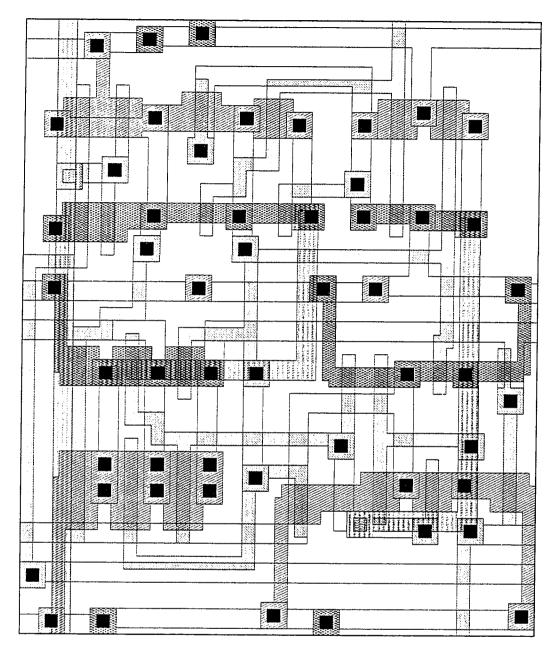

| Figure C-3 Full Adder (afavg): 79x94λ, 1k                           | 100 |

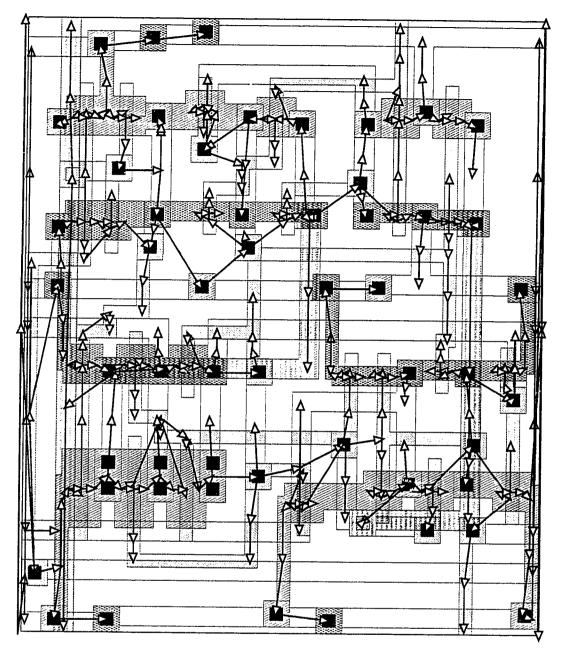

| Figure C-4 Adder with Left-Right Spanning Tree                      | 101 |

| Figure C-5 Adder with Up-Down Spanning Tree                         | 102 |

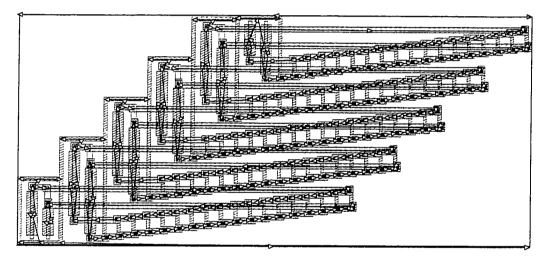

| Figure C-6 Routing (C132): 426x201λ, 5.3k                           | 103 |

| Figure C-7 O( $n^2$ ) Worst Case Compaction                         | 103 |

|                                                                     |     |

# Chapter 1 Introduction

One of the most tedious parts of designing full custom integrated circuits is laying out the artwork needed to fabricate the circuit. The detailed layout has to specify the exact location and size of all the objects required by the fabrication technology to create the desired circuit. VLSI (Very Large Scale Integration) technology has allowed the creation of more and more complex circuits and made layout more and more time consuming. One way to handle this increased complexity is to design circuits at a more abstract level and then automatically translate the designs down to the detailed layout.

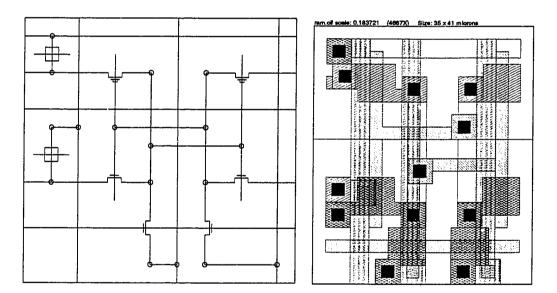

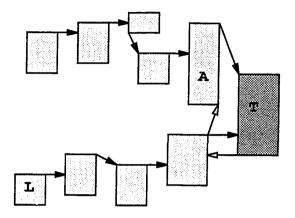

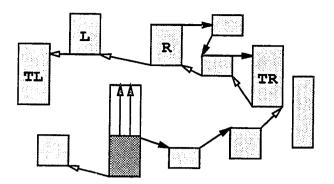

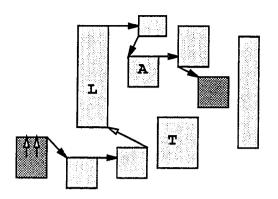

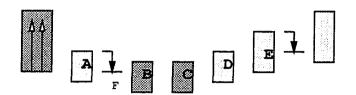

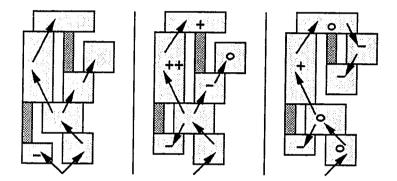

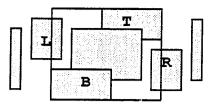

Figure 1-1 RAM Cell Stick Diagram and Layout

Working at a slightly more abstract level allows designers to worry about the relative placement of transistors and wires instead of how to form transistors and how far apart the technology requires things to be spaced. The compaction program takes care of these technology-dependent design rules. An abstract diagram consisting of symbolic transistors wired together with dimensionless wires is called a stick diagram. A stick diagram is much easier to understand and modify than the resulting layout.

Introduction

Figure 1-1 shows a stick diagram for a six-transistor CMOS static RAM cell and its 250-tile layout. When displayed on a color monitor, the wires are colored to show in which layout layer they run. The stick diagram was converted to a layout by a two-step batch process. First, the compactor created a set of layout-level tiles and generated constraints between the tiles to enforce the design rules. Then it solved the constraints and produced the actual layout.

We want layouts to be as small as possible since smaller layouts are cheaper to manufacture and are generally higher performance. Because of the difficulty of true, two-dimensional area compaction, most compactors instead separately minimize the width and height of a layout. A major problem with these one-dimensional compactors is the lack of control over the interaction between the two dimensions. In batch compaction, if designers do not like a compacted layout or have to change the circuit, they change the circuit description and run everything again in the hope of a better layout. Besides taking a great deal of time, this process often makes it difficult or even impossible to achieve the desired improvement. This dissertation describes algorithms for building an incremental compactor. In incremental compaction, enough information is saved to allow the layout to be quickly updated to reflect changes. For example, when the corners of two tiles catch on each other during a compaction, the designer can simply nudge one of them to break the interlock and produce a better compaction. In batch compaction, the designer can at best rearrange the stick diagram to try to avoid the interlock without creating other, worse problems.

This dissertation is divided into two main parts corresponding to the two main tasks in an incremental compactor: generating and solving the constraints. After giving a brief history of compaction, we describe how adjacency lists can be used to quickly generate and incrementally update a minimal complete set of the spacing constraints needed to keep adjacent tiles in a layout from interfering with each other. These constraints are difficult to handle because they depend on the current tile positions and thus change during compaction. We first describe the adjacency lists algorithm for the simple single-color case and then discuss the enhancements added to handle wires, overlapping tiles, and multiple colors.

The second part of this dissertation describes methods of solving the constraints once we have them. After discussing efficient non-wire-length minimization algorithms, we describe four wire-length minimization algorithms based on the four solution conditions of our weight analogy version of the min-cost max-flow problem.

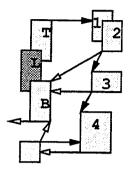

2

Minimizing the total wire length is difficult because a tile's placement depends on the total weight of the set of tiles pressing against it, which changes as the tiles move. The first two algorithms work well for batch compaction but do not save enough information to allow incremental updates. The final algorithm, the tree weight algorithm, maintains a directed spanning tree of active constraints. By calculating and storing with each tile the sum of the wire-pull weights on the subtree above it, the algorithm can easily determine which subtrees need to be moved.

After describing these two main tasks, this dissertation ends by giving some implementation details and timings and statistics for a running test compactor. This includes a description of the interaction between the adjacency lists and tree weight algorithms and more detail about the tree operations used by the tree weight algorithm. The tree compactor's performance is compared with several other compactors' on a set of benchmark circuits. It produces better layouts very quickly without using too much memory.

## 1.1. Background

The earliest computer-aided layout systems were simple drafting programs: layouts were created by digitizing a hand-drawn layout. While this was all right for small circuits, it became tedious as circuits got larger and more complex. One had to worry about creating objects and spacing them far enough apart to not interfere with each other but close enough together to not waste valuable chip area. To make the creation of well-formed objects easier and faster, macros that allowed one-step placement of multiple-tile objects were added to the editors. Batch design-rule checkers were created to check layouts for accidental design-rule violations [Baird 77]. Only recently has this checking been merged with the editors to allow mistakes to be fixed before they propagate too far [Taylor 84].

Even with simple macros and design rule checkers, designers were still responsible for creating artwork without errors and had to be very careful about the space between objects. To try to simplify and speed up the design process, design systems working at a more abstract level were created. Tiles were replaced by symbolic objects; instead of using a macro to place tiles, one just placed a symbolic object on a coarse grid. Williams coined the term sticks [Williams 78] and proposed that compaction should translate a stick diagram, a sketch of the circuit, into a layout. Placing objects on a coarse grid freed the designer from worrying about all the detailed spacing rules. The

#### Introduction

first translation systems simply spaced the grid lines using a constant spacing calculated to prevent any possible design-rule violations [Gibson 76]. This wasted a lot of space.

One method to reduce this waste entailed using the shear line algorithm [Akers 70] to post-process the layout. Starting with a layout, a smaller layout was produced by repeatedly compacting along compression ridges. Found by an expensive search and backtrack algorithm, a compression ridge consists of a group of strips of unused space running from one side of the layout to the other. Removing this excess space causes the halves of the layout on either side of the ridge to slide together along shear lines perpendicular to the ridge. The repeated empty-space searches were too slow to be practical [Dunlop 78]. A method that kept track of local information from previous searches was used to speed up the process [Dunlop 80] but did not help much.

Virtual grid systems [Weste 81] used a much faster but less fiexible method to reduce the wasted space. They improved the fixed grid method by allowing the grid spacings to vary depending on the objects actually present on each grid line; the largest constraint between two nearby grid lines determined their spacing. The spacing constraints were easy to find since most of them occured between tiles on neighboring grid points. The major problem with these systems was that they linked together groups of tiles that were only related by being on the same grid line and thus unnecessarily increased the layout sizes. Later virtual grid systems [Nyland 87] [Bcyer 87a] made trade-offs between allowing more freedom of movement within each virtual grid line and searching for the needed spacing constraints.

More flexible systems [Cho 77] ignored the grid lines completely and instead created a graph of the constraints needed to properly space neighboring objects. The graph was then solved to produce a legal layout. In the next section we discuss the history of generating constraints and in the subsequent section we discuss the history of solving them.

### **1.2. Generating Constraints**

Compaction algorithms operate on the constraints needed to enforce the layout design rules. The stick object definitions prevent ill-formed objects. Therefore a compactor does not have to worry about rules such as poly overlaps of transistors and minimum sizes. Alignment rules tie together the parts of an object and force them to move as a unit. Examples are alignments between a transistor's source, gate, and drain

4

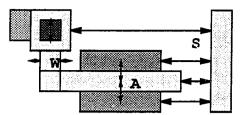

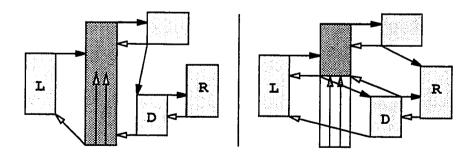

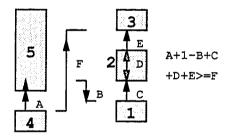

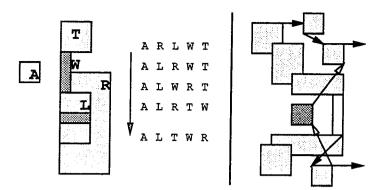

Figure 1-2 Constraints: Alignment, Wire, Spacing

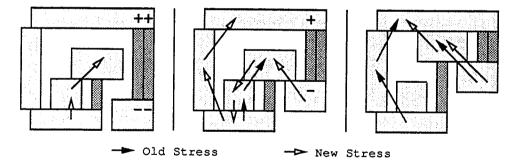

regions (constraints A in Figure 1-2), or between a contact's layers. Wire rules keep wires fully connected to their endpoints, but they also allow wires to slide on wide endpoints. Each wire-endpoint needs one constraint to keep the endpoint's left edge at or to the left of its vertical wire's left edge and another to keep its right edge at or to the right of the wire's right edge (constraints W in Figure 1-2). Finally, the spacing rules provide the margins needed in the fabrication to keep adjacent objects from interfering with each other (constraints S in Figure 1-2). The alignment and wire constraints are easy to handle: they are generated from the circuit description and are invariant during compaction. The spacing constraints are more difficult because they depend on the current x and y positions of the layout tiles.

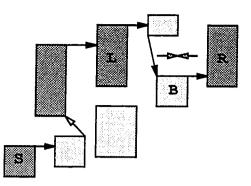

Many algorithms have been used to generate the spacing constraints. The simplest method is to check for interactions between every pair of tiles. The distance between two tiles is taken to be the maximum of the x and y distances between their edges. Thus an x-direction constraint is needed between two tiles only if the tiles are separated by less than the minimum legal spacing in the y-direction. This algorithm is easy to code but has the drawback that although each comparison is quick,  $n^2$  comparisons are required for an *n*-tile layout. In Figure 1-3A, half the tests produce constraints (the dark arrows).

Figure 1-3 A. Every Pair B. Sorted Every Pair

Introduction

The number of comparisons can be reduced by first sorting the tiles by their bottom coordinates (to generate x constraints). Then each tile can be compared with just the tiles in the horizontal band above it. This gives  $O(n^{1.5})$  total comparisons for a roughly square layout [Eichenberger 86]. Besides requiring many comparisons, these two algorithms have another drawback: for normal layouts they produce  $O(n^{1.5})$  constraints when, because of transitivity, only O(n) constraints are needed. In Figure 1-3B, the constraint between tiles A and B is unnecessary because of their constraints with the tile between them.

Another way to reduce the number of comparisons and generated constraints is to use intervening groups. Tiles that are rigidly held together are grouped into features. As all the pairs of features are compared, an approximation of the longest path between every pair is created. When constraints with previously compared features require two features to be further apart than the maximum design-rule spacing, there is no need to check the actual spacing constraints between the tiles in these two features. One method [Kingsley 84] keeps track of just one longest path, which results in extra comparisons. Another [Hedges 85] uses a limited-depth search and a square bitmap to store previous results, which requires a great deal of memory. While these are still  $O(n^2)$  worst case algorithms, they are relatively fast  $O(n^2)$  algorithms. Using the horizontal-band improvement described in the previous paragraph reduces the worst case to  $O(n^{1.5})$ .

A more complex and theoretically faster algorithm uses shadowing [Hsueh 79a]. The tiles are lexicographically sorted on the (x,y) coordinates of their lower left hand corners. A vertical frontier forms and moves to the right as the tiles are processed. The frontier consists of the processed tiles that could still possibly be seen by a tile to the frontier's right. Constraints are generated from tile(s) in the frontier to each tile before that tile is added to, and shadows part of, the frontier. A tile is shadowed when constraints from it to any possible tile to the right of the frontier are superfluous. This is an elaboration of the basic algorithm used in many design-rule checkers [Baird 77]. Maintaining the frontier can be difficult since a tile often shadows only part of another tile and a large tile can be cut into pieces by the shadows of several small tiles. In Figure 1-4A, tile A is completely shadowed, tile B is partially shadowed, and tile C is shadowed in several sections.

The scan line algorithm [Schlag 82] (sometimes called event driven [Burns 87]) is shadowing seen from the other dimension. A horizontal line is scanned from bottom to

Figure 1-4 A. Shadowing B. Scan Line

top and the set of tiles currently cut by the line is maintained in a balanced tree. Tiles are inserted into and deleted from the tree as the scan line crosses their bottoms and tops, respectively. Neighboring tiles in the tree are visible to each other (along the scan line) and are given spacing constraints. This O(nlgn) algorithm generates at most 3nconstraints. Visibilities still generate more constraints than are absolutely necessary. In Figure 1-4B, the current scan-line position generates three constraints but only the one between tiles A and B is necessary since the others are blocked by intervening tiles. By caching recent constraints, the algorithm can remove unnecessary constraints during the constraint generation [Lengauer 83]. In Figure 1-4B for example, when the scan line hits tile E, the algorithm realizes that the constraint between tiles C and D can be thrown out.

The above algorithms need to be completely rerun whenever anything is moved or changed. One way to reduce these recomputations is to use the wires to divide the layout into regions [Watanabe 84]. The set of tiles in or on the edge of each region is invariant during compaction since wires remain connected to their endpoints. An every pair algorithm can be used separately on each region. When tiles are moved, only the affected regions need to be redone. One problem with this algorithm is that it runs slowly when regions are large.

The corner-stitching [Ousterhout 84] data structure allows more general, incremental changes. While designed for a layout editor, the routines used to check for design-rule violations are similar to the ones needed to generate the design-rule constraints. Corner stitching adds space tiles to fill the empty spaces in the layout and completely cover the plane. The algorithm keeps the tiles in a canonic form of maximal horizontal strips by cutting tiles horizontally and recombining them, giving preference to width over height. This canonic form is useful in a layout editor since it prevents fragmentation, but it has some drawbacks for compaction: it loses x-y symmetry and obscures the mapping between higher level descriptions and the layout. Figure 1-5 gives an example of the space tile changes that occur when a tile (shown dark) is added.

Figure 1-5 Corner Stitching: Tile Addition

A variant of corner stitching combined with shadowing forms the basis for the algorithm described in Chapter 2. The adjacency lists algorithm [Carpenter 87] retains the speed of shadowing and the incremental properties of corner stitching but is tailored to generating design-rule constraints.

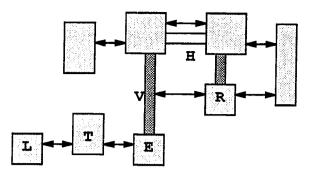

### 1.3. Solving Constraints

CABBAGE [Hsueh 79b] was one of the first systems to generate and then solve constraints. It forces wires to connect to fixed points on endpoints so wire constraints are not needed to keep wires and endpoints fully connected. The spacing constraints form an acyclic graph that is easily solved in linear time to find the critical path across the circuit. The critical path determines the layout's minimum size and the placement of the tiles on the path. CABBAGE uses a scheduling algorithm to place each group of wired-together tiles as low as possible. A group can be placed only after all the groups that could hold it up have been placed -- each group is given a count of the unplaced groups directly below it and when that count is reduced to zero, the group is added to a queue of placeable groups. REST [Mosteller 81] uses the same compaction algorithm but in addition has an elaborate system to allow stick diagrams to be entered using sloppy line segments.

Liao gives an algorithm [Liao 83] to handle the constraint-graph cycles caused by designer-specified maximum spacings. It alternatively performs the scheduling algorithm to satisfy the spacing constraints and a separate, simple pass to satisfy the designer-specified constraints (by moving single groups upwards ignoring the spacing constraints). The algorithm finishes when a simple pass does not move any groups.

Introduction

The maximum number of passes is bounded by the number of designer-specified constraints in the critical path. More flexible compaction systems have a much larger number of constraint cycles -- caused by the wire constraints needed when wires are allowed to slide on wide endpoints. Not tying wired-together tiles into rigid groups allows smaller layouts to be created. Schiele's compactor [Schiele 83] handles the constraint cycles by repeatedly passing through a list of the constraints to move single tiles up to fix any found constraint violations. Again, the algorithm finishes when a pass does not move anything, but now the maximum number of passes is bounded by the length of the critical path. This gives the algorithm a slow,  $O(n^2)$  worst case.

Just compacting a layout to minimum size leaves a range of possible placements for tiles not on critical paths. One way to take advantage of this freedom is to perform wire-length minimization. Shorter wires allow circuits to operate faster and, by bunching things together, can actually allow the creation of smaller layouts. Schiele heuristically minimizes wire length. First, all the lower endpoints (of vertical wires) that are free to move up without moving any other tiles are moved up. Since movements can free other movements, this step loops until no more simple movements arc possible. Then a single pass is made through the lower endpoints to move larger sets of tiles. This heuristic not only makes useless simple movements, it also gives up too easily on larger movements. Lakhani uses an improved, event-driven algorithm [Lakhani 87] that continues until all helpful movements have been made.

LAVA [Eichenberger 86] uses a min-cost max-flow network algorithm to minimize each dimension's total wire length. The compaction problem is converted into a linear-programming problem: the constraints become linear inequalities and the wire lengths are embedded in the objective function. The network algorithm first minimizes the wire lengths and then searches through the constraints to find a set of nconstraints that enforce a legal layout. This search has an exponential worst case. The algorithm is described in Chapter 3. Tailor's compactor [Marple 88] is similar except it uses a dual network algorithm that first finds a legal layout and then adjusts it to minimize the wire lengths.

Optimal two-dimensional compaction is NP-complete [Sastry 82]. It requires deciding for every pair of neighboring tiles whether it is better for one to be above or to the right of the other. Schlag gives an algorithm [Schlag 83] that starts with just the wire constraints and then recursively adds one possible spacing constraint at a time (from the  $O(n^2)$  size set of all possible left-right, up-down constraints). It stops and

9

Introduction

backtracks when either a legal layout is created, the current layout becomes larger than the smallest known legal layout, or the current set of constraints becomes infeasible. Given enough time, this simple branch-and-bound search will always find an optimal layout. Watanabe's compactor [Kedem 84] uses a more efficient search over a smaller set of constraints. Instead of starting with infeasible tile positions and adding constraints, it starts with a legal layout and swaps x and y constraints to reduce the critical paths and thus the layout area.

Many approximate two-dimensional algorithms have been devised. Mosteller's 2-D compactor [Mosteller 87] uses Monte Carlo methods to produce curvilinear layouts: wires bend around randomly placed and moved round endpoints. Supercompaction [Wolf 88] is a compromise between one- and two-dimensional compaction. It iteratively recompacts after moving tiles and creating wire jogs to reduce the preferred dimension's critical path. MACS [Crocker 87] uses a more efficient, event-driven approach to incrementally introduce wire jogs along the critical path and to move groups to minimize wire length. ZORRO [Shin 87] does local twodimensional compaction by allowing lateral movements of elements to try to pack the tiles during repeated compaction steps.

The above algorithms are all batch algorithms: they need to be completely rerun whenever anything is moved or changed. They do not give the designer any control over the interaction between the two dimensions except maybe to specify which dimension has priority and should be compacted first (the compaction in the first dimension interferes with the compaction in the second). An incremental compactor can efficiently propagate changes between the two dimensions. Thus it not only gives designers more control, it also quickly performs multiple one-dimensional steps and makes an ideal basis for two-dimensional compaction. An incremental compactor needs a data structure that stores enough information to allow quick updates. We combine the min-cost max-flow network spanning tree with routines to move weighted subtrees to derive the tree weight algorithm. The algorithm uses a simple batch graph compaction to produce a good estimate of the desired spanning tree. Then a depth-first scan through the tree minimizes the wire length and prepares for incremental changes. This algorithm is described in Chapter 3.

10

# Chapter 2 Generating Constraints

This chapter describes how the set of spacing constraints needed for compaction is generated and incrementally updated. The algorithm presented not only quickly generates the smallest complete set of constraints for a circuit, but also allows one to update the constraints with an effort proportional to the size of the change instead of the size of the circuit when objects are moved, deleted, or inserted. We start with a description of the adjacency lists data structure and its use in the simple single-color case. Then we cover the extensions needed to handle wires, overlapping tiles, and multiple colors. We also give a simple, quick method for initially loading the adjacency lists data structure. We finish with a discussion of the algorithm complexities. The examples in this chapter show generating and updating the set of constraints needed for an x-direction compaction. These constraints are affected by y-direction movements. Using two data structures, one for each dimension, allows the same routines to be used for the symmetric y-x case.

# 2.1. Adjacency Lists

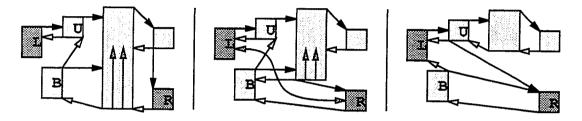

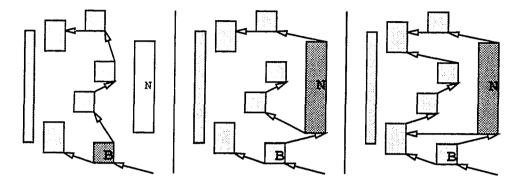

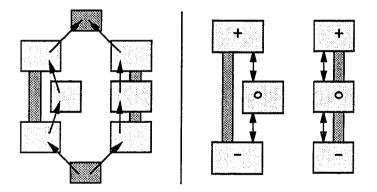

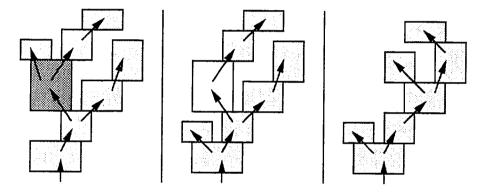

Figure 2-1 A. Adjacencies B. Visibilities

The constraint generation algorithm is based on a strict definition of adjacency. Two tiles are adjacent if and only if moving them in the compaction direction could cause them to hit each other without passing through any other tiles. This is more

restrictive than using visibilities. Because of the intervening tiles in Figure 2-1A, tile A is not adjacent to tiles B and C even though it is visible to them. If we add space tiles to the example (Figure 2-1B), we see that, in the single-color case, the space tiles correspond to visibilities while a subset of the space tiles (marked by dashes) corresponds to our adjacencies. The space tiles form maximal horizontal strips; therefore each space tile's height is determined by neighboring non-space tiles. A space tile's top edge must touch either a non-space tile's bottom edge or one of its top corners (or some combination). Each of a non-space tile is two top corners and one bottom edge can determine the top of at most one space tile. Hence, if there are n non-space tiles there are at most 3n space tiles. The space tile corners; thus there are at most 2n adjacencies. In Figure 2-1B, the space tile corresponding to tile A's top adjacency touches on the top left and bottom right (circled), tile A's bottom adjacency touches on only the bottom right.

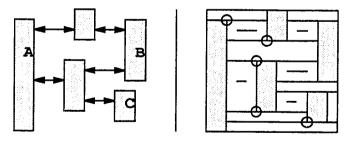

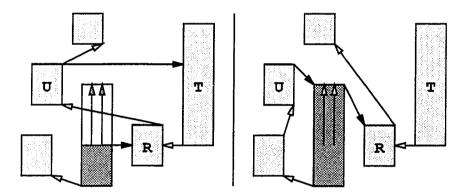

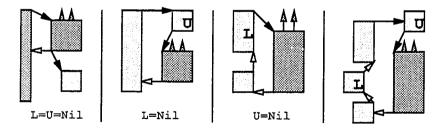

Figure 2-2 A. Adjacency Pointers B. Non-Nil-Ended List

Since there are at most 2n planar adjacencies, the adjacency information can be stored using threaded lists. Each tile record has left, right, up, and down pointers. The lists are threaded clockwise; the left pointer points to the lowest left adjacent tile and the up pointers are followed for the rest of the left adjacency list. In Figure 2-2A, the dark tile has three left adjacencies, found by following light arrows. Likewise, the right pointer points to the highest right adjacency and the down pointers are followed for the rest (the dark arrows). Note that these lists are not always nil ended. It is possible for a tile to be the last tile in one tile's adjacency list and the first in another's. The dark tile in Figure 2-2B is the last tile in tile A's right adjacency list and the first in tile B's. The down pointer of a record is always part of the right adjacency list of the tile pointed to by the record's left pointer. Likewise, the up pointer belongs to the list of the tile pointed to by the right pointer. In the example, the dark tile's left pointer points to tile B so its down pointer continues tile B's, not tile A's, right list.

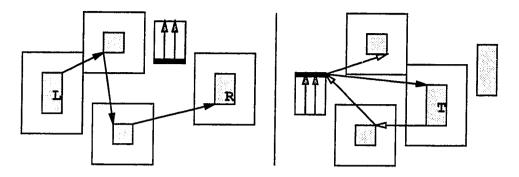

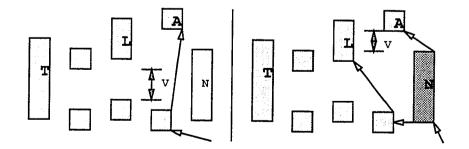

Figure 2-3 Concave Left Turnaround

One common, but non-obvious, operation is to find the tiles above or below a given tile using just the left and right adjacency lists. If tile L in Figure 2-3 were moved upwards we would have to search above it for possible new adjacencies. Since tile L's up pointer is nil we cannot search directly up. Instead we search to the right for a turnaround; then we can search back to the left. Turnaround tile T must be found to travel up or down within the example: the lower half of the tiles have nil up pointers and the upper half have nil down pointers. Right pointers tend to go upwards since they point to top right adjacencies. So, to find a concave left turnaround from below, one just follows right pointers until a non-nil up pointer is found. To find one from above, right and down pointers are followed to find bottom right adjacencies. The turnaround from above occurs when a tile's left pointer does not point back to the previous bottom right tile. In the example, turnaround tile T's left pointer does not point back to tile A.

## 2.2. Single Color Case

Having defined what adjacency lists are, we now describe the routines used to maintain the adjacency lists for the simple case where there is only one color (type) of tile and the only design rule is that tiles can touch but not overlap. This rule is equivalent to replacing a spacing rule of k with a spacing rule of zero after bloating all the tiles by k/2. A frame of special tiles surrounds the layout so that all the normal tiles

will have left and right neighbors. We describe the growing and shrinking of tiles first, as they are the basic operations used to move, delete, and insert tiles. Starting with a simple case makes it easier to explain the basic algorithm; the extensions needed to handle real layouts are described in subsequent sections.

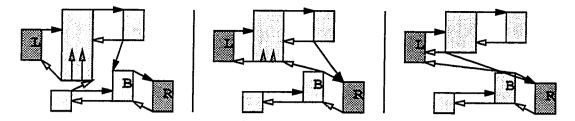

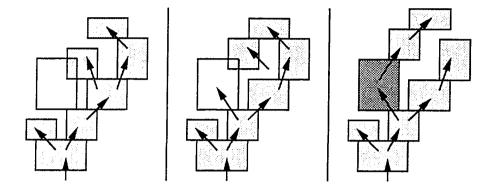

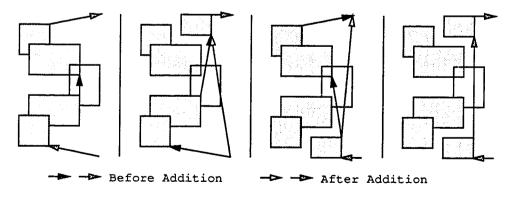

### 2.2.1. Growing Tiles

Tiles are grown by moving their tops up or bottoms down. The cases are symmetric so we just describe moving tops up. As a tile grows, its path may cut old adjacencies and require them to be deleted. The growing tile may also gain new adjacencies which have to be added to its lists. The main part of the grow routine is a loop that scans counter-clockwise upwards to look for adjacencies that cross the growing tile's path. The scan searches right for a turnaround, goes up once, and then left until a tile is found to the left of the growing tile, that is, we scan around concave left turnarounds (Figure 2-3) to find all the crossing adjacencies, one by one, working upwards until a crossing is found at or above the growing tile's final top.

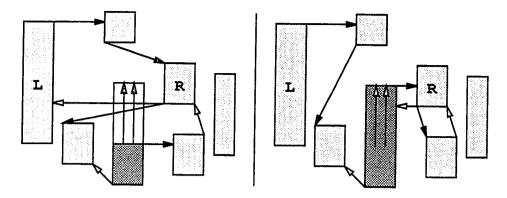

Figure 2-4 Before and After Breaking a Left List

Two cases can occur at the turnaround point: the up tile can be to the left of the growing tile or it can be to the right. If it is to the left, the growing tile has broken into the middle of the turnaround tile's left adjacency list. We remove the up tile from the turnaround's list and add it to the growing tile's left list. In Figure 2-4, up tile U goes from being adjacent to turnaround tile T to being adjacent to the dark, growing tile. Only the relevant pointers are shown. In the other case, the up tile is on right and we have to search for the cut adjacency. Left pointers are followed to find a pair of tiles, one to the right and one to the left of the growing tile's path. If the right tile is the bottom-most tile in the left tile's right list, the right and growing tiles can be made

Figure 2-5 Before and After Breaking a Right List

adjacent to each other by simply adding them to each other's adjacency lists. Otherwise, the growing tile has broken into the middle of the left tile's right adjacency list. We remove the right tile from the left tile's right list and add it to the growing tile's right list (tile R changes adjacencies in Figure 2-5).

Figure 2-6 Before and After Growing a Tile

Sometimes when a tile is added to the top of a growing tile's adjacency list, that tile shadows the previous top adjacent tile and causes it to be removed from the list. In Figure 2-6, newly adjacent tiles L and R shadow the growing tile's old adjacent tiles TL and TR. This occurs on the right when the growing tile's up pointer is non-nil and on the left when some tile's down pointer points to the growing tile. In the example, tile L points down to the growing tile, which points up to tile R.

After the growing upwards loop is finished, one more adjacency may remain to be found on each side of the grown tile. The grow loop finds all the adjacencies created when the growing path cuts between pairs of tiles, but the grown tile's top corners may also catch on nearby tiles' bottom corners to create new adjacencies. On the right side,

Figure 2-7 Final Search for Top Adjacencies

the top half of the last scanned turnaround is reverse scanned for a tile whose bottom is low enough to be adjacent to the growing tile. A similar search until turnaround is made to the left for a new top left adjacent tile. In Figure 2-7, we find two new adjacencies: the search from tile R finds tile TR and from tile L finds tile TL. If the grown tile were grown up again, further, these final adjacencies would be shadowed (as in the previous paragraph).

### 2.2.2. Shrinking Tiles

Shrinking a tile is the reverse of growing one. We only describe moving bottoms up since the tops down case is symmetric. As a tile shrinks, it may lose some of its adjacencies and cause new adjacencies to be stitched between tiles on either side of its old position. The shrink routine is a loop that moves the bottom up to drop one tile at a time from the shrinking tile's adjacency lists.

Figure 2-8 Before and After Shrinking a Tile

Two searches are performed as each tile is dropped. When the bottom tile is removed from the shrinking tile's right adjacency list, one search is made to the right of the dropped tile for a tile to replace it in the shrinking tile's right adjacency list and the other search is made to the left of the shrinking tile for a new top left adjacency for the dropped tile. The search for a new right adjacency follows right pointers until a turnaround is reached or a tile is found whose top is high enough to be adjacent to the shrinking tile's current bottom. The left search likewise follows left pointers looking for a tile with a bottom low enough to be adjacent to the dropped tile. In Figure 2-8, the right search from dropped tile D finds that tile R should now be adjacent to the shrinking tile, while the left search finds that tile L should now be adjacent to tile D. If the shrinking tile shrunk a little more, it would drop its new adjacency with tile R. When a tile is dropped from the shrinking tile's left rather than right adjacency list, symmetric left-up and right-down searches for new adjacencies are used.

### 2.2.3. Changing Tiles

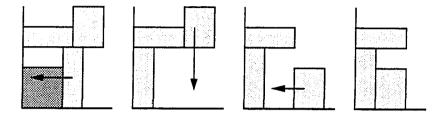

The grow and shrink routines are used to move, delete, and insert tiles. To move a tile a short distance, we can grow it to make it stretch over its new position and then shrink it to its proper size. To move a tile a longer distance, it is faster to delete the tile and then add it back at its new position to avoid cutting and restitching many adjacencies.

To delete a tile, the tile is first shrunk to zero height so that it will have exactly one left and one right adjacency. The zero height tile is then removed from these tiles' adjacency lists and a simple check decides if the left and right tiles should be adjacent to each other or not. They are made adjacent if the deleted tile was either the only tile in one or both of their adjacency lists, the last tile in both lists, or the first in both lists.

Inserting a tile is the reverse of deleting one. A zero height tile is inserted between two tiles to start its adjacency lists and is then grown (down and up) to its proper size. Locating the two initial adjacencies is a two-step process. Starting at any tile (preferably one nearby), up/right or down/left pointers are followed to find a tile at the same height as the bottom of the new tile. The up pointers move quickly, but if one is nil or jumps over the desired height, the right pointers also tend to go up since they point to top adjacencies. Likewise, the down and left pointers are used to go down. Starting at tile S in Figure 2-9, the height search uses one right and one up pointer.

Once a tile is found at the correct height, the adjacency lists are followed to the left or right to find pairs of tiles at the correct height until a pair is found with one tile on the left and one on the right of the new tile's desired position. The tiles in each pair of tiles

Figure 2-9 Locating Where to Insert a Tile

are visible to each other but need not be adjacent; when none of the tiles in a list are at the wanted height, a search until turnaround is used to go up or down from the listed tile(s) found just below or above the wanted height. In Figure 2-9, the second found pair is the correct one. The final right tile R is found by searching through tile B below the desired height.

### 2.3. Wires

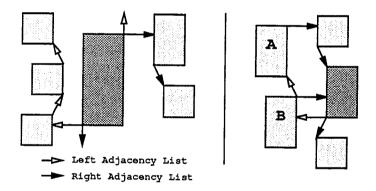

So far we have discussed one kind of tile, but in layouts there are two very different kinds of tiles: fixed-size objects and wires. In our system, wires connect to fixed-size tiles, not to other wires, with at most one wire connected to each tile's side. An endpoint is made at least as wide as the wire(s) connected to it in order to provide a full connection. When an endpoint is wider than a wire, the wire is free to slide along it. In Figure 2-10, vertical wire V is not rigidly connected to endpoint tile E. Wires could be represented as simple, varying-size tiles but we can take advantage of the fact that their ends are protected -- a horizontal wire never generates any constraints useful in x-direction compactions because it is always completely shadowed by the two endpoints to which it is attached. In Figure 2-10, no tile is needed for horizontal wire H. Thus, while non-wire tiles require two tile records, one for each dimension, we can get by with just one tile record per wire.

If we use two pointers in each tile record, a wire-up and a wire-down pointer, to doubly link wires and endpoints together, we can take advantage of the fact that wires stretch when their endpoints move. Wires themselves never need to be moved. When an endpoint is shrunk away from its wire, the wire grows to follow it. Thus instead of the usual shrink loop, the shrink routine can just see how many of the tiles in the

Figure 2-10 Wire Adjacencies

endpoint's adjacency lists need to be moved to the wire's adjacency lists. Endpoints growing towards their wires likewise shrink wires and simply take back some of these adjacencies. Moving endpoint E down and up in Figure 2-10 causes vertical wire V to grow and shrink and gain and lose adjacencies (with tiles T and R), respectively. The wire-up and wire-down pointers can also serve as turnarounds since nothing can pass between a wire and its endpoints. If tile L in the example was grown upwards, the counter-clockwise grow scan could turn around at wire V.

Since a vertical wire is horizontally constrained by its endpoints, it follows, using transitivity, that if a tile is adjacent to one or both of a wire's endpoints, it does not need to also be adjacent to the wire. In Figure 2-10, because of the spacing constraint between tile T and endpoint E and the wire constraint between the left edge of endpoint E and the left edge of its wire V, no spacing constraint is needed between tile T and wire V. Thus we can change the definition of adjacency to say that a tile and a wire are adjacent if and only if the tile is adjacent only to the wire (on that side) and that two wires are never adjacent. In Figure 2-10, tile R's only left adjacency is wire V and the two vertical wires are not adjacent. Note that now, unlike other tiles, a wire's left and right pointers can be nil and its up and down pointers are always nil. Wire V in the example has no left adjacencies.

It is relatively easy to modify the algorithms to handle this definition. A grown tile with more than one adjacency will never be adjacent to a wire, but one extraneous wire adjacency is allowed while a tile is growing so that it can grow past wires. A wire adjacency will be shadowed by any new adjacency or, if necessary, removed after the grow loop. A shrinking tile becomes adjacent to a wire only when nothing else is available; thus a shrinking tile will never lose a wire adjacency. While doing a locate and searching an adjacency list from a wire, if the list is empty or its tiles are all too high or all too low, the search is continued from the wire's endpoints. To delete a wire, one endpoint is grown towards the other endpoint to zero out the wire. Then the wire is removed and the endpoint is shrunk back. Likewise, to insert a wire, one endpoint is grown towards the other until no adjacencies cross between the endpoints. Then the wire is added between the endpoints and the grown endpoint is shrunk back to its correct size. This causes the proper adjacencies to be transferred from the endpoint to the wire.

In summary, taking advantage of the special properties of wires greatly improves the constraint generation. Using fewer tile records means less memory is required. The wire-up and wire-down pointers, which are needed anyway during compaction to keep wires and endpoints connected, speed up constraint generation and make updates faster. More importantly, since fewer constraints are generated in both dimensions, less time will be required to solve the constraints. The algorithm changes required to achieve these improvements are relatively simple, especially since something has to be done anyway to allow for the varying wire lengths.

## 2.4. Overlapping Tiles

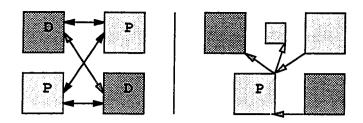

In VLSI compaction, most of the spacing rules can be relaxed between tiles that are electrically connected since there is no need to keep them from shorting out. Not allowing bloated tiles to overlap causes every wire's two endpoints to be spaced at least their minimum spacing distance apart and thus gives every wire a minimum length equal to the bloat distance. This, for example, would cause wire jogs to always jog at least the spacing distance and would space diffusion contacts far away from transistors. To overcome this problem, we can create netlists specifying which tiles are electrically connected and can thus legally overlap. One simple, but slow, method is to force overlapping tiles to be adjacent to each other. Any wire between two such tiles is unnecessary and is removed and added to a list of negative-length wires. After all the movements are done, this list is checked to see if any of the wires now have positive lengths and should be added back to the graph.

## 2.4.1. General Case

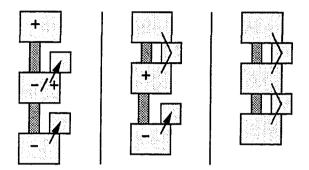

Figure 2-11 Constraints With Pass-Throughs

The most general algorithm would not generate any constraints at all between electrically connected tiles and thus allow such tiles to pass through each other. This flexibility allows a left wire jog to become a right wire jog and vice versa and allows the ordering of taps off of busses to vary. It also makes it much harder to read the constraints from the adjacency lists. To find all the constraints for a tile on net I, we not only have to make a transitive search through adjacent net-I tiles to find the first constraint, say with a tile on net J, we then have to continue the search until we find a tile not on net J. This long search is required because even the furthest away (last scanned) net-J tile could pass through all the intervening net-J tiles and hit the net-I tile after that tile has passed through all the intervening net-I tiles. In Figure 2-11, we have to search all the way from the right-most tile to the left-most tile to find the right tile's two left spacing constraints. While these transitive searches complicate and slow normal shadowing algorithms, they are particularly bad in incremental compaction since constraints may be read from the adjacency lists many times.

Figure 2-12 Fixing Negative Length Wires

Another problem with letting tiles pass through each other is that negative-length wires are created when one endpoint of a wire passes completely through the other endpoint. Having a wire's upper endpoint below its lower endpoint would confuse the grow and shrink routines. Swapping a negative-length wire's wire-up and wire-down pointers restores its positive length and fixes the problem but, unfortunately, creates a new problem -- it may try to point an endpoint's wire pointer at two different wires at once. In Figure 2-12, moving the center endpoint down gives the right wire a negative length. Swapping the wire's endpoints causes a problem with the moved endpoint's wire-up pointer. When a pointer conflict occurs, the shorter wire is given preference: the longer wire is disconnected from the endpoint, shrunk, and attached to the other endpoint of the shorter wire. This recurses until a free endpoint is found. A wire or endpoint may have to be moved horizontally slightly to make a full connection when a vertical wire's endpoints are changed. In Figure 2-12, the left, longer wire is shrunk and connected to the new center endpoint, which is moved left slightly to allow a full connection.

Figure 2-13 A. Insert on Left or Right? B. Cannot Insert Wire

Besides requiring left-right pointer updates, allowing tiles to overlap and cross leftto-right also causes a problem with the function used to decide whether a tile is to the left or right of another tile. Because we use left and right adjacency lists even when two tiles overlap, one tile has to be declared the left so they can be made adjacent. Just comparing left coordinates no longer gives consistent results near wires. When a wire's endpoints are wider than the wire, their left edges do not have to line up. A tile's left edge could be to the left of one endpoint's left edge and to the right of the other's. In Figure 2-13A, it is not clear whether the new tile, which overlaps the center endpoint, should be added on the left or right of the overlapped endpoint since a comparison with the bottom endpoint implies it should be on the left but a comparison with the top endpoint implies it should be on the right. Similarly, if a new wire's desired endpoints are on the opposite sides of a tile, one of them needs to be moved before the wire can be inserted. In Figure 2-13B, the search from the bottom endpoint, on the right, will not be able to find the top endpoint, on the left.

## 2.4.2. Restricted Case

Figure 2-14 Constraints Without Pass-Throughs

In the previous section we saw that allowing tiles to pass through each other causes several problems. With a slight loss in generality we can greatly reduce these difficulties. We allow tiles to overlap but not pass through other tiles; we force the right tile's right edge to be at or to the right of the left tile's right edge and likewise for their left edges. Thus, when two tiles are electrically connected, instead of generating a spacing constraint between the right edge of the left tile and the left edge of the right tile, we generate two zero valued constraints: one between their left edges and one between their right edges (see Figure 2-14). Not allowing left edges to cross left edges, and right over right, fixes many of the pass-through problems: no adjacency searches are needed to determine the constraints, there are no negative-length wire conflicts, and movements never swap left and right adjacencies.

The problem with determining left-rightness is also eliminated except when edges exactly overlap. A simple way to solve this is to define two tiles to be electrically connected if and only if there is a wire directly between them. Then, when two tiles exactly overlap, we can check the wire pointers to determine which is the left and which is the right endpoint. If, when moving several tiles, we always grow the left-most endpoint up first, right endpoints will always grow to the right of any tile they exactly overlap. This allows the grow routine to always break ties in the same direction. To keep from producing temporarily negative-length wires, we break vertical ties so that top endpoints always move up before bottom endpoints. We move right and bottom endpoints down first for the same reasons. Using the direct-connect definition of electrically connected also saves us the trouble of incrementally updating the netlists when tiles are inserted or deleted.

Left and right overlaps in one dimension appear as up and down overlaps in the other. A pointer conflict can occur when top-to-bottom overlapped tiles need to share some of their adjacencies. For example, if three overlapping tiles, on the left, are adjacent to three overlapping tiles, on the right, we may have to generate adjacencies between each of the left tiles and each of the right tiles -- nine adjacencies in all. The planar adjacency list pointers cannot directly handle so many adjacencies. To resolve this problem, we semi-merge top-to-bottom overlapped tiles -- the semi-merged tiles share one common pair of adjacency lists but still move independently. For more details see Appendix A. Semi-merging makes it slightly harder to read the constraints from the adjacency lists and it can create a few over-restrictive adjacencies. The method works fairly well but our implementation depends on the simple direct-connect definition of electrically connected.

Figure 2-15 Compaction-Order Effects on Overlap

Using the direct-connect definition makes it fairly easy to overlap and merge tiles but, unfortunately, it does not allow all legal overlaps. The most noticeable case is that the three endpoints in an L-shape wire cannot all overlap. The two end endpoints are not directly connected by a wire and thus are not allowed to overlap. Which endpoint will overlap the middle endpoint depends on which dimension is compacted first; the second dimension will see a spacing constraint between the two end endpoints. In Figure 2-15, a x-then-y compaction reduces the L-shape wire to a vertical wire, while a y-then-x compaction reduces it to a horizontal wire. While many L-shape wires can be eliminated by changing the stick diagram, doing so is awkward and prevents some useful constructs. The only practical way to fix this problem is to use full netlists and modify the adjacency routines to allow locally unrelated tiles to overlap.

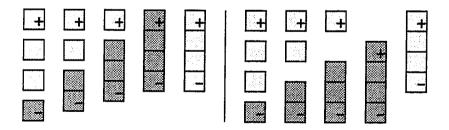

# 2.5. Multiple Colors

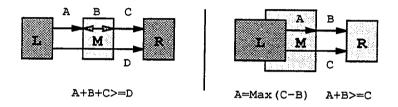

So far we have had just one color (type) of tile and one spacing rule. A real layout needs many types of tiles and many spacing rules. We separate the colors that do not interact into independent planes; each plane consists of a set of tiles connected together by adjacency lists. For nMOS there is a metal plane and a poly-diffusion plane. In a plane with two or more colors, it is unlikely that using constant bloats for each color will satisfy all the spacing rules. Therefore the tiles are stored unbloated and when comparing two tiles, their colors are used as indices into an array of spacing rules to find the appropriate bloat. Rules with very large spacing distances (p- to n-diffusion in CMOS can bleed across poly) would force us to search through adjacencies to find all the spacing constraints. To prevent these searches, we restrict the rules handled in each plane so that whenever tile L is adjacent to tile M and tile M is adjacent to tile R, no spacing constraint is needed between tiles L and R. Figure 2-16A shows the three-color rule that must apply for all possible color combinations within each plane: the sum of spacing constraints A and C, from tiles L to M and M to R, and the minimum legal size B of tile M must be greater than or equal to any spacing constraint D from tiles L to R. For CMOS, a well plane (with well boundary tiles and duplicated diffusion tiles) must be created to handle the p- to n-diffusion rules.

Figure 2-16 A. Spacing and B. Overlap Bleed-Throughs

A similar rule bleed-through problem occurs when tiles overlap. When all the spacing rules were identical, not allowing the right edges of a left tile and an overlapped middle tile to cross guaranteed that no spacing constraint was needed between the left tile and any possible tile to the right of the middle tile. To prevent multiple colors from requiring us to search through overlapped tiles, we increase the constraint between overlapped tiles' right (and left) edges from the previous zero value to a small constant. For each possible pair of overlapping tile colors, we calculate and store in an array the maximum difference between the spacing constraints from the left and the overlapped middle tile to any possible color right tile. In Figure 2-16B, constraint A, the minimum allowable right to right edge distance for tile colors L and M, is calculated using constraint B, from tiles M to R, to make constraint C, from tiles L to R, unnecessary regardless of tile R's color.

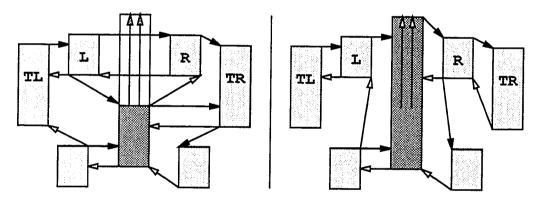

# 2.5.1. Fuzzy Edges

Figure 2-17 A. Locate Off By Bloat B. Shrink Slip Through

The apparent positions of tile tops and bottoms are now fuzzy since the effective bloat of a tile varies with the color of the tile with which it is being compared. This fuzziness causes two problems. The first is minor and occurs when a tile is smaller than the minimum legal size (for that color tile). This can only happen during a tile insertion or deletion. For insertions, the locate to find a pair of tiles to start a new tile's adjacency lists might not be able to find two unbloated tiles at exactly the desired height. In Figure 2-17A, the locate (starting at tile L) returns tiles L and R even though the new tile might not be adjacent to them. After the new tile is inserted and grown to its proper size, the adjacency between it and right tile R may have to be removed (depending on their proper bloat). For deletions, if the shrinking tile in Figure 2-17B dropped its adjacency with tile T, it would be left with no legal right adjacency. The shrinking tile is in the middle of T's left adjacency list; letting it slip over tile T would destroy T's list. Since the shrinking tile is about to be removed, we can just make the shrink loop stop early and leave the shrinking tile adjacent to tile T. If it was not for the three-color rule (Figure 2-16A), normal small tiles could also slip diagonally between adjacencies and cause many problems.

The second fuzzy-edge problem, the around-the-corner problem, is more serious. The adjacency list data structure can only model planar graphs: that is what makes it possible to have just one up and one down pointer per record. But the fuzzy edges make it possible for constraints to diagonally cross. A simple case is shown in Figure 2-18A where four tiles are arranged in a tight square with a diffusion tile above a poly tile on the left and below one on the right. The tiles can be close enough to generate four pairs of constraints since the poly-diffusion spacing rule is smaller than the poly-

Figure 2-18 A. Crossed Constraints B. Up Pointer Conflict

poly and diffusion-diffusion spacing rules. Adding another tile in the middle of all this can cause an up or down pointer to need to point to two tiles at once. Tile P in Figure 2-18B is in the middle of two left adjacency lists.

Searches for around-the-corner adjacencies are needed after growing and while shrinking tiles to avoid missing any constraints. These constraints are kept in a separate list since they cannot be included in the normal adjacency lists. In a batch compactor, this list is checked when the compaction constraints are generated to see if the constraints are still valid and, if so, if they can now be added to the normal lists. Missing constraints can only occur when tile tops and bottoms are very close; thus a simple test can eliminate or cut short most of the around-the-corner searches. The maximum vertical extent of a search is determined using a precalculated function of the colors' bloat distances. This fudge distance is how far the top of a middle tile must be above the top of a left tile before any right tile high enough to be able to slide horizontally over the middle tile will also be able to slide over the left tile (the middle tile completely shadows the left). Note that this distance is the same as the one used to keep constraints from bleeding through overlapped tiles (Figure 2-16B rotated ninety degrees). The next two sections describe how to modify the grow and shrink routines to handle multiple colors.

## 2.5.2. Growing Tiles

After we grow a tile, we have to search for a missing adjacency on its left and on its right. In the section on growing tiles upwards we saw that after the growing loop was finished we sometimes had to search left and right-down until turnaround from tiles just above the grown tile to look for possible final adjacencies. The around-the-corner search is the continuation of this search pretending that the first found turnaround tile was removed. On the right side, the turnaround was the last tile in some tile's right

Figure 2-19 A Complex Around-the-Corner Search

adjacency list (tile T in tile L's list in Figure 2-19). We find the second to last tile in that list, if there is one (tile A in the example), and continue searching right-down from it. If we find a tile with a bottom low enough to be adjacent to the grown tile, we have found an adjacency that could have been added if the turnaround tile was not there. In Figure 2-19, the search finds a missing constraint between the two dark tiles. To start a search, right pointers are followed from the grown tile to find the first turnaround. If any of these tiles have tops more than the fudge distance above the grown tile, the grown tile will be shadowed from any problems on this side and we can abort the search. In Figure 2-19, the two tiles scanned before reaching tile T are not high enough to stop the search.

Figure 2-20 Five-Color Rule

Previously we noted that the spacing and minimum size rules in each plane had to obey a function of three tile colors (Figure 2-16A) to prevent bleed-throughs. It turns out that this three-color rule is not quite strict enough to allow the around-the-corner searches to pretend to remove only one turnaround tile. If tiles 3 and 4 in Figure 2-20 could be adjacent, the search would have to not only examine tile 2, tile 5's second from bottom right adjacency, but also tile 3, the third from bottom adjacency. To prevent this, we make sure tiles 3 and 4 cannot be adjacent: A+1-B+C+D+E>=F must be valid for all possible colorings of five tiles within a plane. All the values are spacing distances except D the minimum size for tile 2. The 1-B occurs because tiles 1 and 5 must be adjacent and B is the spacing rule between those two tiles. This five-color rule does not cause any problem with the CMOS rules as long as the spacing rules are properly divided between the four planes (metal-2, metal-1, active, and well) already required to satisfy the three-color rule.

## 2.5.3. Shrinking Tiles

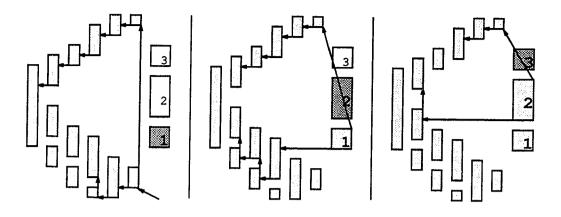

Figure 2-21 Temporarily Cached Missing Constraint

Two major changes have to be made to the shrink routine to handle the around-thecorner problem. First, an extra search is needed after each tile is dropped from a shrinking tile's adjacency lists. When the bottom of a shrinking tile moves up just enough to drop an adjacency on one side (R), it is quite possible that an around-thecorner constraint between the dropped tile and a tile on the other side (L) of the shrinking tile is created. As the shrinking tile continues to shrink and drops the bottom adjacency on this other side (B), it is likely that the constraint can be added directly to the adjacency lists. Therefore we search (left) from the shrinking tile's second from bottom adjacency and cache the missing adjacency, if one, in the hope that it can be quickly resolved. In the first step of Figure 2-21, dropping right dark tile R creates an around-the-corner constraint between it and dark tile L (found by searching from tile U). Dropping the shrinking tile's bottom left adjacency B in the second step allows this missing constraint to be added to the adjacency lists. After the shrinking tile is finished shrinking, if any adjacencies have been dropped from a side, we also have to search for possible missing constraints with the shrunk tile.

The second change to the shrink routine occurs because of the fuzziness of tile tops and bottoms -- the shrinking tile's bottom does not move monotonically upwards. The top of a tile on one side (R) of the shrinking tile may be low enough to not be adjacent

Figure 2-22 Temporary Extra Adjacency

to the shrinking tile's current bottom but still high enough, because of the varying bloats, to be adjacent to a tile on the other side (L) of the shrinking tile. If we just skip the first tile (R), we will miss this unshadowed adjacency (L-R). A simple fix is to not skip any tiles: always make the shrinking tile adjacent to each dropped adjacency's first adjacency. This, in effect, causes the shrinking tile's bottom to sometimes move back down slightly. As each of the adjacent tiles is dropped, its proper unshadowed adjacency, if one, will be found. In the first step of Figure 2-22, we drop the shrinking tile's bottom right adjacency B and make right dark tile R adjacent to the shrinking tile even though it could never possibly hit it. When adjacency R is dropped in the second step, the search to the left of the shrinking tile finds left dark tile L and we make tiles L and R adjacent.

We can do better than the simple, no-skip fix -- many of the tiles can safely be skipped. A dropped adjacent tile will completely shadow from the shrinking tile all the tiles with tops a certain distance below its own. This distance is like the fudge distance except we take the minimum over all possible colors instead of the maximum. Any tile with a top at or below this fudge position can be skipped. This position will monotonically increase during the shrinking loop. Actually, a dropped tile will shadow tiles at various heights depending on their colors. We could store in a shadow array the height below which each different color tile could safely be skipped, but the cost of updating all the entries after every drop is not worth the slight gain from skipping a few more tiles.

A more effective improvement is to store in the shadow array the position of the last tile dropped of each different color. A tile always shadows any tile of the same color with a top at or below its own top. Thus we can skip a tile if its top is at or below the fudge position or if it has been shadowed by a tile of its own color. Except for initializing the array before starting each shrink, this has very little overhead and insures that at most one tile of each color at each height will be checked. Figure 2-23 gives an

example. First, tile A is dropped and the fudge position F is set to slightly below A's top. Tile B's top is above F so it is made adjacent to the shrinking tile and then dropped. Tile B's fudge position is below F so the current fudge position is not changed. Tile C's top is above F but since it shadowed by same color tile B we can skip it anyway. Tile D is likewise shadowed by same color tile A. Tile E's top is above F and above same color tile A's top so it cannot be skipped. Dropping tile E moves the fudge position up slightly.

Figure 2-23 Shrink Shadow: Skip Tiles C and D

## 2.5.4. Summary

Duplicating some of the tiles to create an extra plane to handle large, non-transitive spacing rules is a good compromise between handling all the bloat problems in one plane and eliminating the problems by creating many extra planes (each with a constant bloat). The five-color rule determines which rules can be handled in each plane. Within a plane, the varying bloats cause several problems. Around-the-corner searches are required after growing and while shrinking tiles to keep from missing crossed constraints that cannot be included in the planar adjacency lists. A precalculated function of the bloat distances is used to cut short most of these searches. A constraint cache and a shadow array are used in the shrink routine to help add missing constraints to the adjacency lists and to avoid processing more tiles than is necessary.

# 2.6. Quick Loading

The adjacency lists data structure could be loaded, given an initial placement, by just inserting every tile. This would use a lot of time just locating where to insert each tile. Sorting the tiles lexicographically on the (y,x) coordinates of their lower left hand corners before inserting them makes the locates fast but creates a long horizontal frontier between the added tiles and the top edge of the frame that is often searched as tiles are grown to their proper sizes. It is better to sort the tiles on (x,y). As they are

added in this order, each tile will have nothing to its right except the right edge of the frame. Thus a simple, quick load routine can be used. The locate reduces to finding the tile in the right edge's left adjacency list just below the new tile's bottom. The growing loop reduces to replacing some of the tiles in that left adjacency list with the new tile and making those tiles the new tile's left adjacencies. We still need to scan until turnaround to look for final top and bottom left adjacencies.

Figure 2-24 Quick Load Steps: Locate, Swap, Search