#### **INFORMATION TO USERS**

This reproduction was made from a copy of a manuscript sent to us for publication and microfilming. While the most advanced technology has been used to photograph and reproduce this manuscript, the quality of the reproduction is heavily dependent upon the quality of the material submitted. Pages in any manuscript may have indistinct print. In all cases the best available copy has been filmed.

The following explanation of techniques is provided to help clarify notations which may appear on this reproduction.

- 1. Manuscripts may not always be complete. When it is not possible to obtain missing pages, a note appears to indicate this.

- 2. When copyrighted materials are removed from the manuscript, a note appears to indicate this.

- 3. Oversize materials (maps, drawings, and charts) are photographed by sectioning the original, beginning at the upper left hand corner and continuing from left to right in equal sections with small overlaps. Each oversize page is also filmed as one exposure and is available, for an additional charge, as a standard 35mm slide or in black and white paper format.\*

- 4. Most photographs reproduce acceptably on positive microfilm or microfiche but lack clarity on xerographic copies made from the microfilm. For an additional charge, all photographs are available in black and white standard 35mm slide format.\*

<sup>\*</sup>For more information about black and white slides or enlarged paper reproductions, please contact the Dissertations Customer Services Department.

#### Eichenberger, Peter Armin

FAST SYMBOLIC LAYOUT TRANSLATION FOR CUSTOM VLSI INTEGRATED CIRCUITS

Stanford University

PH.D. 1986

University Microfilms International 300 N. Zeeb Road, Ann Arbor, MI 48106

Copyright 1986 by Eichenberger, Peter Armin All Rights Reserved

# PLEASE NOTE:

In all cases this material has been filmed in the best possible way from the available copy. Problems encountered with this document have been identified here with a check mark  $\_\sqrt{}$ .

| 1.  | Glossy photographs or pages                                                      |

|-----|----------------------------------------------------------------------------------|

| 2.  | Colored illustrations, paper or print                                            |

| 3.  | Photographs with dark background                                                 |

| 4.  | Illustrations are poor copy                                                      |

| 5.  | Pages with black marks, not original copy                                        |

| 6.  | Print shows through as there is text on both sides of page                       |

| 7.  | Indistinct, broken or small print on several pages                               |

| 8.  | Print exceeds margin requirements                                                |

| 9.  | Tightly bound copy with print lost in spine                                      |

| 10. | Computer printout pages with indistinct print                                    |

| 11. | Page(s) lacking when material received, and not available from school or author. |

| 12. | Page(s) seem to be missing in numbering only as text follows.                    |

| 13. | Two pages numbered Text follows.                                                 |

| 14. | Curling and wrinkled pages                                                       |

| 15. | Dissertation contains pages with print at a slant, filmed as received            |

| 16. | Other                                                                            |

|     |                                                                                  |

|     |                                                                                  |

|     |                                                                                  |

University

Microfilms

International

U M

# Fast Symbolic Layout Translation for Custom VLSI Integrated Circuits

# A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

By

Peter A. Eichenberger

March 1986

© Copyright 1986

ъу

Peter A. Eichenberger

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy.

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy.

Kobert Wathers

Dr. Robert G. Mathews

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy.

Dr. Oswald G. Villard

Approved for the University Committee of Graduate Studies:

#### Abstract

Symbolic layout tools have enormous potential for easing the task of custom integrated circuit layout by allowing the designer to work at a higher level of abstraction, hiding some of the complexity of full custom design. Unfortunately, the practicality of symbolic layout tools has been limited for several reasons. Most important, the CPU resources required to compute a full size integrated circuit from a symbolic description are prohibitively large; this problem has been avoided either by restricting the range of applicability to a narrow class of integrated circuits, or by using a sinapler translation algorithm, which reduces the quality of the output. Other problems include: producing poor quality layouts, insufficient user control of the generated output, and inability to cooperate with other layout tools. There problems make symbolic design of complete chips difficult.

This thesis presents an approach to the symbolic layout problems that produces high-quality layout for an arbitrary circuit without requiring excessive CPU time. The key to this approach includes the use of hierarchy to improve CPU time, the use of wirelength minimization to improve quality, a good balance between optimization of the layout and optimization of CPU time, and a smooth transition over varying degrees of automation. The result has been a symbolic layout tool that has been successfully used to lay out several chips from a design-rule-independent input.

#### Acknowledgements

I am grateful to the many people that provided help and inspiration for this work. In particular, I wish to thank Mark Horowitz, Rob Mathews and Oswald Villard for reading drafts of this dissertation and for providing valuable comments. I would also like to thank Rob Mathews and John Newkirk for the inspiration to work on these problems, and for their helpful suggestions and criticisms. Thanks go to Dan Perkins and Tim Saxe for their help in implementing Lava and much of the supporting software. Finally, I would like to thank my family and friends for their support and tolerance during this sometimes difficult time.

This work was supported in part by DARPA under research contract MDA 903-83-C-0335. The author's support by an IBM Fellowship during the 1979-1980 academic year is also gratefully acknowledged.

# **Table of Contents**

| 1. Introduction                                          | 1   |  |

|----------------------------------------------------------|-----|--|

| 2. Background                                            | 7   |  |

| 2.1 Layout Automation                                    | 7   |  |

| 2.2 Optimization Algorithms                              | 12  |  |

| 3. Lava: A New Layout Description Method                 | 15  |  |

| 3.1 Goals and Specification for an IC Description Method | 15  |  |

| 3.2 Lava Overview                                        | 20  |  |

| 3.3 Intermediate Form                                    | 28  |  |

| 4. Lava Compilation                                      | 31  |  |

| 4.1 Sticks                                               | 31  |  |

| 4.1.1 Standard Sticks Compaction                         | 32  |  |

| 4.1.2 Hierarchical Sticks                                | 42  |  |

| 4.1.3 Improvements and Extensions                        | 52  |  |

| 4.1.4 Summary and a Unified Perspective                  | 62  |  |

| 4.2 Abut Cell Implementation: Tiling Algorithms          | 63  |  |

| 4.3 Summary                                              | 69  |  |

| 5. Solution of Optimization Problems                     | 70  |  |

| 5.1 Problem Characterization                             | 70  |  |

| 5.1.1 Problem Size                                       | 71  |  |

| 5.1.2 Sparseness                                         | 72  |  |

| 5.1.3 Problem Decomposition                              | 80  |  |

| 5.2 Solution Methods                                     | 84  |  |

| 5.3 Performance Results                                  | 93  |  |

| 6. Conclusion                                            | 107 |  |

| Appendix                                                 |     |  |

| References                                               | 113 |  |

# **List of Illustrations**

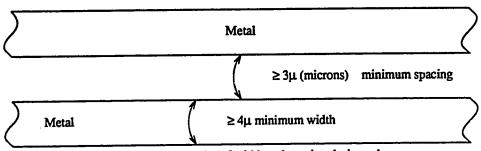

| 1.1a  | Examples of width and spacing design rules                    | 1  |

|-------|---------------------------------------------------------------|----|

| 1.1b  | Example of overlap design rule                                | 2  |

| 1.2   | Design transformations                                        | 3  |

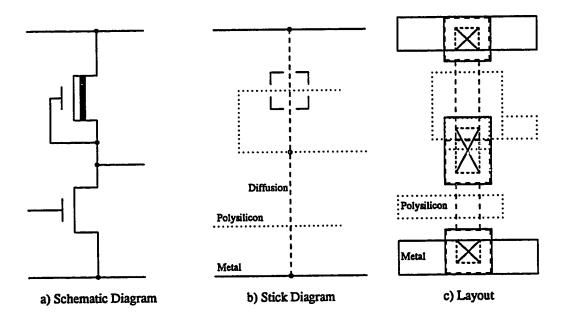

| 1.3   | An NMOS inverter                                              | 4  |

| 1.4   | The advantages of stretch and abut                            | 5  |

| 2.1   | An NMOS inverter                                              | 8  |

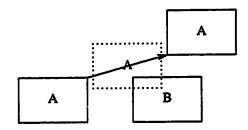

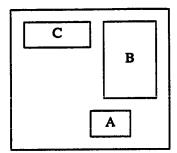

| 2.2   | Non-convexity of compaction                                   | 9  |

| 2.3   | An impossible compaction                                      | 10 |

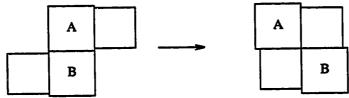

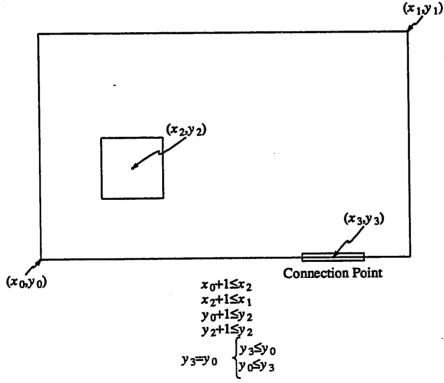

| 2.4   | A design rule spacing constraint                              | 11 |

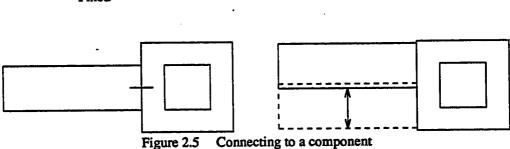

| 2.5   | Connecting to a component                                     | 11 |

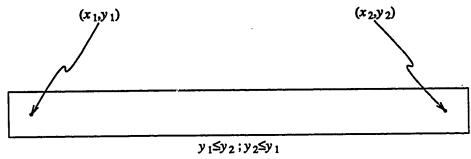

| 4.1   | The component constraints for a wire                          | 32 |

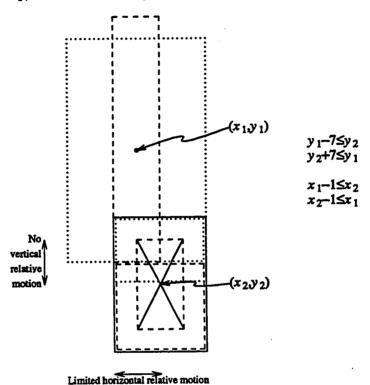

| 4.2   | The component constraints for a depletion load                | 33 |

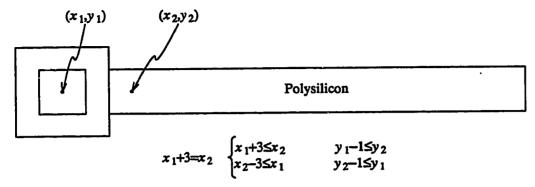

| 4.3   | The connection constraints for a wire and a contact           | 34 |

| 4.4   | Boundary constraints                                          | 34 |

| 4.5   | The generation of a design-rule-spacing constraint            | 35 |

| 4.6   | A constraint graph                                            | 36 |

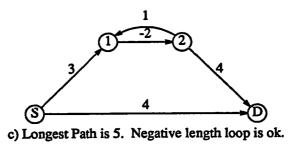

| 4.7   | Three interesting types of constraint graphs                  | 37 |

| 4.8   | Off-center connection to butting contact                      | 38 |

| 4.9   | Initial feasible solution generation                          | 39 |

| 4.10  | Ambiguity of Sticks                                           | 40 |

| 4.11  | Necessity of Pseudo-Coordinates                               | 42 |

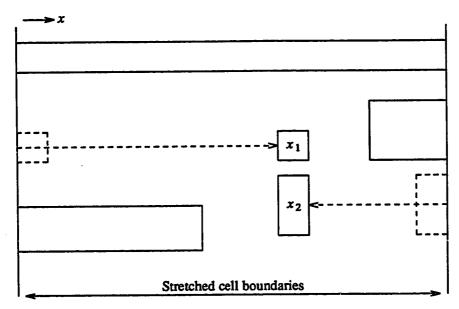

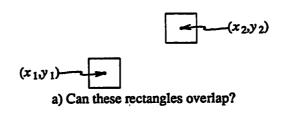

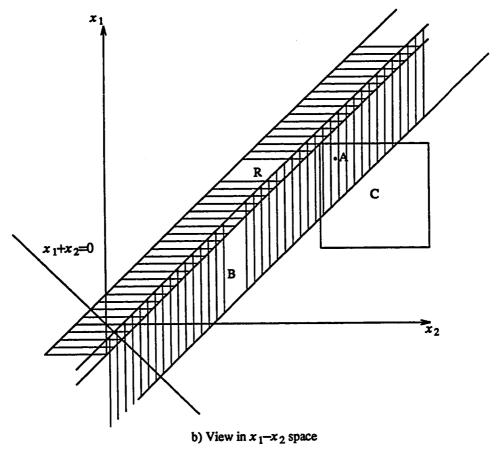

| 4.12  | Hazards of arbitrary stretch lines                            | 43 |

| 4.13  | Overabundance of stretch lines                                | 44 |

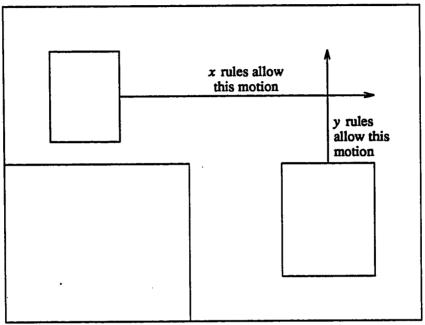

| 4.14  | Undesired x/y interaction                                     | 45 |

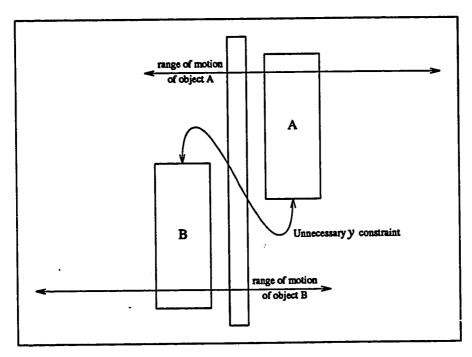

| 4.15  | Additional y constraint                                       | 46 |

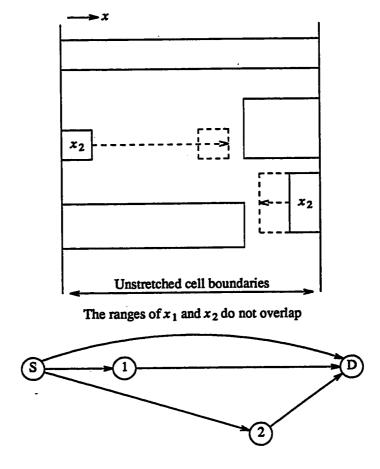

| 4.16a | Stretch rule generation: unstretched cell                     | 47 |

| 4.16b | Stretch rule generation: stretched cell                       | 48 |

| 4.17  | Deciding when to add a constraint for stretch rule generation | 49 |

| 4.18  | Added realization constraints                                 | 51 |

| 4.19  | Variable Merging                                              | 52 |

| 4.20  | Construct requiring non-linear number of constraints          | 54 |

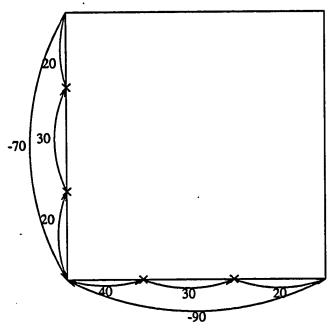

| 4.21  | Conical Shadows                                               | 56 |

| 4.22  | Second step stretch rule shadows                              | 57 |

| 4 23  | Larger than necessary cell                                    | 58 |

| 4.24 | Extra Jogs                                              | 59         |

|------|---------------------------------------------------------|------------|

| 4.25 | A compaction problem requiring wire-length minimization | 59         |

| 4.26 | Results of three different norms applied to figure 4.25 | 60         |

| 4.27 | Shortcomings of L <sup>∞</sup>                          | 60         |

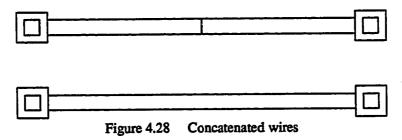

| 4.28 | Concatenated wires                                      | 61         |

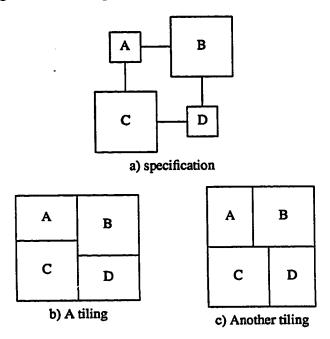

| 4.29 | Ambiguity of Abut specifications                        | 64         |

| 4.30 | Abut constraints during tiling                          | 66         |

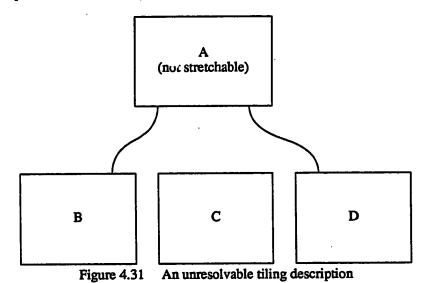

| 4.31 | An unresolvable tiling description                      | 68         |

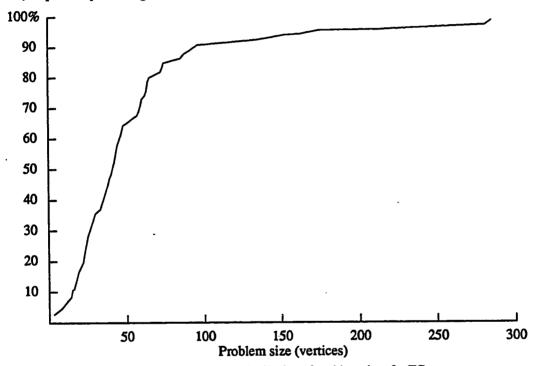

| 5.1a | Cumulative distribution of problem sizes for TC         | 72         |

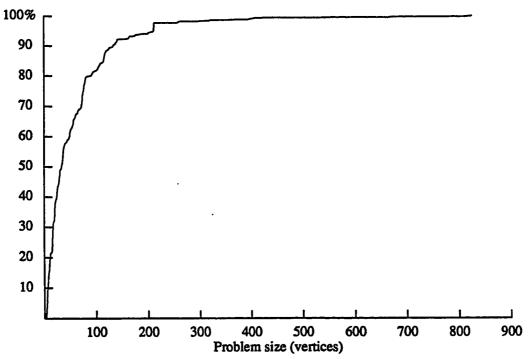

| 5.1b | Cumulative distribution of problem sizes for FP         | 73         |

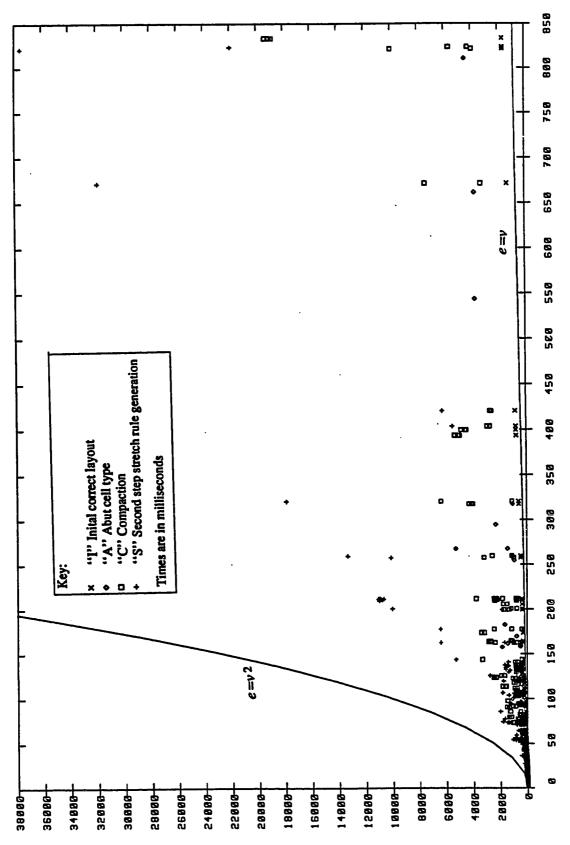

| 5.2a | Edges vs. vertices for "TC" (linear scale)              | 75         |

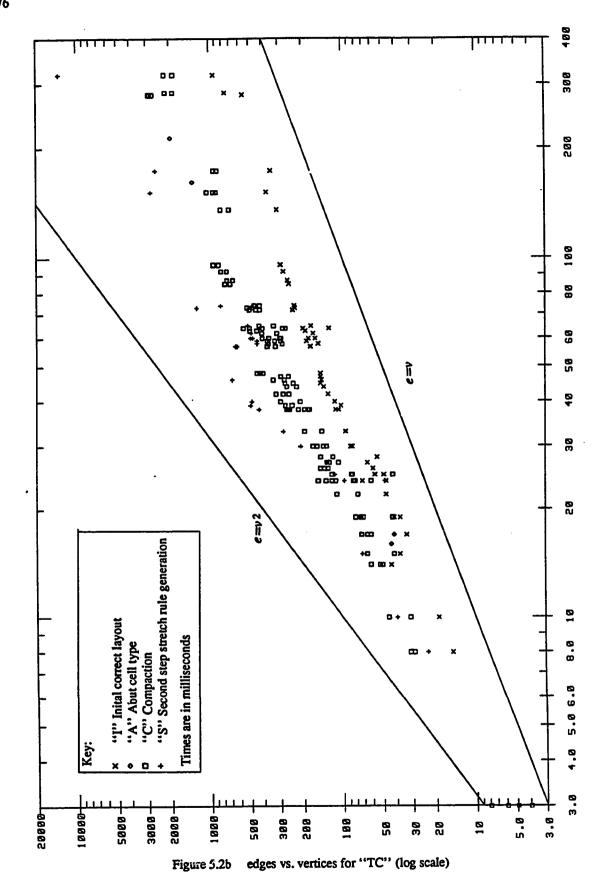

| 5.2b | Edges vs. vertices for "TC" (log scale)                 | <b>7</b> 6 |

| 5.2c | Edges vs. vertices for "FP" (linear scale)              | 77         |

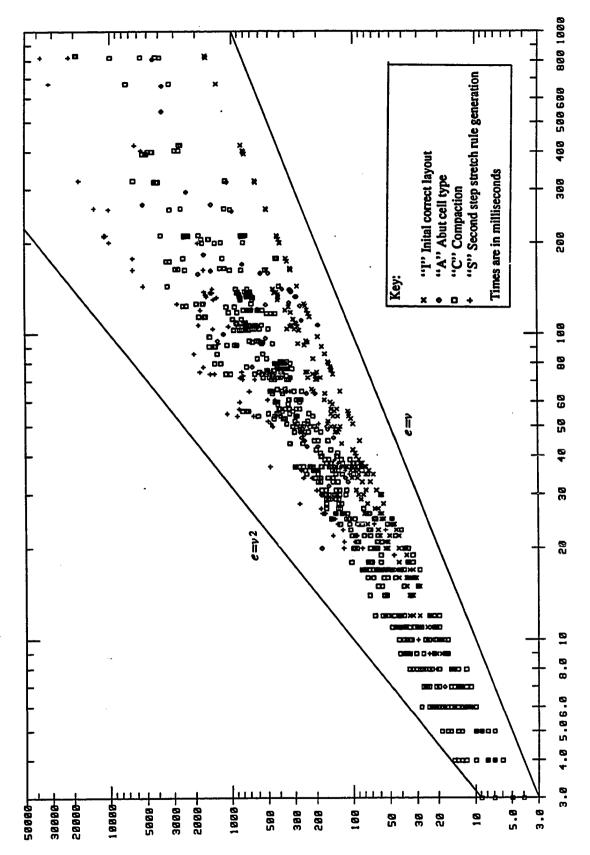

| 5.2d | Edges vs. vertices for "FP" (log scale)                 | 78         |

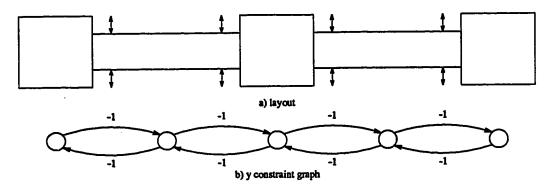

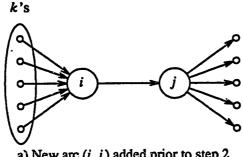

| 5.3  | Cause of large strong components                        | 83         |

| 5.4  | Constraint propagation.                                 | 86         |

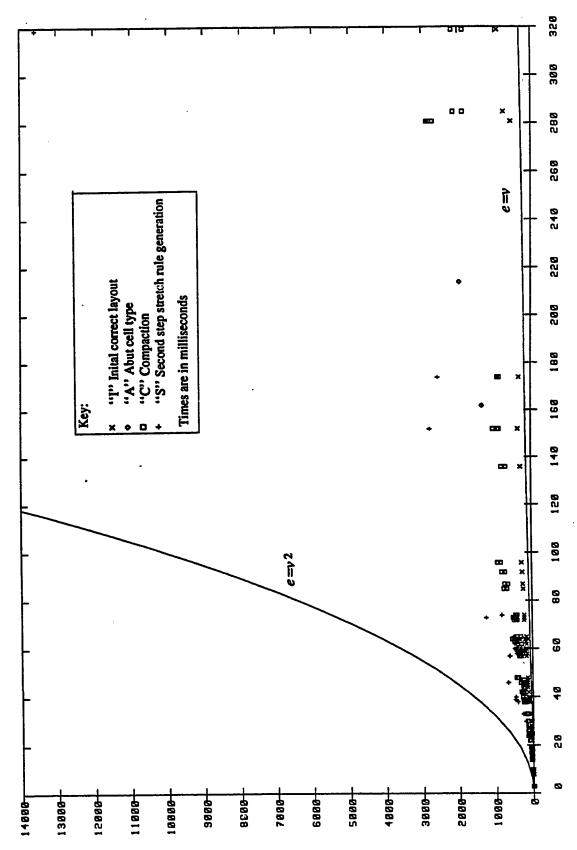

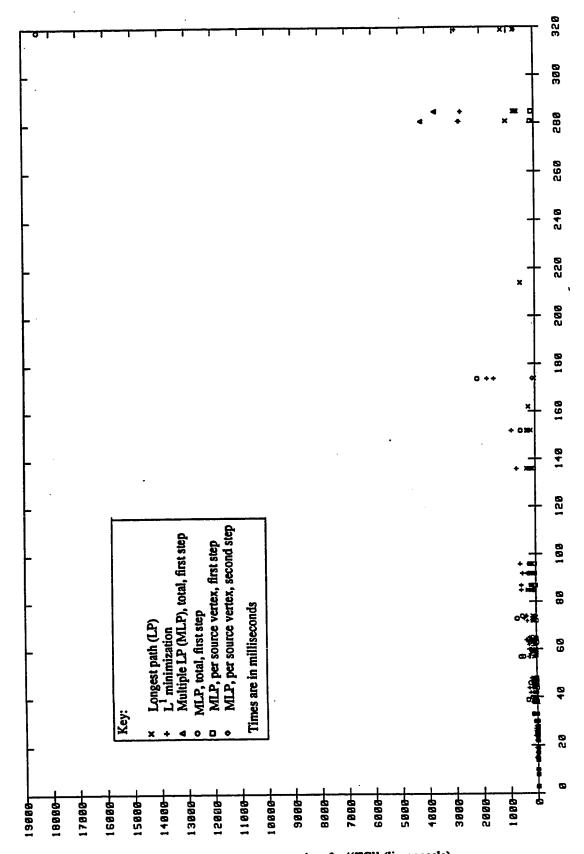

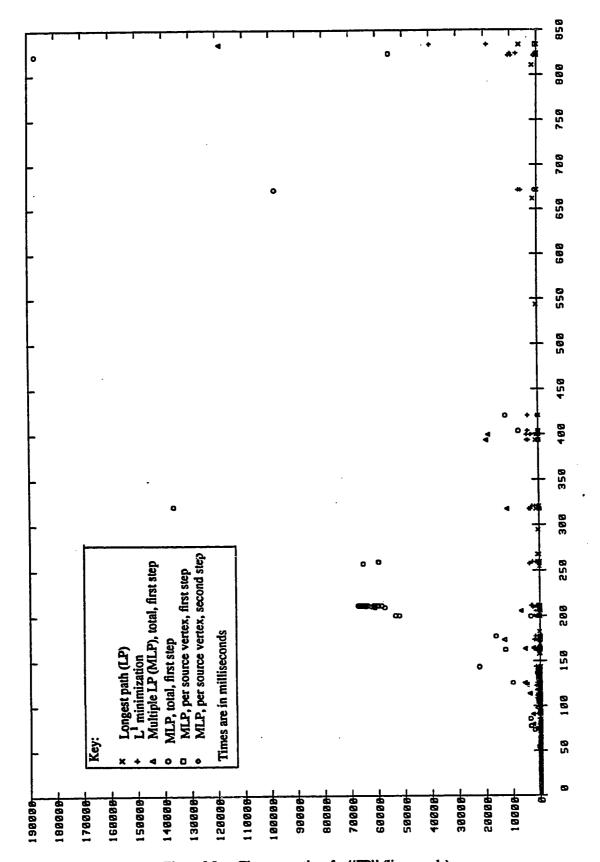

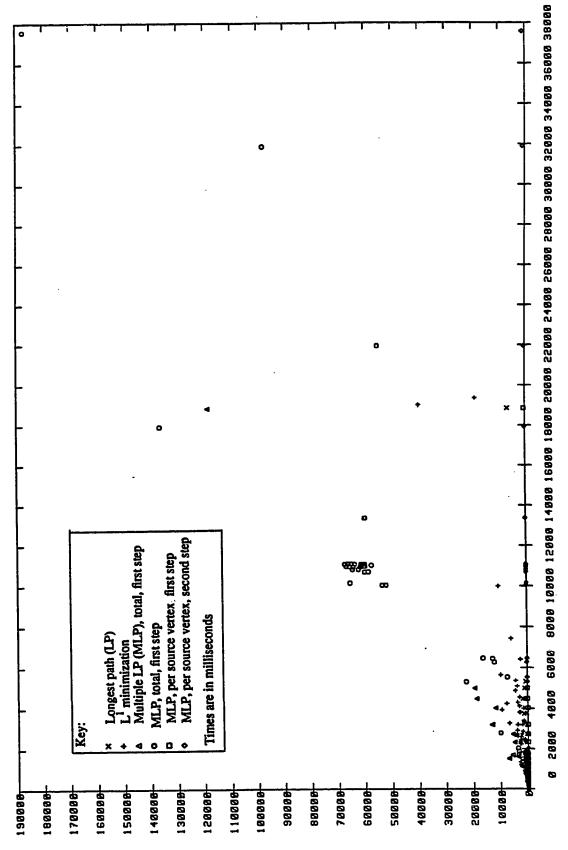

| 5.5a | Time vs. vertices for "TC" (linear scale)               | 95         |

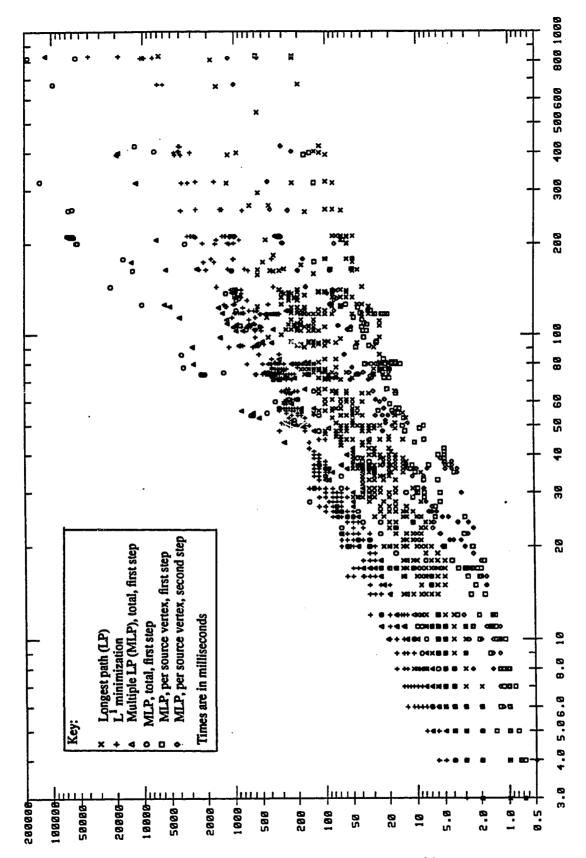

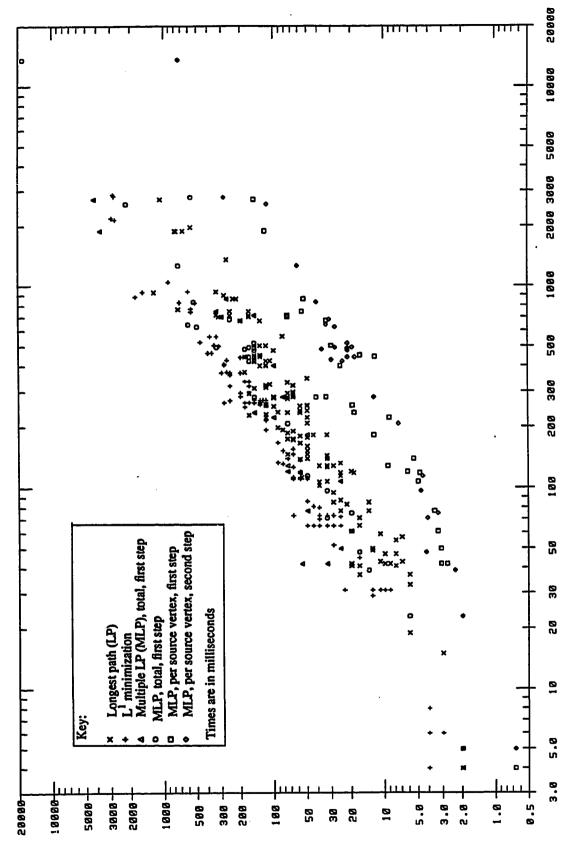

| 5.5b | Time vs. vertices for "TC" (log scale)                  | 96         |

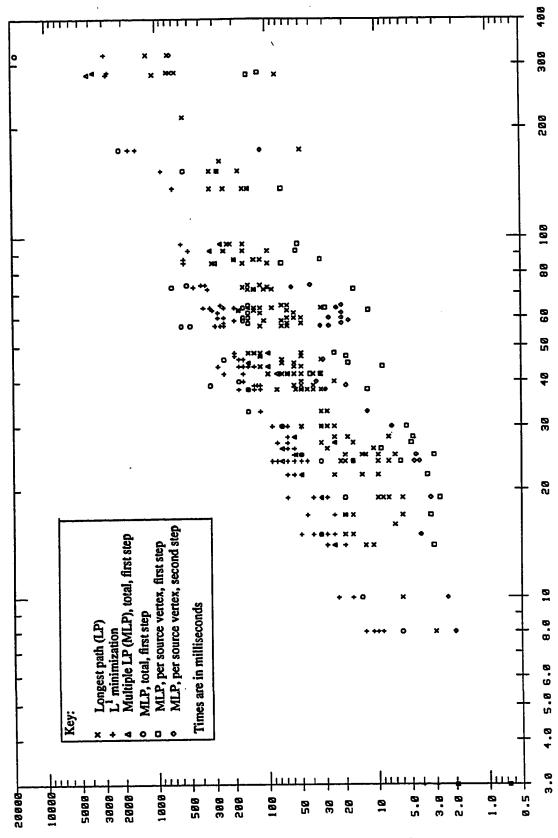

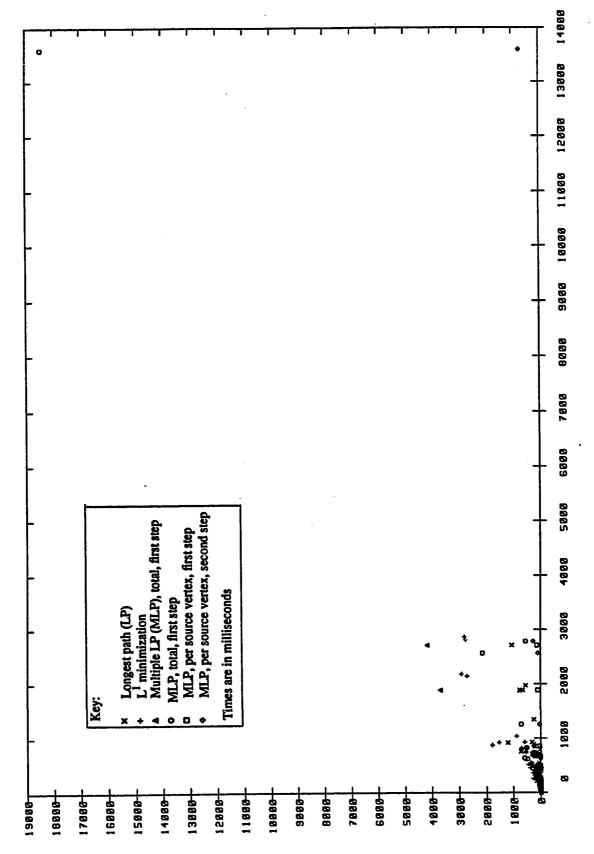

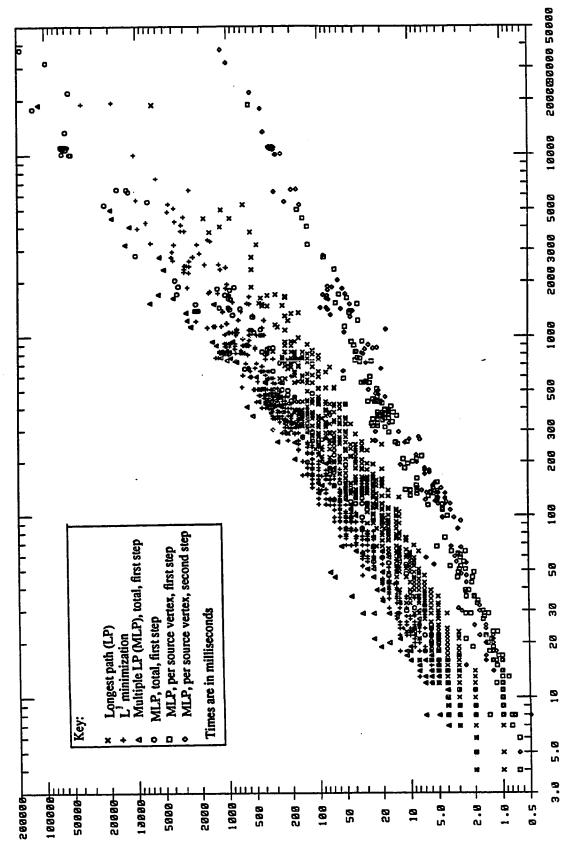

| 5.5c | Time vs. vertices for "FP" (linear scale)               | 97         |

| 5.5d | Time vs. vertices for "FP" (log scale)                  | 98         |

| 5.5e | Time vs. edges for "TC" (linear scale)                  | 99         |

| 5.5f | Time vs. edges for "TC" (log scale)                     | 100        |

| 5.5g | Time vs. edges for "FP" (linear scale)                  | 101        |

| 5.5h | Time vs. edges for "FP" (log scale)                     | 102        |

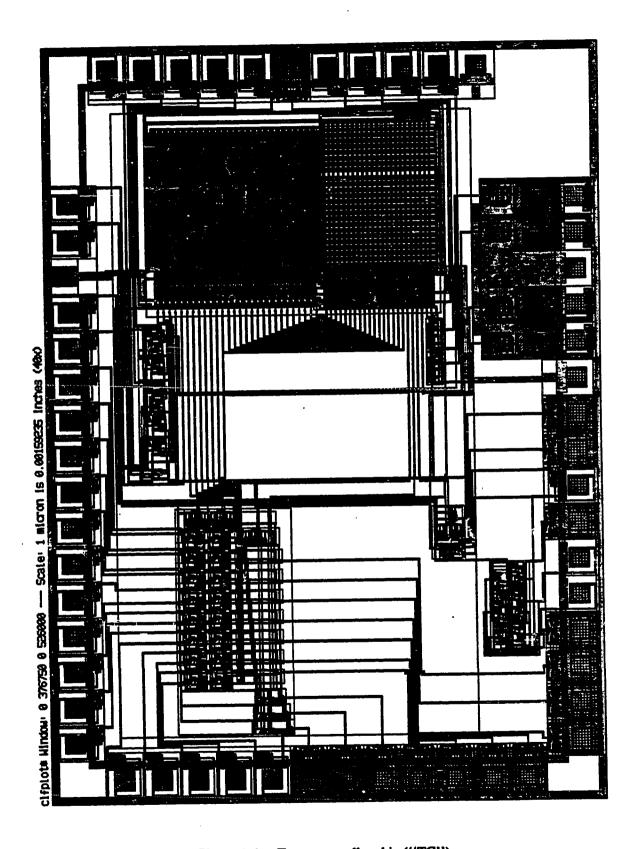

| A.1  | Tester controler chip ("TC")                            |            |

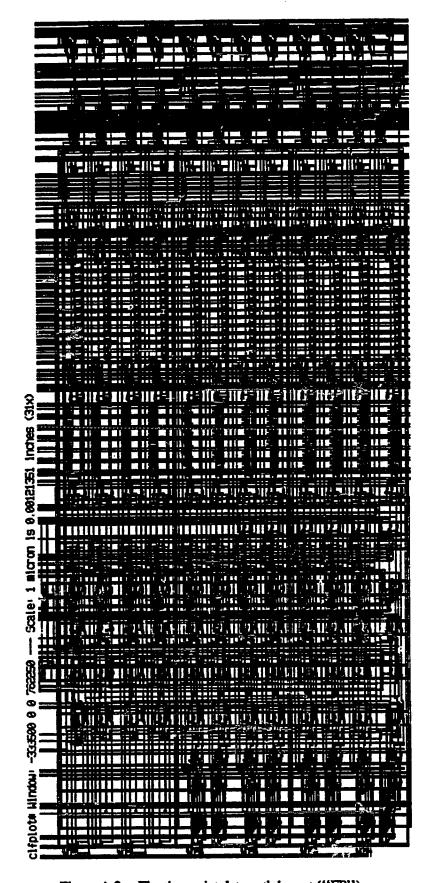

| A.2  | Floating point data path ("FP")                         | 112        |

#### 1. Introduction

Custom integrated circuits offer the highest performance, function density, and lowest manufacturing cost of various IC design techniques. These properties, in turn, allow smaller and less expensive devices to be built. The problem with custom ICs is that their design and verification is difficult, and, therefore, expensive.

One way to make IC design simpler, is to use a *semi-custom* design method such as *gate-array* or *standard cell*, where design consists of interconnecting a number of pre-designed subcircuits. This yields larger chips than full custom, where most of the pieces (subcircuits) have been designed to fit together for a particular chip.

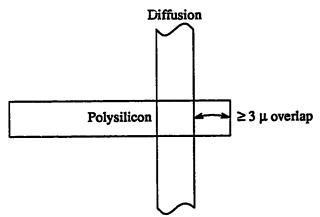

Why is the process of designing a custom IC difficult? There are many reasons, although one of the major difficulties is the process of layout — that is, transforming an electrical description into geometry (the actual "picture" that will go on the masks at fabrication time). Layout is made difficult by a desire to minimize the area while obeying certain design rules. These design rules specify minimal distances between certain geometrical features to ensure manufacturability. For example, in Figure 1.1a, the distance between metal lines might have to be greater than 3µ (microns) to ensure they will not be shorted and the minimum required width of the metal lines might be 4µ to ensure that they are continuous. Another example of a design rule is in Figure

Figure 1.1a Examples of width and spacing design rules

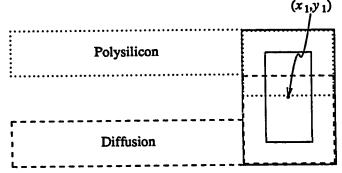

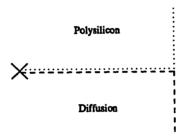

1.1b, where the polysilicon line must extend beyond the gate of the transistor by at least  $3\mu$  to ensure the transistor does not become shorted. Many of the design rules also depend upon whether the objects involved are electrically connected or whether they are intended to be carrying different signals.

Figure 1.1b Example of overlap design rule

Simplified design-rules sets have about two dozen of these rules. Regular design-rule sets are 30 page documents. Constructing a layout that contains over a million objects and does not violate the design rules is a monumental task. Even worse is the task of synthesizing an IC to be of minimal size while obeying these rules. Design rule errors are inevitable.

How do we avoid working with design rules? The designer must be able to express his intent in a manner that has no implicit knowledge or assumptions about the design rules. This is precisely the intent of symbolic layout.

#### Symbolic Layout

In symbolic layout, the designer works with a notation that is representative of, but much more abstract than, the layout that finally appears on the chip. Typically, position information that would require knowledge of design rules is left unspecified, positions are approximate and relative, components and sometimes connection are referred to by names, etc.

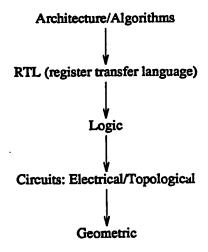

The process of designing a custom IC consists of a series of transformations from a more to a less abstract specification<sup>1</sup>. Figure 1.2 illustrates a typical sequence of such transformations. Different design methods may break the problem into transformations in different ways. Each transformation is expensive and involves some "art" (for a high-quality result).

<sup>&</sup>lt;sup>1</sup> At many of these levels, the specification is not a well defined machine readable notation, but is only an ambiguous human understandable notation.

Figure 1.2 Design Transformations

The last transformation is probably the most tedious since it works with the largest data set. This transformation involves turning an electrical description with some topological information (approximate relative locations) into the geometry that will finally appear on the chip, taking into account the design rules and attempting to minimize the chip area. It should be the first to be mechanized, not only because it is probably the most expensive and tedious, but also is the easiest to mechanize well and will provide a basis for work on automating higher level transformations.

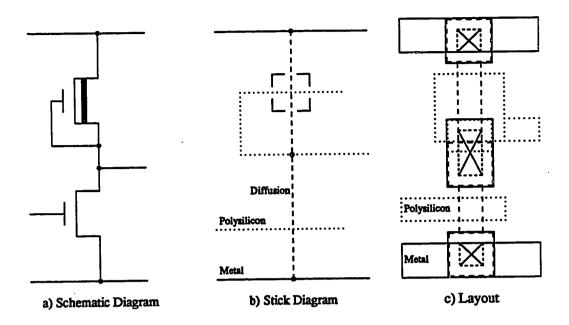

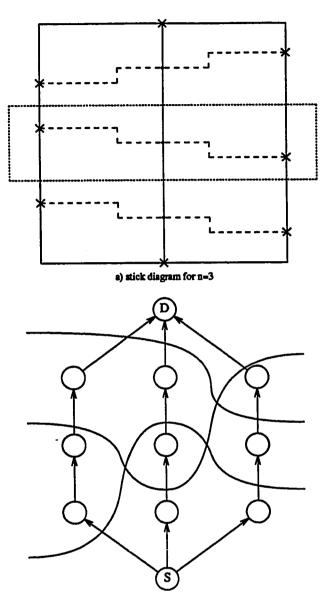

An example of a symbolic notation is *sticks* [Williams 78]. Sticks is a design-rule-independent layout description notation. In sticks, interconnect is drawn as narrow lines, positions are relative, transistors are represented as crossing polysilicon and diffisuion lines, etc. See Figure 1.3b for an example of a stick diagram for an inverter. Figure 1.3c is the layout represented by the stick diagram of 1.3b. Distances in the stick diagram are meaningless as the final dimensions will be computed from the design rules during translation. Sticks notation works best for describing low-level cells consisting of transistors, vias, and wires, but becomes awkward when extended to compose subcells into higher level cells.

Figure 1.3 An NMOS Inverter

## **Symbolic Layout Translation**

Some of the major difficulties of symbolic layout translation for entire ICs are caused by the immense size of the task. Also, when composing a large chip, the designer wishes to describe his layout to the translator in different terms than he would for a lower level cell. Efficiently implementing these higher-level translations is a distinct task.

Translation of stick diagrams or other forms of symbolic notation was attempted many years ago [Williams 78] [Hsueh 79], and much work continues in that area [Weste 81] [Buric83] [Dunlop 81] [Juran 83] [Kedem 84].

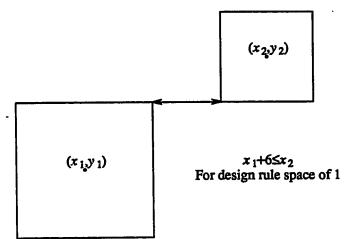

There are still problems, however, that have prevented symbolic layout from becoming a practical tool. Some systems are slow to translate even small cells and are impractical for translation of any significant portion of a chip. Others produce layouts of too poor quality to be used for designing serious chips. Most sticks translators are only designed to produce leaf cells (bottom level cells, which have no subcells), not entire chips, and therefore only produce maximally compacted cells. The user is left with the task of composing the compacted cells to form the whole

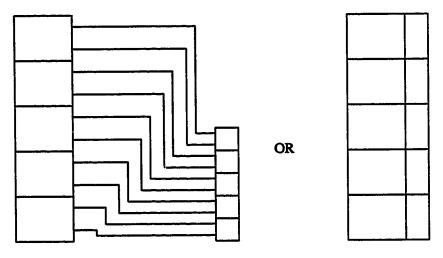

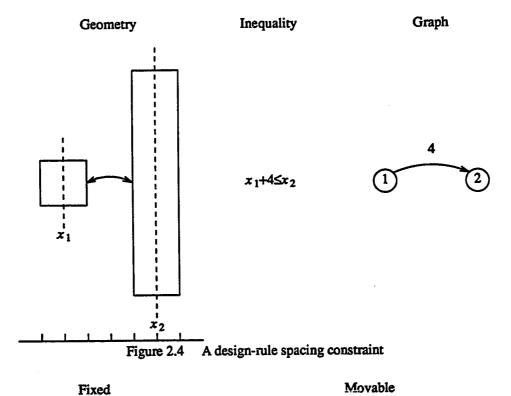

chip. Unfortunately, composing maximally compacted cells rarely produces a minimal sized chip, or even a small chip. In many cases, as in Figure 1.4 it is far more area efficient to compose cells by stretching and abutting them than to wire together mismatching subcells.

Figure 1.4 Advantages of stretch and abut.

CPU time is also an important consideration. Many algorithms are satisfactory for translating a single cell with a small number of elements in it. For an entire chip, which is a much larger problem, not only is the speed of the algorithm important, but also how the CPU time grows with the size of the chip (the asymptotic time complexity of the algorithm). CPU time that is linear in the chip size (area) would be ideal. Many translators' performance are far worse than linear because they contain algorithms that are quadratic, cubic, or even exponential in the worse case.

The quality of the output is another important consideration. While the notion of quality is hard to quantify, suffice it to say that merely producing any correct layout is not sufficient. The translator must produce a good layout in terms of area, wire length, etc., though not necessarily the best correct layout.

#### My work

This dissertation presents a method to make symbolic layout of entire chips practical. While there is no single approach to achieve this goal, I have made a sequence of design decisions that appeared to lead most directly to a practical symbolic layout translator, and have made a number of measurements along the way. Many of the alternatives appeared to have significant problems, but now that one successful course has been charted and measured, exploring these other avenues more carefully should be much easier. In order to test many of the design decisions, and the algorithms they required, a system was implemented that could be used by designers of integrated circuits. This design system, called Lava, has been used by designers who had no part in implementing it.

The next chapter discusses previous related work in symbolic layout translation and solution of optimization problems. Chapter three begins by discussing the goals for an IC description method, then discusses the major features of the new IC description language Lava. The summary is a description of a partially compiled intermediate form upon which the algorithms of the next chapter are based. Chapter four describes the algorithms for generating systems of constraints and optimization problems from the intermediate form. Chapter five characterizes the optimization problems, then presents solution methods based on the characterization and analyzes their performance. Various tradeoffs and alternatives for performance improvement are discussed. Chapter six concludes the dissertation with a discussion of some of the major decisions made in designing Lava and the ramifications of those decisions.

#### 2. Background

This chapter discusses previous work relevant to this dissertation. The first section covers symbolic layout and layout compaction. Many approaches to the layout compaction problem reduce the task to a general mathematical optimization problem. These problems are not unique to the field of IC design automation, but have been studied by many other researchers. The second portion of this chapter deals with the solution of these optimization problems.

#### 2.1. Layout Automation

One of the more tedious and error prone tasks in custom IC design is layout. For well over a decade, researchers have tried to automate this phase of IC design.

Symbolic layout began as simply a shorthand notation for representing layouts: easy-to-write symbols were used instead of combinations of carefully drafted rectangles [Gibson 76], [Barnes 75]. These symbols were drawn on a courser grid than the layout would have been, resulting in some waste of area. The course grid spacing was chosen to ensure the layout contained no design rule errors.

The loss of area due to the course grid can be mitigated by performing automatic *spacing* or *compaction* on the layout. Akers proposed IC-mask layout tools in a style similar to printed circuit board layout, but with some expansion and compaction features [Akers 70].

#### **Sticks**

Williams coined the term *sticks* to represent a kind of symbolic notation that was similar to a sketch the designer might draw of the circuit before laying it out [Williams 78]. The stick diagram is somewhere between a schematic diagram and a layout: relative placement of components and mask layers for interconnect have been chosen, but actual positions and dimensions have not been chosen. He also proposed a program to translate the stick diagram to rectangles and perform the compaction to produce a design-rule-correct layout. For instance, an NMOS inverter would be represented as in Figure 2.1b, while the schematic and layout are as in Figure 2.1a and Figure 2.1c.

Figure 2.1 An NMOS Inverter

#### **Layout Compaction**

The task of layout compaction is to minimize or reduce the area of a layout (or portion thereof) while obeying the design rules and maintaining the integrity of the circuit. Although reducing the area to the absolute minimum is a very difficult problem for any significant layout, simply reducing the area to close to the optimum is practical.

The reason that optimal area reduction is so difficult is that the search space is not convex<sup>1</sup>, meaning that it is not always possible to move smoothly and directly from one legal set of positions to another without passing through illegal positions as in Figure 2.2. The non-convex search space means that there may be many local minima, which make finding the global minimum much more difficult.

A popular technique for compaction is to reduce or minimize each dimension separately, alternating between dimensions until no further improvement is made<sup>2</sup>. Such an approach (called

<sup>1</sup> Precisely, a convex set is defined as a set such that if  $\vec{X}_1$  and  $\vec{X}_2$  are in the set, then  $\alpha \vec{X}_1 + (1-\alpha)\vec{X}_2$ ,  $\alpha \in [0,1]$  is in the set. Here, the vectors represent the positions of all the objects in the layout.

<sup>&</sup>lt;sup>2</sup> Each one dimensional problem (as formulated) usually has a convex feasible space.

Figure 2.2 Non-convexity of compaction

one-dimensional compaction) frequently comes close to the best that may be achieved without reorganizations such as interchanging or rotating components. Another technique, called two-dimensional compaction, moves objects in both dimensions simultaneously [Kedem 84] [Wolf 84].

There are several approaches to layout compaction. One approach involves placing the mask features on a grid or other data structure representing the allocation of chip area, and directly manipulating these features. Another involves generating a system of inequalities representing the design rules and the relationships among the mask features. This system of inequalities, which can be represented as a directed graph, is solved to yield a set of compacted positions for the mask features. In many cases, the geometry manipulation algorithms can be described in terms of graph manipulations.

#### **Shear Line and Virtual Grid Compactors**

Dunlop, in SLIP, places the mask features on a course grid, and then searches for a sequence of grid points crossing the chip (the compression ridge) that are either adjacent, or connected by a shear line, that can all be eliminated without changing the circuit [Dunlop 78]. Shear-line compactors, in theory, are capable of performing almost as good a one-dimensional compaction as the coarseness of the grid allows. Unfortunately, the search for the removable grid points involves exploring many avenues and backtracking, and therefore can be time consuming. As the search time is a function of the number of grid points, a faster compactor requires a coarser grid and therefore can waste more area.

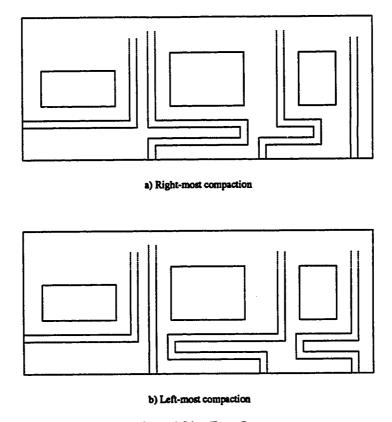

In virtual grid compactors, such as MULGA [Weste 81] [Boyer 83] or VIVID [Rosenberg 84], the layout is densely placed on a grid without regard to design rule spacing. The grid is then scanned to determine what spacing between each pair of grid lines is necessary to satisfy the design rules. For larger layouts, there are more unrelated components on a grid line, yet all must be moved together to account for the worst case spacing and cannot be moved relative to each other. For example, a virtual grid compactor could not achieve the following compression (in x), because "A" and "B" are on the same virtual grid line:

Figure 2.3 An impossible compaction

This inflexibility of virtual grid compactors can exact a large area penalty in large layouts. A more flexible compactor might be able to produce the drawing on the right.

#### **Constraint System Compactors**

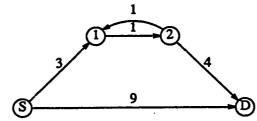

One of the earlier compactors to build a system of inequalities was Hsueh's CABBAGE [Hsueh 79]. In Cabbage (as in many others), the constraints (inequalities) arise only from design rule spacing constraints as in Figure 2.4. Because the only user constraints are lower bounds on distance between features, Cabbage's constraint graph is acyclic and can therefore be solved for longest paths in time linear in the number of edges. Upper bound constraints are only checked, but not used to determine the solution.

A penalty of acyclic constraint graphs is that connections must be made to fixed locations on a component rather than being allowed to slide over a larger permissible area as in Figure 2.5. Hsuch uses a form of automatic jog introduction to mitigate the area costs of this rigidity.

Similarly, Mosteller in REST builds an acyclic constraint system (again, except for user-provided upper bound constraints), but does no automatic jog insertion [Mosteller 81]. Dunlop in SLIM [Dunlop 81] also builds an acyclic constraint graph, but does automatic jog insertion and

uses a variety of methods for reducing the difficulty of compacting large layouts. McGarity claims area performance of SLIM is poor [McGarity 83]. ALI uses a longest-path constraint graph where all edges have a non-negative length [Lipton 82]. Such a graph cannot have non-trivial cycles and is solvable in linear time.

Both Schiele and Kedem use cyclic constraint graphs to represent flexible connections [Schiele 83], [Kedem 83] [ Kedem 84]. Schiele is also minimizing wire lengths in his compaction algorithm.

Kedem is trying to minimize area by compacting in both x and y directions simultaneously using an integer programming formulation to couple the problems. This simultaneous x and y

compaction is called two-dimensional or 2-D compaction, as opposed to 1-D, which compacts in each dimension sequentially. While 2-D compactions could potentially perform better than 1-D, Kedem offers no data comparing either performance (expected to be better) or CPU time (expected to be worse). Sastry shows that optimal 2-D compaction is NP-complete [Sastry 82].

#### 2.2. Optimization algorithms

Most of these symbolic layout translators make use of the solution of some kind of mathematical optimization problem to perform the compaction operation. Most of these mathematical optimization problems have had applications in other fields than integrated circuit layout, and therefore have been well studied.

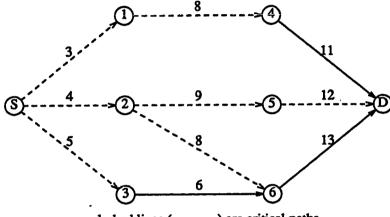

The graph-based symbolic layout tools compile the layout problem into a mathematical optimization problem, usually a longest-path problem. The longest-path problem is stated as follows: Given a set of inequalities

$$\left\{x_i + C \leq x_j\right\}$$

find the minimal difference between a pair of distinguished variables:

The source and sink variables might correspond to the positions of the left and right edges of the cell being compacted, respectively (or bottom and top). This problem corresponds to finding the longest path in a graph from a source vertex to a sink vertex, where the arc lengths are the constants in the inequalities.

In practice, the result desired is not just the longest path from source to sink, or its length, but the length of the longest paths from the source to all other vertices. Fortunately, this information is what is most often computed by the longest-path algorithms, or it is easily computable in linear time from information available.

If the arc lengths are negated, this problem becomes the shortest path problem, an isomorphic, and more frequently studied problem. To be solvable, the graph must has no positive weight cycles (infinite longest path) and must be connected (no path).

#### Acyclic longest path

The simplest of the optimization problems is the longest-path problem when the constraint graph is acyclic. This problem can be solved in time O(v+e), where v is the number of vertices and e is the number of edges. These correspond to the number of variables and inequalities, respectively. The algorithm traverses the edges of the graph in topological sort order, which may also be determined in linear time, propagating the longest-path lengths onto the vertices.

#### **Unrestricted Longest path**

Slightly more difficult to solve is the longest-path problem where the constraint graph may have cycles. For there to exist non-trivial cycles, negative arc length must be permitted. Since the longest-path problem is a subset of the linear programming problem, the simplex method [Dantzig 63] could be used. As linear programming problems are quite a bit more general than longest-path, the simplex method is overkill and costs far more memory and CPU time than is necessary.

If an initial feasible (though not necessarily optimal) solution is available, it can be used to solve the problem in  $O(e \log v)$  time [Johnson 73]. Johnson transforms all the variables (in the corresponding shortest-path problem) by the amount of the initial solution, resulting in a shortest-path problem with non-negative arc weights, and then uses a priority queue to traverse the edges in proper order to solve it. By making portions of his algorithm adaptive he is able to achieve a slightly better bound than mentioned above.

The Floyd-Warshall algorithm [Floyd 62] computes longest paths without an initial feasible solution, computes longest paths for all pairs of edges, and, unfortunately, requires  $O(v^3)$  time.

Mathews used a relaxation-based algorithm to solve the longest-path problem [Mathews 81]. He found the time bound to be  $O(B \cdot e)$ , where B is the number of "back-edge" trees in the graph. Very similar are D. B. Johnson's "Arc set partition algorithms" [Johnson 73]. Liao uses a relaxation method that relies on the existence of an initial feasible solution [Liao 83].

A network flow formulation can be used to solve the longest-path problem. Kennington and Helgason describe a "Primal Simplex method on a graph" suitable for solving the network flow problem [Kennington 80]. Discussion of empirical performance of network flow as applied to IC layout may be found later in this dissertation.

#### Multiple longest paths

Some symbolic layout systems require the longest paths from multiple source vertices. If all vertices were used as source vertices, this problem would become the all-pairs, longest-path problem. The simplest, the Floyd-Warshall algorithm  $(O(v^3))$  mentioned above, computes all pairs. D. B. Johnson has an all-pairs algorithm with a somewhat better time bound. In either algorithm, far more data than is needed by Lava is being computed, with the excess discarded. Mathews found it faster to compute individually the longest path from each source vertex, using results from the previous vertex to accelerate the speed of convergence [Mathews 81].

Reduction of wire length can be useful as a secondary objective during compaction. W. L. Schiele presents a method of reducing wire length [Schiele 83], although it is not clear whether a minimum is achieved. A method of minimizing wire lengths based on a network flow formulation is discussed later in this dissertation (§5.2).

#### **Summary**

In this chapter, I described some of the approaches that have been taken to automate the task of IC layout. First, a symbolic representation is used to ease the task of describing the layout. Because a direct translation of the symbolic representation leads to a waste of area, layout improvement called *compaction* is employed. Many of the compaction algorithms construct a system of linear inequalities and minimize some objective function subject to those constraints. In the second part of this chapter, I describe some of the existing optimization algorithms that are well suited to the optimization problems that result from symbolic layout translation.

### 3. Lava: A New Layout Description Method

A new method of describing IC designs was developed to give the designer much greater expressive power than previous layout description methods. In this chapter I will describe in general terms some of the features of the new language, Lava, to motivate the work described in the next chapter. After describing some of the goals and major features of Lava, I will describe the primitive objects and operations of the language. Finally, I will describe a canonical intermediate form that is used as input to the algorithms of the next chapter.

#### 3.1. Goals and Specifications for an IC Description Method

This section describes the motivation behind the design of the IC layout language Lava. I also will list some general goals for IC descriptions, and then give a set of design specifications for an IC layout language, while relating them to the goals.

Modern programming languages embody solutions to problems of managing complexity and representing structure. Similar problems exist for the task of describing hardware. In the design of Lava analogies with programming languages have proved very useful and were frequently used as a guide.

#### Goals

A high level of abstraction is one way to provide the designer with some "leverage" over the design. By using automation to avoid details, the designer can potentially gain much more leverage than if he had to work with the details, even with machine assistance. Potential benefits include reduced need for design auditing tools, reduced errors, and relative design-rule independence of the design. The programming language analogue would be high-level programming languages.

At odds with the goal of a high level of abstraction is that of providing a generality of application. Many special purpose layout tools have been constructed that are very powerful, but good only for a narrow range of applications. In contrast, my objective is a tool that could replace

current IC layout tools, produce any topology that the designer intends, and would not restrict the design methodologies available to the designer.

Also conflicting with the goal of a high level of abstraction are the designer's goals of area efficiency, speed, etc. The design tool must have an acceptably small performance penalty for its use.

The IC description should be concise in order to be easier to read, write, and modify.

# Design specifications for an IC description method

Given these general goals, there are many ways to design an IC description method. The following are the important features of Lava.

Hierarchy has long been used to deal with the complexity of programs, ICs, etc. because it reduces the quantity of information that must be manipulated at any given time. As ICs are organized and designed in a hierarchical fashion, an IC description method should be capable of representing this structure. A hierarchical description also reduces the effort required for programs that implement the design description.

The notion of parameterized cells is another useful idea borrowed from programming languages. It allows variants of a cell to be created and used without the user dealing with all of the details of its construction. These parameters can be used for modifying the size of devices in a cell or they can be used to control repetition and conditional inclusion, thereby making it possible to specify a generic cell that can generate variants of a cell. Typical uses might be for specifying the width of a register, or for selecting one of a number of variant cell types, such as the least significant bit versus a center bit of an adder. Parameters lead to more concise descriptions and keep the designer from having to respecify nearly identical objects. The elimination of duplicate similar cells makes bug fixes much simpler — one only needs to fix the generator rather than all the versions of the cells.

Another simplifying concept is the use of wire aggregates. Arrays and records are constructs in programming languages for grouping together related variables and manipulating them

as one entity. A similar concept can be very useful for describing hardware. Busses may be described as an array of connections or wires; a collection of control lines not part of a regular array can be thought of as a "record" of wires. In Lava, these records are called bundles. A bus including control lines would be a bundle that includes an array. Connection between such aggregates may be made in a manner analogous to plugging together multi-pin connectors (such as the connection between a terminal and a computer), provided that the shape and size of the connectors matches. Aggregates allow an IC description to be much more concise by hiding details that are unimportant. At a high level when a connection is been made between two blocks, you know that the left signals of block A connect to the right signals of block B, but the names of the individual connections are irrelevant. After all, when you last plugged together a multi-pin connector did you think about each of the many connections being made?

In Lava, the electrical circuit is the fundamental method of description. It is specified explicitly and unambiguously using a variety of language features included solely to make the electrical specification convenient and concise. Since the electrical circuit is one of the levels of specifications that the designer works through on his way to designing the IC, he should specify the electrical description directly rather than indirectly through a topological or geometric description.

In a utopian world, the electrical specification is all that would be necessary to produce an optimal layout. In reality, a better layout can be produced if the designer provides topological or geometric information such as the orientation or relative position of a component, or the width, layer, or route of a wire. Such information will be referred to as a hint, that is, information that aids the compiler of the description to produce a layout from an electrical description. Lava contains a number of variants on the method of description, the major difference being the types of hints required. When the electrical specification (or a higher level) is the primary specification of circuit behavior, there are fewer conversion steps to be performed by the designer, and topological and geometric hints need be specified only after the circuit (or chip) has been completely electrically specified and a functional simulation performed.

A Lava IC description does not contain assumptions about the geometric design rules. Assumptions about the form and specifics of geometric design rules should not be a part of the description that the designer provides. The design-rule-independent description also precludes the specification of most physical dimensions, as dimensions are almost always a function of design rules. There are many benefits of a design-rule-independent description, but one of the most significant is reducing the amount of detail the designer must specify. Since the design tool now has the responsibility for maintaining design-rule correctness, it also has the power necessary to do some layout minimization and other optimizations, which will be discussed later.

A design-rule-independent description allows the design rules to be changed with little effort, thus permitting a great deal of portability of designs among fabrication facilities. Universal design-rule sets, whose aim is also to increase portability, rely on the assumption that as the technology improves, it improves uniformly for all the design rules so that designs can simply be scaled for different fabrication facilities. This assumption is poor, because different design rules have shrunk at different rates. For example, recently minimal transistor dimensions have been reduced far more than minimal line widths. While scaling still works, the scaled design gradually becomes less optimal.

Currently, design tools that offer the designer some degree of automation (i.e., do more than just drafting) to aid him in IC layout often do not produce an optimal result. If the layout is not satisfactory, the designer is faced with the choice of putting up with the tool and layout or using less automatic methods. Rather than abandoning this automation, the designer should be able to provide hints, or otherwise constrain the design tool, to produce a result more to his liking. Allowing the designer to add more and more constraints results in a continuum from automatic to manual design. This continuum is important for allowing the designer to produce layouts with an acceptably small area and performance penalty.

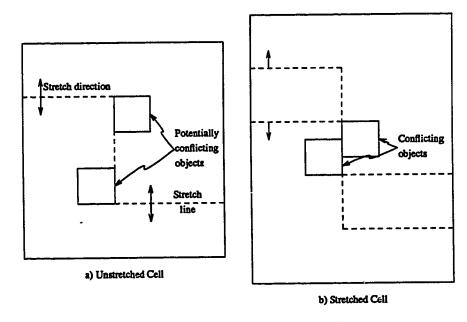

Cell stretching and pitch matching are useful cell composition techniques for achieving efficient designs. In order to make cell stretching easy for the designer, he should not have to specify the rules by which the cell stretches. Computing the set of rules that guarantee that a

cell's geometry remains design-rule correct as it is stretched in both dimensions is a tedious and error-prone task for a designer. Computing this set of rules can better be done by machine. Automatically generated stretch rules allow the designer to work at a higher level of abstraction and make the description more concise. Because the design tool has the power and responsibility for design-rule correctness, it is capable of generating stretchable cells, as will be shown in the next chapter.

#### Form of the description

The previous section described some of the capabilities of the Lava language; this section will discuss some of the implementation decisions. There are a number of choices to be made when you create a new IC layout language. While I do not claim that there is a correct or best answer, I will justify the choices I have made. In general, Lava uses the form that was the most general and put the fewest restrictions on what could be represented.

The first major question was whether to use a graphical input form or a textual language as the basis for Lava. A textual description was chosen for several reasons. First, there are many concepts that are easy to express textually, but are very difficult to express graphically. For example, the ideas of repeating an object N times, where N is a parameter yet to be specified, or of conditional inclusion, where different objects are placed in the layout depending on a parameter, are more naturally expressed textually. However, graphics does seems better suited for expressing specific instances of the more general specification.

Probably more important, as long as the textual description is at least as general as the graphical description, a preprocessor can be written to manipulate the latter to produce the former. In fact, such a program has been written (called SEDIT [Burns 82]) to manipulate graphically portions of layout descriptions and produce a textual equivalent. It has proved very useful, but its weaknesses are just where one might expect: the concepts for which the graphical description does not have sufficient expressive power, such as iteration, wire aggregates, and conditional inclusion.

Finally, developing a graphical description entails spending a large amount of time developing a graphical user interface. Eventually, graphics will be important in the overall solution to the problems of IC layout, but it is not essential for exploring what fundamental operations and facilities are needed and how to implement them. Therefore, the design of a graphical user interface was deferred.

Another major design decision was whether to make Lava a stand-alone or an embedded layout language. Lava is a stand-alone language, not an extension of an existing programming language. The purpose of this project was to try to understand what facilities are necessary to specify ICs, and a stand-alone language is superior for that purpose. If some feature is missing, the IC designer cannot fall back on the surrounding programming language, but must complain to the language designer. The problems become obvious this way. Many embedded design languages are merely facilities for writing design tools, but not design tools. The design decision is: What is the language with which the designer describes his design? not What is the language with which to write a design tool? Creating a stand-alone language is not giving up anything, as the stand-alone language can later be embedded in a conventional programming language by including statements or procedure calls to generate the stand-alone language statements.

The Lava input is a concise, powerful notation for hierarchical, design-rule-independent, textual IC description. Major features include an electrically explicit, but geometrically ambiguous, description supplemented with *hints* to provide a continuum from automatic to manual translation.

#### 3.2. Lava Overview

#### Organization

In Lava, an IC layout is described as a hierarchy of cells. A cell may recursively contain subcells, and appear multiple times in a layout, but may not intersect another cell. A cell that contains no other cells is called a *leaf* or *leaf-level* cell. From an electrical view, cells and subcells could be called circuits and subcircuits. A cell may have a number of connections points

called terminals. A logical grouping (by means of bundles or arrays) of one or more terminals is called a pin. Physically, each cell has an inviolate rectangular boundary enclosing transistors, wires, vias, subcells, etc. The terminals appear only on the boundary. A pin is a logical entity and has no physical existence independent of the terminals of which it is composed.

Cells in Lava may have *parameters*. A parameter is numeric information provided to a cell by the cell above it (its parent in the hierarchy) in order to customize the cell or its subcells. The customization is done by controlling repetition, subscript indices, or conditional inclusion. There is no information returned (passed up the hierarchy) that is under control of the designer.

#### Features common to most cell types

Most cell types are similar except for the hints. What follows is a description of those features in common among most all cell types. I will discuss *objects*, their interconnections, and then a few points of notation.

#### **Objects**

Cells are composed of interconnected objects. There are two kinds of objects: primitive components (such as transistors, loads, or vias), which are defined in a technology database, and cell calls (the creation of an instance of another cell). Depending on the component, there may be optional information included: a sub-type (such as transistor type), parameters (such as dimensions or aspect ratio), transformations (such as rotations and reflections), and various hints as required by the cell type. Instances of objects may be given names, which are used to refer to that object instance.

Cell calls can either be single cell calls or iterated cell calls. A single cell call causes an instance of a subcell to be included in a cell, gives local names to each pin (group of terminals) of the subcell, and provides values to the parameters of the subcell (from expressions in the cell call). Transformations and hints may be included, as with primitive components.

An iterated cell call additionally includes a count, a direction, and a description of how adjacent faces are to be connected, and produces a linear array of identical cells. (The iterated

call is not the only way to generated an array of cells. The foreach construct (see section on notation below) may also be used to generate multiple single cells calls.

# The wiring operator and wire expressions

Lava is an expression-based language where the existence of an expression causes an object to appear or a connection to be made. Central to wire expressions is the wiring operator.

Lava's method of description is primarily electrical; consequently, interconnections are specified electrically, while the geometric or topological aspects are derived from the electrical description as much as possible. Hints are used to supply physical information that cannot be determined from the electrical description. The interconnections are specified by a symbolic equivalencing of names or expressions that represent nets or connection points. The expression might refer to a particular connection point on a primitive component or a pin on the cell boundary. An electrical description that is independent of physical information allows the circuit to be designed and its description to be debugged prior to layout (by means of functional simulators and circuit-analysis tools). The equivalencing is done by an operator "#" which will be referred to as the wiring operator, but it is important to remember that the operation actually being performed is to make its operands electrically equivalent, and may or may not cause a wire to be generated.

There are several types of permissible operands for the wiring operator. For one, a pin of the cell being constructed may be equivalenced. These pins are known as *formal pins* in analogy to formal parameters of programming languages. Another is a terminal of a primitive component. Such a terminal is just a reference to the component, possibly with a qualification to specify which terminal if the component has multiple terminals. An entire wire expression may itself be used as an operand in another wire expression. Lastly, an otherwise unknown identifier is simply equivalenced to the other operand and may then be used elsewhere in the cell to represent those net(s). What about connections to the pins of subcells? Subcell calls have implied wiring operations for each of the pins. Thus, an identifier used as an *actual pin* name (analogous to an actual parameter in programming languages) becomes synonymous with the

subcell pin. This same name may be used in another subcell call, making a connection between the cells without introducing additional names or statements. More on this technique appears in the section on notation.

In addition to wiring together individual nets, the wiring operator is capable of wiring together corresponding elements from aggregates of nets. These aggregates are the hardware designer's equivalent of the programmer's arrays and records. In Lava they are called arrays and bundles, respectively. Roughly, an *array* is a collection of connections or nets where the individual elements are of similar structure and are accessed by a numerical index, whereas a *bundle* is a collection of inhomogeneous connections or nets accessed by element name. Either a bundle or an array may have bundles or arrays as elements.

To prevent unintentional or nonsensical connections, the wiring operator only permits wiring together things of identical structure. If the operands are arrays, they must be of the same size and the elements must be of the same structure; if the operands are bundles, there must be the same number of elements, and the corresponding elements must be of the same structure. Essentially, if we are looking at the trees corresponding to the aggregate's structure, the trees must have the same size and shape.

An aggregate's structure may be defined in several ways. First, pins of cells may be explicitly given structure in the pin declarations. Second, the structure of terminals on primitive objects is known (scalar) and the structure of pins on subcells is known (from the subcell pin declarations). Third, wiring to something of known structure will propagate the structure information to an identifier of unknown structure. Since subcell calls have an implied wiring operation, they are just a special case of this structure propagation. Thus, an element selected from an aggregate also has known structure, and therefore may be used to define the structure of something else. There are some examples of this kind of structure inference in the next section. Finally, an iterated cell call creates arrays whose elements have the structure of (and are wired to) the pins of the subcells.

## **Notation**

A design in lava consists of a set of bundle definitions and cell definitions. The bundle definitions give a name to a bundle type so that pins throughout the chip can be conveniently given the same structure. A cell definition consists of a cell header, pin declarations, and the cell body. The cell header and pin declarations name the cell, the pins, and the parameters, and specify properties (including the structure) of pins.

The cell body is a block of statements. In Lava, the order of statements within a block is irrelevant, as they are not executed sequentially (or even executed) as they would be in a programming language.

The if statement chooses one of two blocks of statements based on the value of an arithmetic expression, which may be a function of parameters. The foreach statement causes a block of statements to be reproduced some number of times, possibly with a variation. The number of time the block is reproduced can be a function of the cell's parameters. An index variable is set to a different integer for each copy of the block of statements. It can be used within the block in arithmetic expressions just as cell parameters are used. These arithmetic expressions can be used as parameters in subcell calls, to control if or foreach statements, etc. For example:

```

foreach x to 5 {

if(x < 3 || x > 4) {

cell_call(pin; x+j);

} else {

other_cell_call(pin2; x);

}

}

```

is equivalent to:

```

cell_call(pin; 1+j);

cell_call(pin; 2+j);

other_cell_call(pin2; 3);

other_cell_call(pin2; 4);

cell_call(pin; 5+j);

```

Lava is an expression-based language, and the remaining statements are of one of two types of expressions: instance expressions or wire expressions. As with operators in arithmetic

expressions, Lava's instance or wire operators have precedence and associativity, which may be modified by parentheses. What is different is that the expressions do not have values, but express relationships. Most binary operators say something about the relationship of things referred to by their operands. If an expression is being used as an operand, it refers to one, or the other, or some combination of its operands.

In general, instance expression cause objects to exist, and describes physical (geometric or topological) relations among them, while wire expressions denote electrical relationships between these objects (connectivity).

The simplest examples of instance expressions are cell calls and declarations of primitive objects (such as transistors). There are operators such as above or "|" (abuts) that express physical relationships. The objects referred to in an instance expression can be given a name, which can be used to refer to them elsewhere. This name is called an *instance name*. For example:

name = instance-expression

This instance name may be used wherever an instance expression is required. Instance names may also be subscripted:

insname [5] = instance-expression which is useful for working with iterated structures.

Simple examples of wire expressions are pin names (from the cell header), or actual pin names (from a subcell call). The most important wire expression operator is the wiring or equivalencing operator "#". It connects or equivalences the nets of its operands. When used within another wire expression, the nets that are being referred to (i.e. its "value") are simply those of one of its operands. If the wire expression refers to an array or bundle, subscripting or qualification, may be used to select parts of the aggregate. This selection is done with square brackets "[]" or dot "." as in many programming languages. To connect to a primitive

<sup>1</sup> Which one only matters in cell types where "#" produces wire segments rather than net lists. In such cases the "value" is the right operand, and "#" is left associative. This convention is arbitrary but will cause the sensible result for expressions such as a # 5 # c

component, an instance expression referring to a single component may be used as a wire expression if the component has a single net (a # via br) or with qualification if a multiple-terminal component (a # tranname.gate). The following sample wire expression illustrates some of the above features:

((busa # busb).data # aluin)[1] # highbit

Where busa and busb are bundles that have an element data which is an array of the same

size as aluin.

# Cell types and the hints they require

The electrical circuit alone is not enough for the designer to specify the layout that he desires to produce. Lava's compilation algorithms require an initial, almost correct, though not necessarily optimal, layout. The information from which this layout is determined varies according to cell type. Additional information such as the relative location of components, the layer or width of interconnect, etc., may be necessary. These hints will be described in this section for each of the three cell types: Stix, Abut, and Externals cells.

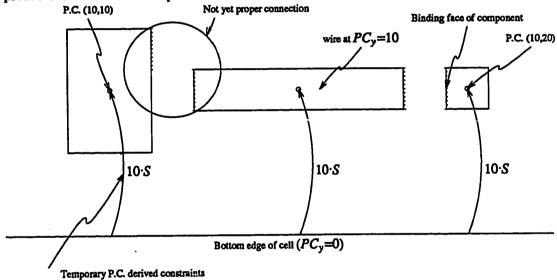

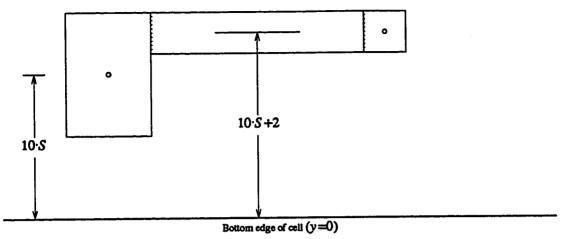

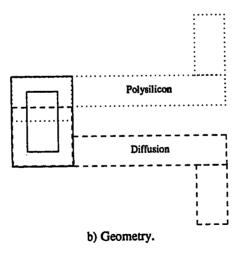

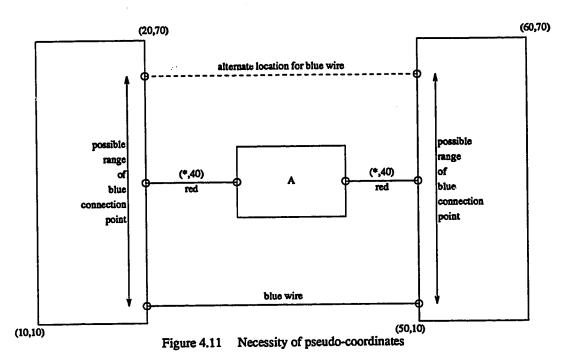

The purpose of the Stix cell type is for designing lower level cells where the designer has a specific idea of the layout he desires, and wishes to have a high degree of control over the locations of components and wires. In this cell type, relative positions are specified by giving each of the components *pseudo-coordinates*. These pseudo-coordinates merely establish a relative position; the magnitude has no meaning except in comparison with other coordinates. For example, the coordinates from a stick diagram would serve well as pseudo-coordinates. Because subcells may have several connections on a side and are potentially stretchable, rather than a pseudo-coordinate representing the location of its center as with other components, the subcell requires pseudo-coordinates representing each of the edges<sup>2</sup>.

In Stix cells, wires generate single wire segments with the color (layer), width, direction and pseudo-coordinate provided as hints. In many cases the color, pseudo-coordinate, and

<sup>&</sup>lt;sup>2</sup> Provided as a pseudo-coordinate representing the lower left corner and a pseudo-size.

direction may be inferred from the adjacent components. The width will default to the minimum width.

Other hints that may be specified are transformations (rotations and reflections) and user constraints. User constraints are constraints on the relative position of objects. These differ from pseudo-coordinates in that pseudo-coordinates only provide an initial relative position of objects, which may change during compaction, whereas constraints always remain in effect.

The need for pseudo-coordinates in the Stix cell type makes the use of wire aggregates (bundles and arrays) sufficiently awkward to be not very useful. A distinct pseudo-coordinate needs to be given to each element of the aggregate. When several elements of a bundle or array are connected to the same subcell, pseudo-coordinates cannot be inferred and must be provided manually.

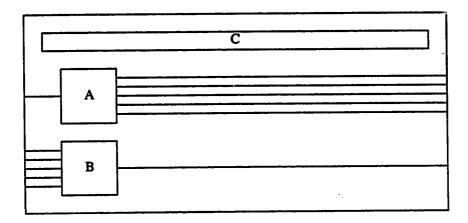

The Abut cell type is intended for the design of larger cells that are composed entirely of subcells. The principle distinction between Abut and Stix cell types is the manner in which the initial positions are specified and a restriction on the components allowed (only subcells in Abut).

In the Abut cell type, the area of the cell is entirely tiled by the subcells and all connections are made by abutment. The initial positions are specified by the operators such as left of, which specifies that a cell or group of cells is to be to the left of another cell or group of cells. Another set of operators, of which abuts left of is an example, specifies that connections between the cells (or groups of cells) are to be made by abutting and that the cells are to be adjacent<sup>3</sup>. Because of the tiling, no pseudo-coordinate, pseudo-size, or wire direction need be specified. Also, because the only components are subcells, the wire layer can always be determined from the subcells. Wire widths and transformations are hints that may still be specified.

The External cell type provides a way to use cells that were designed outside of Lava. This cell type simply provides a mapping from cell and pin names to CIF cell number, cell size, and

<sup>&</sup>lt;sup>3</sup> The distinction between abuts left of and left of would seem redundant. The intention was that connections that were not made by abutment would be saved for a wire router. Unfortunately, this feature never got implemented.

pin location. One could view the hints for this cell type as being the complete, rigid layout.

Why different cell types? At each level in the cell hierarchy cells are composed of a number of component objects. The kinds of information that the designer would like to and not like to specify are different at the different levels. At the bottom level (leaf level), the objects being composed are typically single devices, and the connections are single wire segments. The relative locations are specified for most all components. In top level cells, the objects being composed are often themselves large cells with thousands of devices in them. The interconnections consist of hundreds of individual wires, which are often placed in logical groupings and wired systematically. These wires are often not just straight wire segments, but are routed around objects and change layers automatically. The relative placement of objects are more loosely specified. In general, Lava is given fewer hints and more freedom in the specification of larger cells because the optimum position, route, or stretch is frequently not known by the designer. At lower levels, the designer often wants more exacting control over the operations performed by the design tool and so the hints should be capable of fine control. At the higher levels, such fine control is not necessary. The designer often wishes to use broad strokes to describe layout at this level.

# 3.3. Intermediate Form

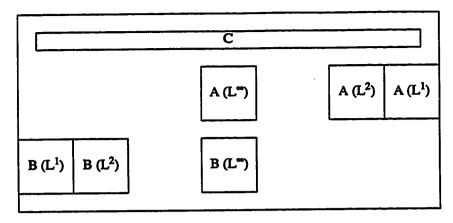

Lava undergoes a partial compilation to remove parameters, conditionals, iterations, bundles, arrays, etc. This expanded form is the input to the symbolic layout algorithms of the next chapter. Since at this level the description is no longer parameterized, a cell name consists of both the name given by the designer plus the list of parameter values that were used to produce this "distilled" description. The contents of the expanded version of two different cell types, Stix and Abut will be described.

For both cell types, the majority of the information in the intermediate form is contained in a component list and a wire list. Components are terminals, subcells, transistors, vias, etc., although in the Abut cell type only the first two are permissible. Other information in the component list, which is not specific to cell type, is additional information about the type of

component, parameters (such as sizes), orientation, etc. The connection points on the components are connected together only by wires, which are horizontal or vertical elastic segments.

In addition to the components and wires, the algorithms of the next chapter sometimes need to know connectivity information for this cell. Such information can be computed from the component and wire lists, and from knowledge of the connectivity of the components. The external connectivity information (called the *electrical abstraction*) for the subcells was computed during a similar prior operation. From the connectivity, an electrical abstraction for the current cell is prepared for use by its superior cells.

In the Stix cell type, an initial (pre-compaction) position for all of the components and wires is necessary to correctly generate the compaction constraints. As these initial positions are only used to determine an ordering, and have no relationship to any physical dimensions, they are called *pseudo-coordinates*. Also, if a subcell has more than one connection on a side, the pseudo-coordinates for all sides of the cell are necessary<sup>4</sup>. Wires have a single pseudo-coordinate and a direction. These pseudo-coordinates may be thought of as coordinates in a picture of the stick diagram of the cell.

In practice, much of the information such as positions, direction, layer, etc. may be inferred from positions, layer, etc. of adjacent components and wires. Lava does this inference so that the user does not need to provide much of this information. For the purposes of the discussion it will be assumed that all that information has already been filled in.

In the Abut cell type, the designer provides the information with which to construct an initial placement in a different manner. There are no pseudo-coordinates in the component or wire lists. The only additional information is a list of instance expressions giving the relative locations of subcells or set of subcells (such as A leftof B) as discussed in a previous section.

These lists of components and wires constitute most of the essential information required by the constraint-generation algorithms of the next chapter. The issues involved in producing these

<sup>4</sup> These pseudo-coordinates are provided as a pseudo-coordinate pair and a pseudo-size pair.

lists from the Lava input are mostly language processing and compiler issues and are not particularly relevant to IC design tools. A different front end (such as a graphics interface) could easily be substituted at this point and produce the same lists as output.

## **Summary**

In this chapter, I discussed some of the goals of producing a layout tool that allowed the designer to represent his design at a high level of abstraction with minimal sacrifice of flexibility or silicon area. I gave an overview of the language, which describes electrical connectivity, showing some of the major features: wire aggregates, parameterizable cells, an overly flexible description with disambiguating hints, and a design-rule-independent description. Finally, I described the intermediate form which is the input to the algorithms of the next chapter.

# 4. Lava Compilation

The previous chapter discussed methods to describe IC layouts using a language called Lava. This chapter presents methods for compiling Lava descriptions into a few well-defined optimization problems. The resulting optimization problems will be relatively small and sparse, and can be solved by methods described in the following chapter.

The compilation of the Lava description can be converted into three different optimization problems, longest path,  $L^1$  minimization, and constraint propagation. These optimization problems will be defined precisely as they are encountered in this chapter.

A second purpose to this chapter is to set the stage for the next chapter in which the characteristics of the resulting optimization problems are studied. In order for the characterization to be meaningful, the precise manner in which the problems are constructed must be specified. The above, however, does not mean that the characterizations will not be typical of optimization problems created by other symbolic IC layout systems. I expect the characterizations to be typical of other symbolic layout systems as well.

#### 4.1. Sticks

In this section I will first talk about standard sticks compaction, then I will extend it to take advantage of the existing hierarchy of the chip, and discuss some extensions that improve the quality of the layout and the speed of compilation. Finally, I will summarize with a perspective that unifies all the optimization problems used in this section.

The object of sticks compaction is to produce a minimal cell size for a given circuit while obeying all the constraints imposed by the design rules. The optimal solution (minimal area) of such a problem is computationally very difficult<sup>1</sup>. However, the problem can be changed to make it easier in several ways. First, the designer is often willing to (or demands to) provide the orientation and an initial relative placement of each component. The circuit description with this

<sup>&</sup>lt;sup>1</sup> To optimally solve such a problem, all legal combinations of relative positions, rotations, and reflections must be considered to optimize the nonlinear objective function. Optimal sticks compaction has been shown to be NP-complete [Sastry 82].

information is similar to a stick diagram in information content. While the size of the solution space has been cut tremendously, finding a solution of minimal area is still a difficult problem. The objective function is nonlinear and the constraints are also nonlinear (conditional), making the solution space nonconvex.

If the problem is broken down into a sequence of one-dimensional problems (alternately solving for minimum width and height), the result may not quite be optimal, but the optimization problems become very tractable. The objective (minimizing only the height or width) is linear, and the constraints are linear, resulting in a convex solution space. This problem is the longest-path problem, which is a special case of the linear programming problem. The next section describes the basic compaction algorithm for sticks-like descriptions. This method will be extended to gain efficiency (by using hierarchy) and quality (by using L<sup>1</sup> minimization) in the following sections.

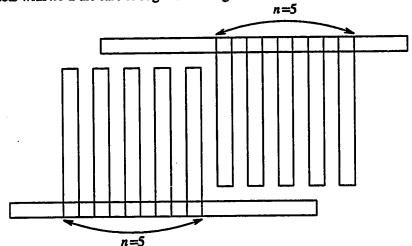

## 4.1.1. Standard Sticks Compaction

There are four types of constraints used in compaction. The first three types: component constraints, connection constraints, and boundary constraints are called fixed constraints because they are computed once and do not change from one compaction step to another. The fourth type, design-rule spacing constraints are called variable constraints because they are a function of the current positions of components and therefore may vary from one compaction step to the next. These four constraints are used to determine the positions of the objects in the final layout.

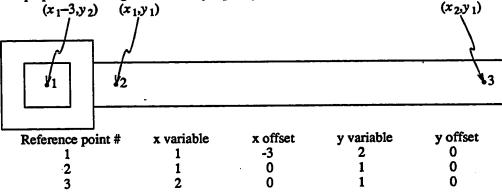

Figure 4.1 The Component Constraints for a Wire

Component constraints are used to hold portions of each component together in some specific relationship. Many component are not flexible or stretchable and therefore have no need for such constraints. An example of a simple component that requires these constraints is a wire. In Figure 4.1, the constraints  $y_1 \le y_2$  and  $y_2 \le y_1$  keep the horizontal wire horizontal, while remaining elastic in the x direction. A more complex component example is a depletion load with butting contact (pullup) and is shown in Figure 4.2. Here, in this depletion load, the butting contact

Figure 4.2 The component constraints for a depletion load

has a limited range of motion with respect to the transistor and this range is set by the component constraints. Component constraints are very useful for hierarchical sticks, since the subcells become components, and the component constraints represent the pin constraints of the subcell. The next section discusses this in more detail.

Connection constraints are used to hold together two connected components, and to maintain the design-rule-specified minimum width for the connection. In Figure 4.3 a polysilicon wire is connected to a poly-to-metal contact. The constraints in x hold the connection together, while

Figure 4.3 The Connection Constraints for a Wire and a Contact

the constraints in y ensure at least a minimum width connection. Note that the wire is not restricted to connect on center, but may slide one unit either way.

Boundary constraints simply constrain all components to remain within the four boundaries of the cell. Also, connection points (terminals) are constrained to lie on the boundary. See Figure 4.4.

Figure 4.4 Boundary Constraints

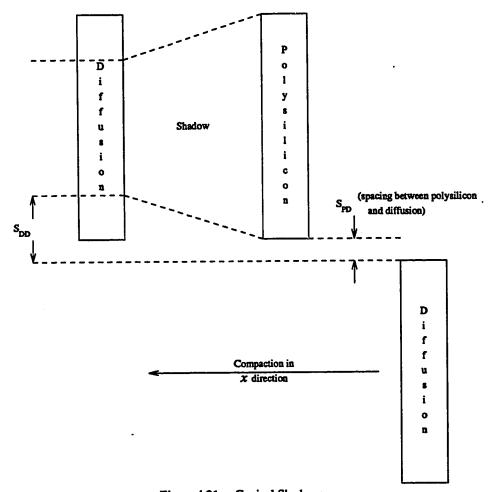

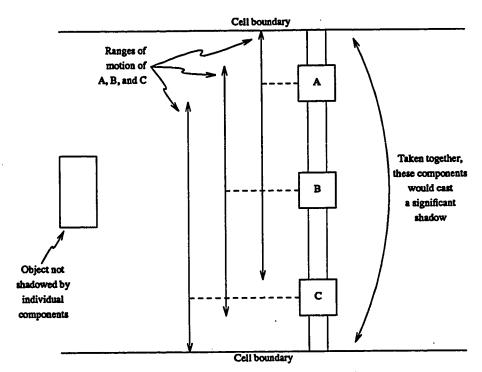

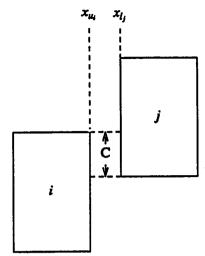

Design-rule spacing constraints, rather than holding the components together, keep them apart. As a consequence of decomposition into separate x and y problems these constraints must be a function of the positions of components<sup>2</sup>. For the sake of this discussion assume that constraints are being generated for compaction in the x direction. Each pair of components is examined to determine if design-rule spacing constraints should be written between them: If their spacing in y is less than the design rules between these components, then a constraint is generated, keeping the components greater than this design rule distance apart<sup>3</sup>. If the pair of components are within this distance in y, then an x constraint must be generated between these objects. The current x positions are examined to determine the direction of this constraint, *i.e.*, is A constrained to be to the left or right of B?. The appropriate constraint is generated as in Figure 4.5.

Figure 4.5 The generation of a design-rule-spacing constraint

Having constructed a graph representing all of the constraints between the components, we can find the positions of the objects by solving a standard optimization problem — finding the longest path in a graph. The longest-path problem is defined as follows: