## VERILOG PIECEWISE LINEAR BEHAVIORAL MODELING FOR MIXED-SIGNAL VALIDATION

# A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

Sabrina Liao

May 2014

© 2014 by Sabrina Liao. All Rights Reserved. Re-distributed by Stanford University under license with the author.

This dissertation is online at: http://purl.stanford.edu/pb381vh2919

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

### Mark Horowitz, Primary Adviser

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

### **Boris Murmann**

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

#### **Bruce Wooley**

Approved for the Stanford University Committee on Graduate Studies.

### Patricia J. Gumport, Vice Provost for Graduate Education

This signature page was generated electronically upon submission of this dissertation in electronic format. An original signed hard copy of the signature page is on file in University Archives.

# Abstract

Today's mixed-signal systems-on-chip (SoC's) are complex entities that contain very tightly coupled analog and digital circuits. Validating these complex systems requires simulating the entire design through a large number of test vectors, and each test vector might in turn lead to a long simulation. Due to traditionally differing views of validation as well as design tools for analog and digital, validation of an SoC is not easily accomplished. Behavioral modeling is an attractive approach that tries to address this issue by replacing analog circuits with high-level functional models to speed up simulation while retaining some of the analog behavior. This dissertation proposes a method for creating these models in an event-driven, digital modeling language.

The model-writing strategy is three-pronged. First, to fit into a digital simulator that simulates mostly unidirectional designs, the analog circuits must be broken into subblocks with unidirectional ports. Second, continuous time analog signals need to have a suitable representation in a discrete-time simulator. A piecewise linear format in which value-slope pairs are updated at discrete intervals is employed as an example. Third, time integration must be avoided in the computation of model outputs. By leveraging the linear (possibly with small nonlinearity) intent of analog circuits, a companion method of efficiently calculating output in piecewise linear format is developed. The overall result is analog behavioral models that are pin-accurate, fast to simulate and capture the key dynamics in analog circuits. Models of various types of circuits (a simple RC filter, a phase interpolator, a comparator and a current DAC) are composed to illustrate the wide applicability of the proposed modeling method. A 250MS/s track and hold, a 2.5-1.8V switching regulator, and a 1GHz PLL are also modeled to verify the preservation of important circuit behaviors as well as to gauge these models' computation complexity.

# Acknowledgements

William Arthur Ward once said: "Feeling gratitude and not expressing it is like wrapping a present and not giving it." I am grateful for this opportunity to give thanks to the people who have helped to bring this dissertation to fruition.

First and foremost, I would like to thank Professor Mark Horowitz for his valuable mentorship and tutelage. His dedication to his students despite his many other academic duties is awe-inspiring. He has the amazing ability to explain the most confusing concepts in the clearest of terms, and somehow can always find better words to express an idea. I have learned much from him over the years, and still have much to learn. It has truly been a privilege to work with him.

I would also like to thank Professor Boris Murmann and Professor Bruce Wooley for reading this thesis and for delivering enlightening lectures on circuits. These lectures have taught me a great deal and they have been one of the highlights at Stanford. I am honored to have Professor James Harris chair my orals committee and to have Professor Ada Poon serve on my orals committee. I appreciate the technical discussions and guidance from Professor Jaeha Kim when I first embarked on this journey of research.

My special thanks also go out to Sakshi Arora for providing the design of the dcdc converter, and to John Brunhaver for selflessly organizing his digital design data so that this dissertation could benefit from it. I have made great friends – Vaibhav Tripathi, Andrew Danowitz, Harendra Guturu, to name a few. Life as a graduate student wouldn't have been as pleasant without you. I will also cherish the memories I have made with everyone in the VLSI research group, including Teresa Lynn and Mary Jane Swenson who have tirelessly managed the administrative details, thus giving me freedom to stay focused on research.

To my wonderful parents: Thank you for always being there, showering me with love, encouragement and affirmation. You have done the impossible by giving me roots as well as wings.

This research is generously supported by the Stanford Graduate Fellowship, the Natural Sciences and Engineering Council of Canada Postgraduate Scholarships and the Stanford Rethink Analog Design initiative.

# **Table of Contents**

| Abstrac | et                                | . iv |

|---------|-----------------------------------|------|

| Acknow  | vledgements                       | . vi |

| Introdu | ction                             | 1    |

| 1.1     | Analog Validation                 | 2    |

| 1.2     | Digital Validation                | 3    |

| 1.3     | Mixed-signal Validation Challenge | 4    |

| Mixed-S | Signal Validation Background      | 5    |

| 2.1     | Analog (SPICE) Simulator          | 5    |

| 2.2     | Digital Simulator                 | 7    |

| 2.3     | Modified Simulators               | 9    |

| 2.3.    | 1 Fast SPICE                      | 9    |

| 2.3.2   | 2 Piecewise-Linear Simulation     | 13   |

| 2.3.    | 3 Mixed-Mode/Co- Simulation       | 15   |

| 2.4     | Macromodeling                     | 18   |

| 2.4.    | 1 LTI Circuit Macromodeling       | 18   |

| 2.4.2   | 2 Nonlinear Circuit Macromodeling | 20   |

| 2.5     | Behavioral Modeling               | 22   |

| 2.5.    | 1 Simulink/Matlab                 | 23   |

| 2.5.    | 2 SystemC-AMS                     | 23   |

| 2.5.    | 3 Verilog-A/Verilog-AMS/VHDL-AMS  | 24   |

| 2.5.4   | 4 Digital Verilog with Real       | 25   |

| 2.6  | Su     | mmary                                    |    |

|------|--------|------------------------------------------|----|

| Beha | vioral | Modeling Approach                        | 30 |

| 3.1  | M      | odeling Language                         |    |

| 3.2  | Ci     | rcuit Partitioning                       |    |

| 3.3  | Sig    | gnal Representation                      | 35 |

| 3    | 3.3.1  | Sampled Data Representation              | 35 |

| 3    | 3.3.2  | Augmented Representation                 | 38 |

| 3    | 3.3.3  | Another Augmented Representation: XMODEL | 43 |

| 3.4  | M      | odule Output Computation                 | 45 |

| 3    | 3.4.1  | Time Domain Response                     | 46 |

| 3    | 3.4.2  | Forming Piecewise-Linear Output          | 48 |

| 3    | 3.4.3  | Filtering Output Updates                 | 49 |

| 3.5  | Su     | mmary                                    | 52 |

| Crea | ting A | nalog Behavioral Models                  | 53 |

| 4.1  | A      | to A (Filter-like) Circuits              | 54 |

| 4.2  | D      | to D Circuits                            | 58 |

| 4.3  | A      | to D Circuits                            | 63 |

| 4.4  | D      | to A Circuits                            | 69 |

| 4.5  | As     | sertions                                 | 73 |

| 4.6  | Su     | mmary                                    | 75 |

| Expe | rimen  | tal Results                              | 76 |

| 5.1  | Tr     | ack and Hold                             | 76 |

| 5    | 5.1.1  | Circuit Description                      | 77 |

| 5    | 5.1.2  | Model Description                        | 79 |

| 5    | 5.1.3  | Simulation Results                       | 84 |

| 5.2  | D      | C-DC Switching Regulator                 | 88 |

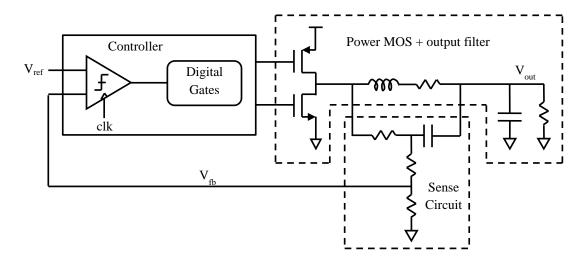

| 5    | 5.2.1  | Circuit Description                      | 88 |

| 5    | 5.2.2  | Model Description                        | 90 |

| Bibl | liogr | aph  | y                      | 120 |

|------|-------|------|------------------------|-----|

| Con  | clus  | ions |                        | 117 |

| 5.   | 5     | Sun  | nmary                  | 115 |

| 5.   | 4     | Sim  | ulation Speed Analysis | 105 |

|      | 5.3.3 |      |                        |     |

|      | 5.3.2 | 2    | Model Description      | 98  |

|      | 5.3.  | 1    | Circuit Description    | 95  |

| 5.   | 3     | Pha  | se Locked Loop         | 94  |

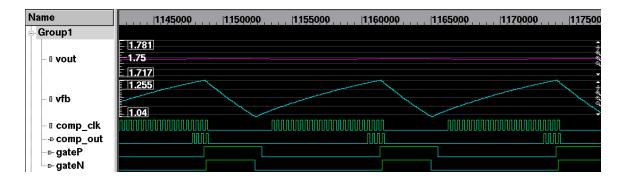

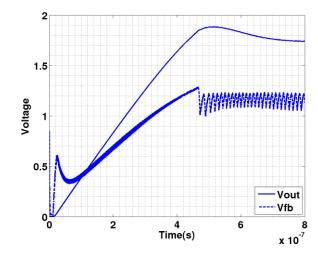

|      | 5.2.3 | 3    | Simulation Results     | 91  |

# **List of Tables**

| Table 1 - Some Commercially Available Fast SPICE Simulators           |     |

|-----------------------------------------------------------------------|-----|

| Table 2 – Nonlinear macromodeling algorithms                          |     |

| Table 3 – Contributions to distortion in track and hold               |     |

| Table 4 – Output tones of track and hold                              | 87  |

| Table 5 – PLL sub-block contribution to output jitter (SystemVerilog) | 103 |

| Table 6 – Internal re-evaluation rates for T/H                        |     |

| Table 7 – Internal re-evaluation rates for DC-DC converter            | 109 |

| Table 8 – Internal re-evaluation rates for PLL                        |     |

| Table 9 – Schematic and model simulation times                        |     |

| Table 10 – Simulation time of DPI vs. custom function calls           |     |

# **List of Figures**

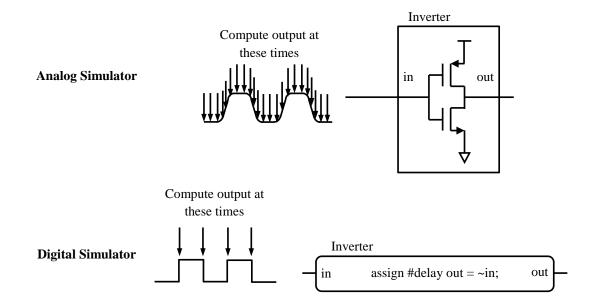

| Figure 1 – Different treatment of an inverter by analog and digital simulators           | 8  |

|------------------------------------------------------------------------------------------|----|

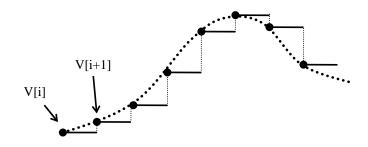

| Figure 2 – Sampled data representation of continuous time signal                         | 25 |

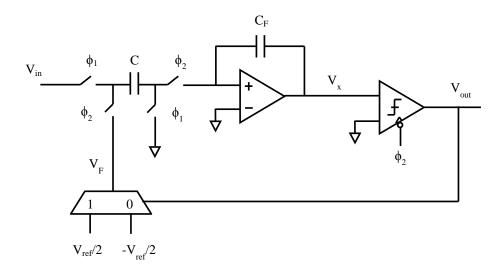

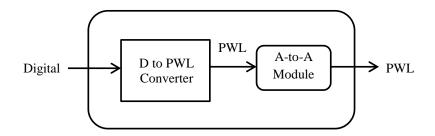

| Figure 3 – Switched capacitor implementation of 1 <sup>st</sup> order DSM                | 26 |

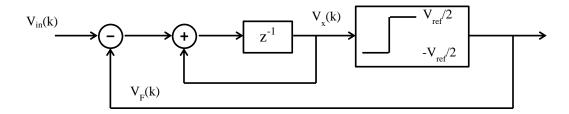

| Figure 4 – Signal flow graph for 1 <sup>st</sup> order DSM                               | 26 |

| Figure 5 – Current summing node in DAC                                                   | 33 |

| Figure 6 – Current summing node in single-slope ADC frontend                             | 33 |

| Figure 7 – Circuit partitioning procedure                                                | 35 |

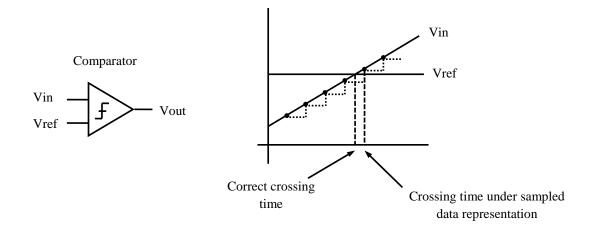

| Figure 8 – Comparator behavior using sampled data representation                         | 36 |

| Figure 9 – Track-and-hold using sampled data representation                              |    |

| Figure 10 – Sampled data representation with jitter-less clock                           | 37 |

| Figure 11 – Samples captured by jittery clock under sampled data representation          | 38 |

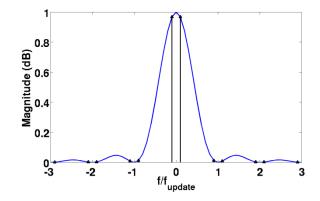

| Figure 12 – Spectrum of piecewise linear representation of a sinusoid                    | 40 |

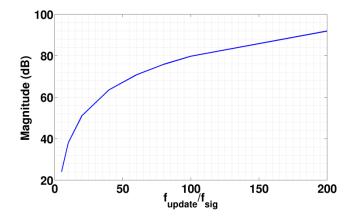

| Figure 13 – Signal to error ratio vs. signal update rates for constant time internal PWI | _  |

| waveform                                                                                 | 40 |

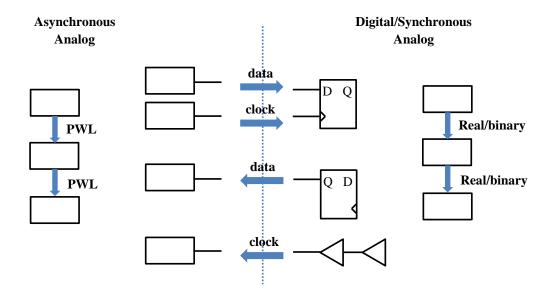

| Figure 14 – Block to block interactions in mixed-signal design                           | 41 |

| Figure 15 – Samples captured by jittery clock under piecewise linear representation      | 42 |

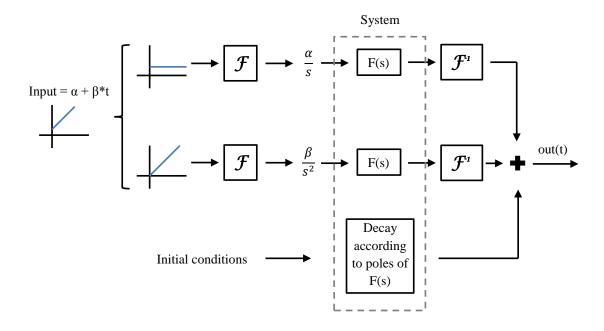

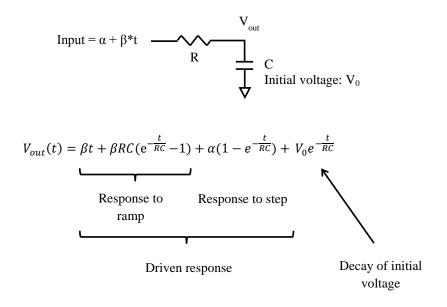

| Figure 16 – Time domain response to input linear segment                                 | 47 |

| Figure 17 – Time domain response of single pole system to a linear input segment         | 48 |

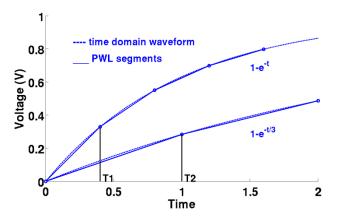

| Figure 18 – PWL segment length for systems with different time constants                 | 49 |

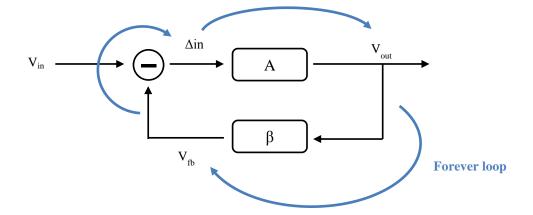

| Figure 19 – Forever loop caused by a single input update                                 | 50 |

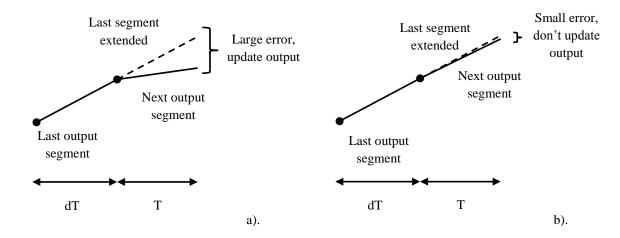

| Figure 20 – Filtering unnecessary output updates                                         | 51 |

| Figure 21 - Circuit categories based on input/output characteristic                      | 53 |

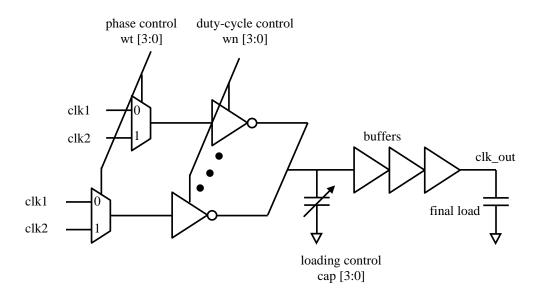

| Figure 22 – A phase interpolator implementation                                          | 60 |

| Figure 23 – Phase interpolator sample waveforms                                          | 60 |

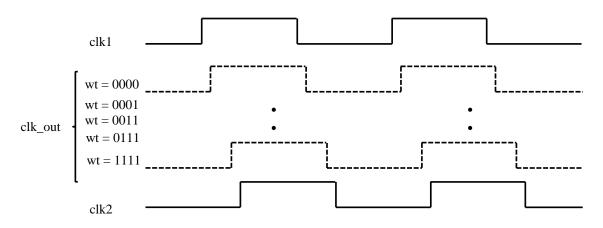

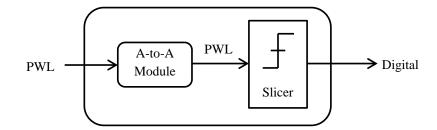

| Figure 24 – A-to-D module block diagram                                                  | 64 |

| Figure 25 – D-to-A module block diagram                                                  | 69 |

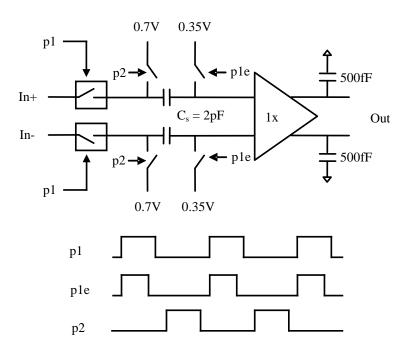

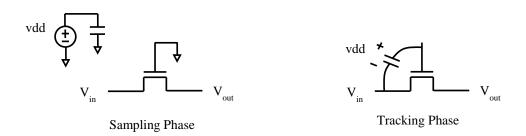

| Figure 26 – Track and hold circuit block diagram                                         | 78 |

| Figure 27 – Bootstrapping concept                                                        | 78 |

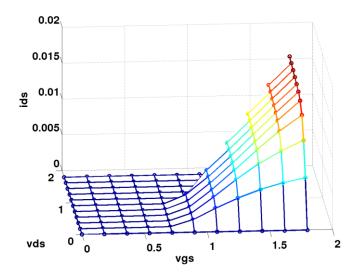

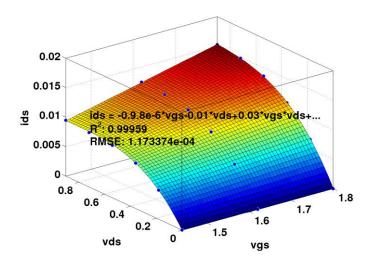

| Figure 28 – Sampling transistor current vs $v_{gs}$ and $v_{ds}$                         | 81 |

| Figure 29 – Sampling transistor current extracted as function of $v_{gs}$ and $v_{ds}$   | 81 |

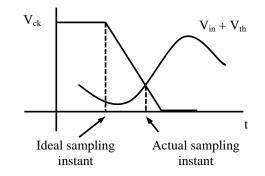

| Figure 30 – Signal dependent sampling instant                                            | 82 |

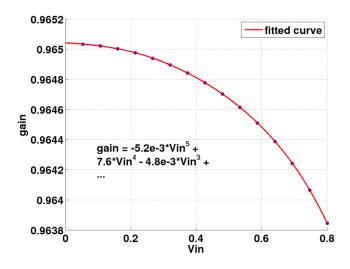

| Figure 31 – Buffer gain extracted as a function of input amplitude                       | 83 |

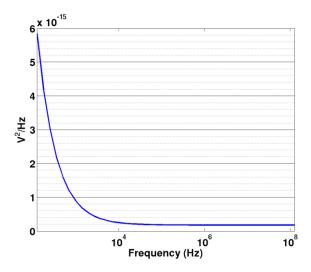

| Figure 32 – Track and hold total output noise power spectrum                | 84  |

|-----------------------------------------------------------------------------|-----|

| Figure 33 – Transient waveforms of T/H model                                | 85  |

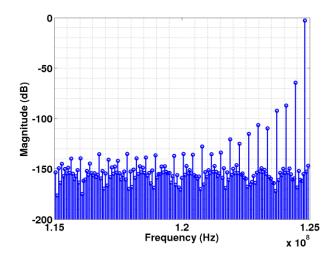

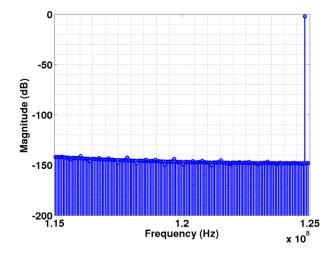

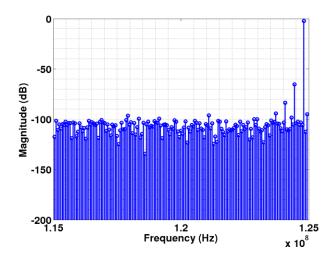

| Figure 34 – T/H output spectrum (Spectre)                                   | 85  |

| Figure 35 – T/H output spectrum (SystemVerilog without distortion effects)  | 86  |

| Figure 36 – T/H output spectrum (SystemVerilog with distortion and noise)   | 87  |

| Figure 37 – Buck converter block diagram                                    | 88  |

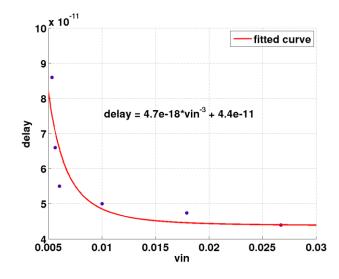

| Figure 38 - Clocked latch delay extracted as a function of input amplitude  | 91  |

| Figure 39 - Transient waveforms of buck converter model                     | 92  |

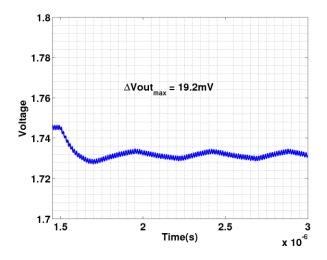

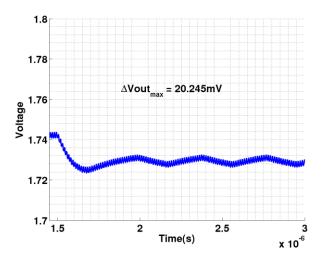

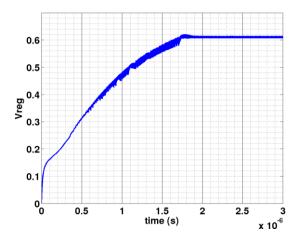

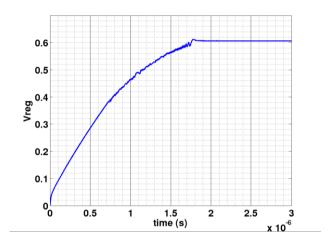

| Figure 40 – Startup behavior of buck converter (Spectre)                    | 93  |

| Figure 41 – Startup behavior of buck converter (SystemVerilog)              | 93  |

| Figure 42 – Buck converter load response (Spectre)                          | 94  |

| Figure 43 – Buck converter load response (SystemVerilog)                    | 94  |

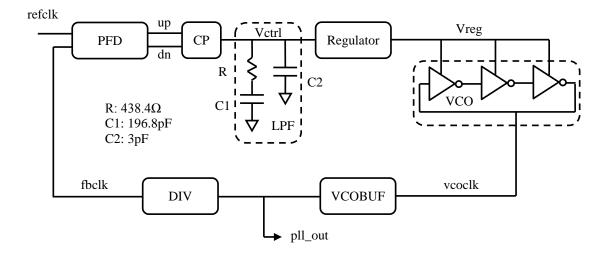

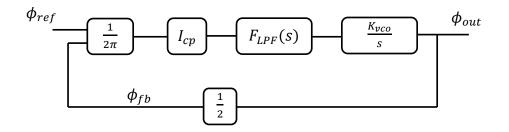

| Figure 44 – PLL block diagram                                               | 96  |

| Figure 45 – Linearized PLL model                                            | 96  |

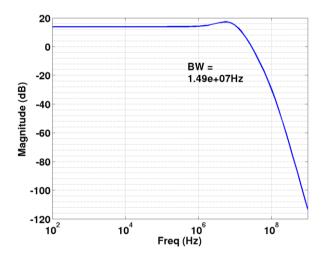

| Figure 46 – Closed loop PLL transfer function                               | 97  |

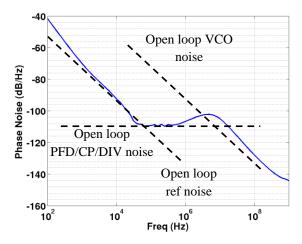

| Figure 47 – Typical PLL phase noise plot                                    | 98  |

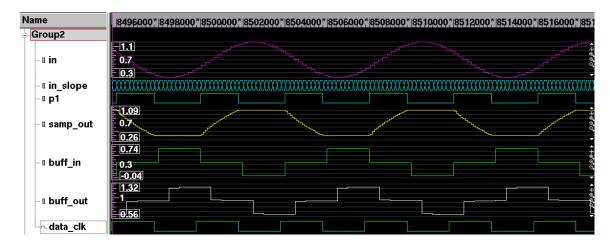

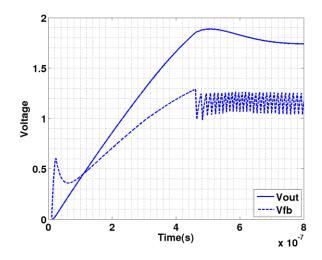

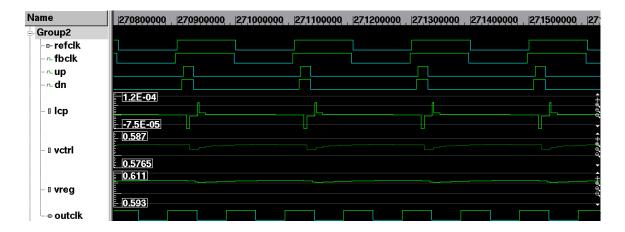

| Figure 48 – Transient waveforms of PLL model                                | 101 |

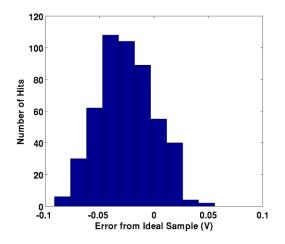

| Figure 49 – PLL locking behavior (Spectre)                                  | 102 |

| Figure 50 – PLL locking behavior (SystemVerilog)                            | 102 |

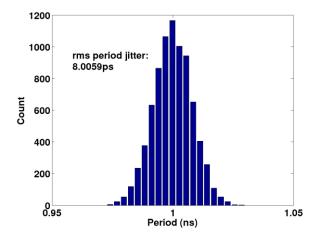

| Figure 51 – PLL output jitter histogram (SystemVerilog)                     | 103 |

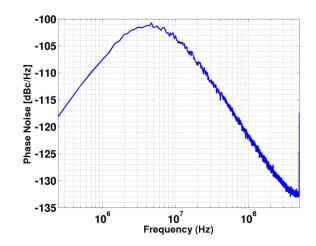

| Figure 52 – PLL output phase noise spectrum (SystemVerilog)                 | 104 |

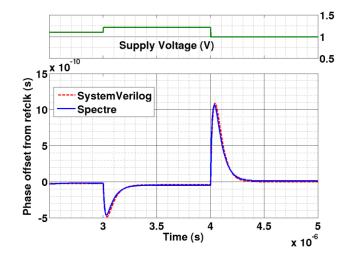

| Figure 53 – PLL output phase response to supply disturbances                | 105 |

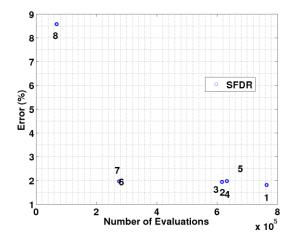

| Figure 54 – T/H SFDR error for various re-evaluation rates                  | 107 |

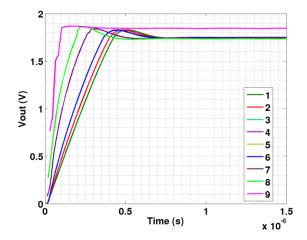

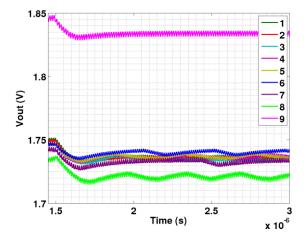

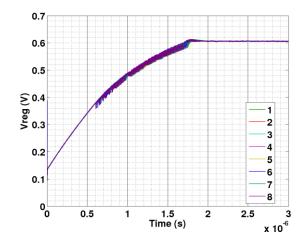

| Figure 55 – Buck converter startup behavior for various re-evaluation rates | 109 |

| Figure 56 – Buck converter load response for various re-evaluation rates    | 110 |

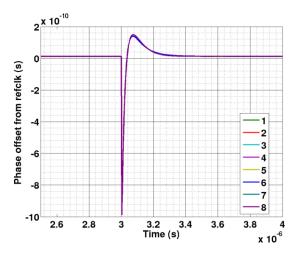

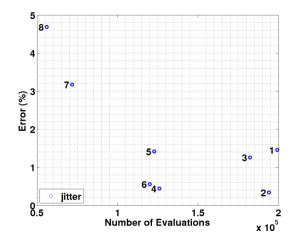

| Figure 57 – PLL locking behavior for various re-evaluation rates            | 111 |

| Figure 58 – PLL phase step response for various re-evaluation rates         | 111 |

| Figure 59 – PLL output jitter error for various re-evaluation rates         | 112 |

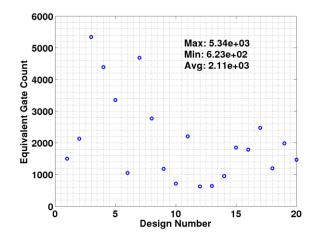

| Figure 60 – PLL model equivalent gate count from digital designs            | 113 |

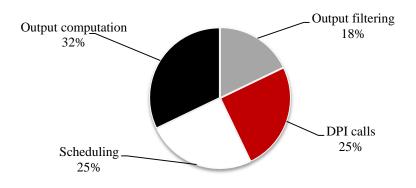

| Figure 61 – A-to-A module CPU time distribution                             | 114 |

|                                                                             |     |

# Chapter 1

# Introduction

There are two types of circuits in modern systems-on-chip (SoC's): analog and digital. Traditionally, different abstraction, design methods and tools are used for each type. For a long time, this approach worked well because the designs were on different chips, or weakly coupled, such that analog circuits can be designed and validated in isolation from the digital circuits. Over the past decade, however, the constant search for smaller, faster and less power hungry SoC's has brought analog and digital ever closer together. With aggressive scaling, designers saw benefit in the smaller form factor, flexibility and better noise sensitivity of digital circuits and began to implement a number of traditionally analog functions using digital circuits. For instance, continuous time equalization techniques in clock and data recovery circuits are supplemented with digital adaptive equalization algorithms [4]; in other cases, analog equalization techniques are complete replaced with an ADC frontend and extensive digital signal processing [5]. Phase-locked loops (PLL's) have mostly been analog entities, however there has been tremendous interest recently in achieving frequency synthesis using mostly digital PLL's [6] [7]. Since scaling degrades matching<sup>1</sup>, a popular solution is to use digital circuits to reduce analog matching errors as seen in digitally assisted data converters [3] [2]. The

<sup>&</sup>lt;sup>1</sup> Scaling improves analog matching per unit area [99], however minimum size devices often have the higher performance that designers seek and the overall matching of these devices degrades as technology scales.

#### Chapter 1. Introduction

demand for better power performance has also brought digital power management on chip. Wireless transceivers use profiled power management units to reduce active power consumption [8] and many digital control techniques such as digital peak voltage/peak current [84], digital pulsewidth modulation [85] and constant on/off time control [86] have been developed to rival traditional analog control loops in power converters. In all these cases, analog and digital circuits are no longer isolated entities, but rather two tightly coupled and constantly interacting components of a complex system.

Any complex system requires validation as a whole, but doing so is difficult because of the traditionally differing and incompatible design/validation methods of analog and digital circuits [80]. This thesis proposes using high-level analog functional models written in SystemVerilog to address this validation gap, and provides a method for creating these models.

## **1.1 Analog Validation**

Analog circuits are validated at the device level, using a simulator (e.g. SPICE) that uses compact device models to evaluate the behavior of the circuit schematic. Designers are interested in measuring some characteristics of the analog circuit's output and if a set of required performance is achieved, then the circuit is considered to be validated [60]. For example, in a sample and hold, designers might drive the input with a sinusoid slightly below the Nyquist frequency and measure the circuit's spurious free dynamic range (SFDR), signal to noise ratio (SNR), power and output swing. For a regenerative latch, the set of test signals might be a series of constant voltages with varying amplitude. The performance specification might involve an upper limit on the input to output delay for different input voltages. Designers simulate the circuit using the various types of analyses available in SPICE (such as DC, transient, AC, PAC, PSS, PNOISE) and inspect that all simulation results meet spec. Often times, the simulation

space also extends to the entire gamut of process corners, temperatures and supply voltages [60].

Despite the large variety of characteristics that can be measured of analog responses, analog outputs are smooth functions of the circuit's input. Therefore, designers are usually not concerned with enumerating every possible test stimulus such that the input space is finely sampled. Typically, a small set of test inputs is sufficient to fully characterize the analog response surface, because the result from one input case yields a great deal of information on results from similar inputs. Using this small set of test cases, analog validation can be completed for each performance metric even if each analog test case (especially those that require transient simulations) might be time-consuming.

### **1.2 Digital Validation**

The goals of digital testing are very different from those of analog test. Rather than trying to extract a number of parameters of the circuit, the digital designer wants to know whether a large collection of logic does the correct function. A digital design with N state variables has  $2^{N}$  mutually independent states – that is, the correct function of one state yields no information on the correct function of any of the other states. In other words, the result surfaces of digital circuits are not smooth like analog circuits, and it is hard to predict what the machine will do in a specific situation without testing that situation. Validating a digital circuit, therefore, involves exercising every possible state that the design may go through. Commonly used digital simulators include VCS and ModelSim.

Even though the simulation time of a single test vector may be small, a digital design may contain millions of logic gates and the number of test vectors necessary to completely verify a design is very large – sometimes impractically so. As a result, coverage is oftentimes sacrificed by running only as large a set of test vectors as time will

#### Chapter 1. Introduction

allow. In addition, the verification is concerned with function only; timing information such as delay and skew are handled separately by static checking tools.

## **1.3 Mixed-signal Validation Challenge**

Given the vastly different validation approach for analog and digital circuits, it is not surprising that the validation of a mixed-signal design is difficult. In order to run millions of test vectors with reasonable speed, the digital component of an SoC must be validated in a discrete-time, event-driven, digital simulator [87]. At the same time, active collaboration between analog and digital – for example, digital calibration – dictates that the digital component must be aware of the analog component's behavior in order to determine its own behavior. This means that the analog component must also be simulated for every test vector sent to the system. Difficulties arise in this case since first, there is a clear disconnect between analog and digital simulators and second, timeconsuming analog transient simulation means that either the coverage of the validation suite will be very limited or the validation effort cannot be completed within any practical amount of time.

There have been a number of approaches that address mixed signal validation and these will be reviewed in Chapter 2. Among these approaches, behavioral modeling seems to be the only solution fast enough for mixed-signal validation. To summarize the contribution of this work – namely providing some formalism to behavioral modeling – Chapter 3 will lay down general guidelines developed to writing behavioral models. Next, to see how these guidelines can be applied, Chapter 4 will discuss models for different types of circuits. To be more specific and evaluate the models' performance, Chapter 5 will demonstrate the viability of the proposed model-writing strategies through several real circuit examples. An analysis of the models' efficiencies will also be presented. Concluding remarks are provided in Chapter 6.

# Chapter 2

# **Mixed-Signal Validation Background**

System-level validation of mixed-signal SoC is challenging [16], and not surprisingly, it is an active area of research. To better understand the issues that need to be addressed, this chapter will begin with a discussion of traditional analog and digital simulators (Sections 2.1 and 2.2 respectively). Given the difference in simulation tools, three different approaches to mixed-signal validation will be compared. One approach focuses on modifying the simulators to make the analog simulator run faster, and be able to connect to a digital simulator. The macromodeling approach tried to replace the device-level network that is solved by the analog simulator with a simpler one that has equivalent behavior. Lastly, behavioral modeling completely replaces the circuit schematics with a functional description. While these three methods have advantages and disadvantages, and behavioral modeling is the solution with the highest hopes of being fast enough for mixed-signal SoC validation.

## 2.1 Analog (SPICE) Simulator

Analog designers use SPICE-like simulators to help them predict and analyze the behavior of a circuit. Starting from a schematic and very accurate device models, SPICE simulators compute the voltage and current values at each node for all instants of time. KVL and KCL nodal equations are generated first. Due to devices such as transistors in the design, these equations are usually a set of differential-algebraic equations (DAE's), whose general form is shown below [1]:

$$\frac{dq(\boldsymbol{v},t)}{dt} = i(\boldsymbol{v},\boldsymbol{u},t) \tag{1}$$

$\mathbf{v} = \mathbf{v}(t)$  is a vector of nodal voltages and branch currents;  $\mathbf{u} = \mathbf{u}(t)$  is a vector of inputs; t is time;  $q(\bullet)$  is an operator describing charge; and  $i(\bullet)$  is an operator describing current. Numerical integration methods need to be invoked in order to solve these equations. First, time-discretization is applied using algorithms such as backward Euler, trapezoidal or second order Gear. For example, if backward Euler integration were used, the system of (1) will yield an algebraic equation

$$\boldsymbol{v}_{t+\Delta t} = \boldsymbol{v}_t + \Delta t \cdot i(\boldsymbol{v}_{t+\Delta t}, \boldsymbol{u}_{t+\Delta t}, t + \Delta t)$$

<sup>(2)</sup>

This equation needs to be solved for the unknown vector of node voltages and branch currents,  $\mathbf{v}_{t+\Delta t}$ , at time t+ $\Delta t$  where  $\Delta t$  is the time step. This is equivalent to finding zeros of a nonlinear operator:

$$F(\boldsymbol{v}) = \boldsymbol{v}_{t+\Delta t} - \boldsymbol{v}_t - \Delta t \cdot i(\boldsymbol{v}_{t+\Delta t}, \boldsymbol{u}_{t+\Delta t}, t+\Delta t) = 0$$

(3)

The solution of (3) can be obtained with an iterative algorithm such as the Newton-Raphson method or successive chords method. Using, for example, the Newton-Raphson method, a single iteration involves solving the equation:

$$J_F(\boldsymbol{v}^{i+1}) - J_F(\boldsymbol{v}^i) = -F(\boldsymbol{v}^i)$$

(4)

$J_F$  is the Jacobian matrix for operator F and i is the iteration number. The solution for (4)

can be found using direct matrix methods such as LU factorization. The iteration stops when the difference between  $v^i$  and  $v^{i+1}$  is smaller than some predefined value.

In a transient simulation, the construction of the system of equations, the discretization of this set of DAE's, and the iterative matrix solves are carried out at every time step. In accordance to analog designers' expectations, SPICE simulators prioritize high-accuracy above anything else [1]. This in turn means highly-accurate and detailed device models, creating a single system of equations for the entire circuit, using very fine time steps during discretization, and calling direct matrix solvers that are computationally expensive. All these traits as well as the purpose of the analog simulator are considerably different from those of the digital simulator, as the next section will show.

### 2.2 Digital Simulator

Digital designers work with circuits that have already been validated at the transistor level to design a larger system that performs a digital function. The purpose of the digital simulator, hence, is to evaluate the logical function that the design created. These designs are generally written in a hardware description language (HDL) like VHDL or Verilog, and simulated in a digital simulator such as VCS or ModelSim. The HDL is a functional model of the design and is later mapped to standard cells implementing different logical functions using digital synthesis tools.

In simulation, the distinct changes in Boolean values are tracked. As a result, digital simulators are discrete-time and only evaluate the functional models when inputs change. An internal time-wheel mechanism keeps track of when the input changes occur - these are called triggering events. When such an event is encountered, the simulator wakes up and computes the new outputs. If the outputs change, the changes are scheduled to take effect at a future time as determined by the delays of the gates. Then the time-wheel advances. Periods with no change in Boolean values (e.g. between clock cycles of

a flip-flop) are skipped in the simulation until the next triggering event – this is called the selective trace technique [16]. Thus, as time progresses the evolution of the system's state is determined and the logic function of the design is verified.

The fundamental difference between an analog and a digital simulator can be illustrated using an inverter with some clock input (see Figure 1). To the analog simulator, an inverter is two transistors. The SPICE algorithm will be concerned with solving the output waveform very accurately at each time instance, and will be doing computations at all times (although the figure shows constant time steps for computation, more advanced analog simulators have adopted variable time steps so that computation occurs less often when the signal is not fluctuation much). The digital simulator, on the other hand, only computes the output of the inverter when the input changes its Boolean value. The correct timing of the output will come from the delay of the inverter annotated in its functional model. Therefore, for the same amount of time simulated, an analog simulation is much more computationally intensive and time-consuming.

Figure 1 – Different treatment of an inverter by analog and digital simulators

### 2.3 Modified Simulators

The previous two sections have demonstrated that analog and digital simulators use different algorithms and have very different computational costs. This clear disconnect makes mixed-signal validation difficult. The following sections review research that concentrates on altering the simulators to make them more suitable for mixed-signal simulations. Fast SPICE involves a collection of techniques to accelerate the basic SPICE engine so that larger designs (possibly including digital as well) can be simulated. The piecewise-linear simulator speeds up simulation by using a piecewiselinear description of the circuit network instead of the full system of nonlinear DAE's. However, simulating digital circuits with analog simulators is difficult even with efficient algorithms and simplified nonlinear DAE's. Therefore, the mixed-mode simulators focus on creating an appropriate interface between an analog and a digital simulator so that the two different types of circuit can be simulated with their native engines.

### 2.3.1 Fast SPICE

The conventional SPICE simulator, whose mathematical engine was briefly outlined in Section 2.1, provides a means of modeling integrated circuits with the highest possible accuracy. Because of this constraint on accuracy, SPICE simulators must use full equation-based device models as well as high complexity direct linear solvers on a single large matrix that represents the entire design. All this results in a simulator with a complexity of  $O(n^{1.5-2})$  where n is the number of nodes in the circuit and a limited capacity of about 100,000 active elements (MOSFETs) [1]. With modern SoC designs reaching an active element count of from 100 million to 1 billion MOSFET devices and a parasitic devices count in the millions, performing full-chip functional simulation is well beyond the capabilities of conventional SPICE. On the other hand, the accuracy requirement for full-chip functional validation (especially for the digital parts of an SoC) is not as stringent [1]. The accelerated transistor-level ("fast SPICE") simulator, therefore,

leverages this fact and applies three general methodologies to speed up simulation. These methodologies may be classified as matrix-based, graph-based and circuit-based.

The matrix-based approach is equally applicable to both analog and digital circuits. At its core, it fundamentally argues that after all other optimizations, there was going to be a system of equation that needed to be solved and hence developing faster matrix solution algorithms will lead to shorter simulation time. For instance, hMETIS [13] reorders nodes during matrix factorization and linear solves to produce fill-reduced sparse matrices that are easier to solve. Furthermore, matrix preconditioning techniques such as incomplete LU factorization and multi-grid preconditioning [1] can be used on sparse matrices to reduce solve time. There are also fill-in based matrix partitioning algorithms, such as [9], that review the fill-in patterns and break down the problem into smaller pieces such that the sub-problems are easier to solve than the single matrix.

The graph-based approach contains an eclectic selection of techniques that rely on treating the design as a graph and drawing inspiration for acceleration from hierarchical circuit data storage. It has been observed in [19] that simulating a very large circuit on a computer with a virtual memory leads to a large amount of paging due to the near random distribution of data in memory. By maintaining hierarchy in a design, and careful memory allocation, data structures for a given sub-circuit will be in a smaller number of pages, and hence will reduce overheads and improve the run-time of the simulator. Therefore, efficient methods for processing hierarchical netlist have shown to improve speed and capacity, most predominantly in the simulation setup phase [1]. Isomorphic matching techniques [14] [15] also fall into the graph-based category. Because the netlist data is stored hierarchically, sufficiently identical circuit blocks can be found during the transient simulation phase, and repeated simulation is avoided. The isomorphic matching technique is particularly well-developed for identifying highly regularized circuit blocks like memory arrays, leading to methodologies such as hierarchical array reduction [10] [11] that can improve memory simulation speeds by up to 50x.

The circuit-based viewpoint targets the acceleration of SPICE for digital circuits. The method is a two-step process. First separate the circuits, automatically or semiautomatically, with respect to their functional characteristics - analog or digital. Second, develop and apply appropriate optimization and simulation strategies for the two circuit types separately. The circuit partition algorithms have evolved over the years. Initially, simple methods such as grouping channel-connected MOSFETs proved to be effective in predominantly digital circuits connected to ideal voltage sources [1]. More recent advances in partition methods introduce digital rail detection as well as topological analysis [9]. Once the digital partitions are found, specialized simulation strategies can be applied to them. For example, approximate device models can be utilized instead of the full equation-based models. Some common simplified device models include lookup tables of empirical gate delays [18] [20], ideal current source in parallel with a conductance exhibiting piecewise-polynomial characteristics [21] and DC operation region dependent current models [20] [31]. Another strategy is to use different matrixsolving algorithms as well as integration time-points than the analog partition. For instance, relaxation-based algorithms in [17] discard coupling sub-matrices in the full matrix so that the decoupled matrices are faster to solve. In [22], the direct SPICE method with network separation is carried out so that relaxation is only applied when the coupling matrices are weak (i.e. close to 0). The coupling is also re-assessed dynamically for the duration of the simulation. In addition, this de-coupling allows latent sub-circuits (circuits whose node voltages and branch current don't change much on successive iterations) to use larger time-steps of integration than those of critical analog circuits and hence increase simulation speed. This is called the multirate integration technique because in the basic SPICE engine, the entire design uses the same integration timepoints when solving the system of DAE's.

Though the three approaches (matrix, graph and circuit) have been presented separately, many fast SPICE simulators deploy all three simultaneously. Another technology that fast SPICE simulators benefit from is parallel computing. From the matrix-based point of view, parallel and multi-threaded linear solvers can be employed to speed up simulation. From the circuit-based perspective, the partitioned sub-systems can be simulated in parallel on several processors. Some commercially available Fast SPICE simulators are listed in Table 1. Note that these simulators achieve an order of magnitude acceleration compared to conventional SPICE.

| Tool                      | Company         | Comments                              |  |

|---------------------------|-----------------|---------------------------------------|--|

| Spectre APS               | Cadence         | 10x faster than Spectre               |  |

|                           |                 | Proprietary full-matrix solver        |  |

|                           |                 | Multi-thread / multi-core             |  |

| Spectre XPS               | Cadence         | Announced on October 9, 2013          |  |

|                           |                 | Advanced partitioning/model reduction |  |

| Virtuoso UltraSim         | Cadence         | Hierarchical storage                  |  |

|                           |                 | Isomorphic and adaptive partitioning  |  |

|                           |                 | Automatic parasitic reduction         |  |

| Analog FastSPICE Platform | Berkeley Design | 5-10x faster than SPICE               |  |

|                           | Automation      | Proprietary full-matrix solver        |  |

|                           |                 | Multi-thread/multi-core               |  |

| FineSim                   | Synopsys        | 3-10x faster than SPICE               |  |

|                           |                 | Advanced full-matrix solvers          |  |

|                           |                 | Multi-thread / multi-core             |  |

| HSIM                      | Synopsys        | Hierarchical storage                  |  |

|                           |                 | Isomorphic matching                   |  |

|                           |                 | Parasitic reduction algorithm         |  |

| Eldo Premier              | Mentor          | 2.5-20x faster than SPICE             |  |

|                           | Graphics        | Proprietary full-matrix solver        |  |

|                           |                 | Multi-thread / multi-core             |  |

Table 1 - Some Commercially Available Fast SPICE Simulators

#### **2.3.2** Piecewise-Linear Simulation

In Fast SPICE, the high accuracy of analog circuit simulation is maintained, while various relaxation techniques are applied to simulate digital circuits. The piecewise-linear (PL) simulator is an interesting class of tools, in that it represents an entire design, including logic gates, resistors, capacitors and transistors, in the form of a piecewise linear system rather than the full blown differential algebraic system. In other words, it allows both analog and digital circuits to have a particular form of relaxation.

Bokhoven in [88] derived that a continuous time piecewise linear dynamical system can be fully captured by (5).

$$\begin{bmatrix} 0\\ \dot{u}\\ p \end{bmatrix} = \begin{bmatrix} A_{11} & A_{12} & A_{13}\\ A_{21} & A_{22} & A_{23}\\ A_{31} & A_{32} & A_{33} \end{bmatrix} \begin{bmatrix} x\\ u\\ q \end{bmatrix} + \begin{bmatrix} a_1\\ a_2\\ a_3 \end{bmatrix}$$

(5)

where  $p \ge 0, q \ge 0$  and  $p^t \cdot q = 0$

Vectors x and u represent the system's inputs and state variables respectively. The matrix shown can describe a PL system of  $2^n$  linear segments, with n being the dimension of matrix A<sub>33</sub> [33]. The condition on p and q originates from the derivation of the matrix representation, which is based on the addition of ideal diodes as PL elements to linearize the system and ensure PL behavior is exhibited [88]. In this case, p would be the diode voltage, and q the diode current. As a result, equation (5) is sometimes called the ideal diode model.

An advantageous property of piecewise-linear equations is that the solution algorithms yield global convergence, instead of local convergence which sometimes occurs for SPICE [33]. The most commonly used numerical algorithm for PL solutions is the Katzenelson algorithm [88]. This algorithm is similar to the Newton-Raphson

algorithm used in SPICE. The major difference is that the solution of the DAE system for SPICE is continuous, while here the system is described by a set of linear segments and discontinuities occur at the boundary of the segments. Therefore, at any iteration of the algorithm, if the solution vector was found to have crossed the boundary of the current segment, the next iteration would have to take a smaller time-step and the set of PL equations need to be solved for the new segment before further integration can occur. Stiphout et al. in [33] presents a piecewise-linear simulator, PLATO, combining the above PL representation of a system with multirate integration techniques described in Section 2.3.1. This implementation suffers from a great deal of computational overhead. Since each sub-circuits has its own optimal integration rate and simulation results are only available after the determination of a new stepsize, recomputation would be necessary if the new stepsizes differs too much from the previous ones because the design is flattened and simulated as a whole. Yang et al. in [34] improves simulation speed as well as capacity by performing symbolic and hierarchical piecewise-linear analysis. Instead of the ideal diode formulation, parameterized matrices model a given linear segment of the system behavior. Not only does this allow for more compact data representation, symbolic solution can also be obtained so that each iteration of the Katzenelson algorithm does not require a separate LU factorization, hence accelerating simulation speed. The hierarchical scheme allows very large (actually without limit) designs to be analyzed symbolically since the size of the circuit matrix that needs to be solved is reduced to the size of small sub-blocks [34]. The symbolic and hierarchical PL simulator proposed in [34] reports simulation speed ups of up to 10x compared to conventional SPICE.

An interesting property of the piecewise-linear simulator is that macromodels of sub-circuits such as operational amplifiers can be simulated instead of the full transistor-level model [33]. Just as digital circuits are simulated in their Boolean abstraction in digital simulators, here, the analog circuits can be simulated in a high-level piecewise-linear abstraction. As long as a sub-circuit's behavior is described by a set of PL matrices,

this sub-circuit can be inserted directly into the overall design's matrices and be naturally mixed with low-level components [33]. The idea of abstracting away transistors inside an analog sub-block is actually what macromodeling – another area of research geared toward mixed-signal SoC validation – attempts to achieve. The macromodeling solution will be presented in Section 2.4.

#### 2.3.3 Mixed-Mode/Co- Simulation

Fast SPICE simulators have come a long way from conventional SPICE. Because of their efficient algorithms and in some cases, specialized technologies that target a specific circuit topology (e.g. memory arrays), they have been adopted by industry to aid in circuit design. Yet, they are not often employed in SoC validation. Although Fast SPICE simulators have an improved time complexity of  $O(n^{1.1-1.5})$  compared to  $O(n^{1.5-2})$  of basic SPICE, they are still not scalable to designs with up to billions of active devices requiring millions of test vectors [1]. The mixed-mode simulator research community recognizes the difficulties of simulating both analog and digital circuits using an analog (or simplified and optimized analog) simulator, and proposes to stitch together an analog simulator with a digital simulator, thus allowing each type of circuit to be analyzed by their respective engines.

Some work (for example [12] and [24]) focus on implementing only the interface and making it flexible so that numerous simulators can be coupled together without much modification to the interface itself. Others choose to integrate specific analog solvers and digital simulators into a single entity. Whichever the route taken, the key elements at play in the design of a mixed-mode simulator are sub-circuit type labeling, electrical interface between analog and digital, and global timing synchronization. First, circuit sub-blocks must be designated as digital or analog. Manual partitioning of a design is often done [20] as it is natural in a top-down flow for the designer to be aware ahead of time which subblocks are analog and which are digital. In this case, the partitions are inherent in the representation of each block: schematic for analog, RTL for digital. Once the sub-circuits are marked for either the analog solver or the digital engine, the interface between analog and digital circuits needs to be defined and signal value conversion rules need to be set. In its simplest form (as seen used in [16]), an analog to digital signal conversion is a threshold given by (6):

$$v_{logic} = \begin{cases} HIGH, v > k_r VDD(rising) \\ LOW, v < k_f VDD(falling) \end{cases}$$

(6)

where VDD is the supply voltage, and  $k_r$  and  $k_f$  are technology dependent constants with  $0 < k_f < k_r < 1$ . A more elaborate conversion method is used in [20] in which a four-level threshold (Max-H, Max-L, Min-H, Min-L) is implemented, such that Max-H and Min-H determine the margin for the detection of logic high and Max-L and Min-L determine the margin for logic low. If the simulator does not detect two logic levels (high and low) or a digital input is non-monotonic, an error flag is sent to the user or if the schematic representation of the digital block is available, the simulator automatically switches this block to the analog solver.

For digital to analog interface, the typical method is to use rise and fall times on the digital signal since analog solvers do not handle well instantaneous transitions in voltage [16]. In [20], the user defines delay parameters including rise/fall time and driving capability in capacitance units. The total rise/fall delay time would equal rise/fall time + capability factor \* load capacitance. The high impedance state in digital logic could be modeled as a user defined high impedance output resistance, which is ramped exponentially to its final value so that instantaneous changes in voltage can be avoided [16].

The last major piece to a mixed-mode simulator is a global timing synchronization mechanism. Recall from Section 2.1, the time-steps in the analog solver is controlled by the required simulation accuracy. For the digital simulator, the evaluation points occur when inputs change and is recorded on a time wheel. The time instances of the analog time-steps are independent from the time instances of the digital events, but they need to move forward together in a mixed-mode simulator. The scheme presented in [16] and [23] is to preserve the digital event list and between the events, let the analog solver evaluate using numerical methods but adapt the integration step such that it stops at a digital event. At the same time, when an analog signal reaches a certain condition that causes a digital event, that event is scheduled on the digital time wheel to force an evaluation in the digital simulator.

Now that the conceptual mixed-mode / co- simulator is complete, parallel computing can be applied to accelerate simulation just as it had benefited Fast SPICE simulators. A design is first partitioned onto different processors, either randomly or by applying some heuristics such as grouping by nearness [25]. Communicating across partitions is a large overhead. Value synchronization across multiple processors is typically achieved with sending messages containing information on the last simulated time [24]. A few scheduling policies include deadlock avoidance [26], deadlock detection and recovery [27], the Timewarp algorithm [30] and the moving time window algorithm [28]. The latter algorithms try to reduce communication by blocking value udpates in time. Speedup from parallelism is typically sub-linear due to the communication overhead across multiple processors [24].

Mixed-mode or co- simulators bring together analog and digital simulation with the aim to benefit from the best of two worlds: analog circuits will be solved accurately by the analog simulation engine, and at the same time, the digital simulation will be maintained at its usual blazing speed [29]. When pitted against top-level mixed-signal SoC validation, however, analog simulation becomes the bottleneck and slows down the entire simulation [32]. Even if a Fast SPICE simulator were used as the analog solver here, the speedup would be about an order of magnitude (recall from Section 2.3.1 and 2.3.2), but performing mixed-signal SoC validation requires the analog circuits be simulated over millions of test vectors. For example, a test might involve a power-up sequence that needs to wait for the analog circuits to turn on and reach a stable operation point, or it might run through a complex digital calibration loop. These simulations could take ms or even longer, while the analog simulator's integration step might be on the order of ps or fs. Therefore, another line of attack is needed.

### 2.4 Macromodeling

Modifying the analog and digital simulators brought about some (but not enough) simulation acceleration. Time is predominantly being spent in the analog simulator. With this in mind, macromodeling aims to alleviate the analog bottleneck. Given a circuit netlist, the complete behavior of the system is captured by a set of differential-algebraic equations (1). Loosely speaking, the macromodeling problem (sometimes called model order reduction problem) is defined as finding an alternate, possibly simpler, version of (1) which will then simulate faster, but preferably retain as much of the full SPICE model behavior as possible. To evaluate the effectiveness of macromodeling for the mixed-signal validation problem, this section will review two macro model generation methods. Both methods assume a model candidate and attempts to determine the model "coefficients" through an assortment of approximation techniques. The Linear Time Invariant (LTI) macromodeling method, as the name suggests, assumes the circuit is an LTI system. The nonlinear methods assume various degrees and types of nonlinearity exist in the circuit to be modeled.

#### 2.4.1 LTI Circuit Macromodeling

A representation of an LTI system is its transfer function H(s). Since the analog circuit is assumed to be LTI, a straightforward modeling method is to fit a reduced-order transfer function  $H_r(s)$  to the original full transfer function. A well-known method is the Padè approximation [53] in which  $H_r(s)$  takes the form of

Chapter 2. Mixed-Signal Validation Background

$$H_r(s) = \frac{a_0 + a_1 s + a_2 s^2 + \dots + a_m s^m}{b_0 + b_1 s + b_2 s^2 + \dots + b_n s^n}$$

(7)

which satisfies

$$H_r(0) = H(0)$$

(8)

$$\frac{d^k}{ds^k} H_r(0) = \frac{d^k}{ds^k} H(0), \qquad k = 1, 2, ..., m + n$$

where  $\frac{d^k}{ds^k}H(0)$  is also known as the k-th moment of the transfer function. Hence this is also called the moment-matching method. Asymptotic Waveform Evaluation (AWE) and Padè via Lanczos (PVL) are two macromodeling algorithms based on this idea. AWE [58] explicitly computes the moments to perform the order reduction; however, the reduced model often has numerical inaccuracies which then need to be remediated using heuristic methods. PVL [59] improves on the numerical instability and provides an error bound on the accuracy of the reduced model.

So far, moment-matching algorithms yield reduced models in the frequency domain; however, recall from Section 2.1 that an analog simulator solves a set of DAE's and therefore cannot simulate a transfer function. The transfer function could be transformed into the matrix format that an analog solver accepts, but it is difficult to control the properties of the resulting matrix (for example, it might be non-passive which then leads to instability [47]). Linear projection based algorithms start with the DAE representation of the circuit, and projects that system onto a smaller linear subspace that still roughly encloses the circuit's trajectories. The intuition is that by projecting the system onto such a subspace, the model order is reduced and at the same time, major dynamics of the original circuit is preserved since most of the system's state is reachable in the smaller subspace [39]. For LTI circuits, the DAEs have a specific form due to linear properties:

19

Chapter 2. Mixed-Signal Validation Background

$$C\frac{d}{dt}x + Gx + Bu = 0$$

$$y = D^{T}x$$

(9)

The vector x represents the state variables, u the list of inputs and y the list of outputs. The reduced-order model is in the same form with new and smaller C, G, B, and D matrices that are defined by

$$C_r = W^T C V, \qquad G_r = W^T G V, \qquad B_r = W^T B, \qquad D_r = V^T D.$$

(10)

V and W are projection matrices that define the smaller subspace onto which the original system is projected [39]. Since these models look just like any other matrix that an analog simulator is intended to solve, they can be directly inserted into SPICE/fast SPICE or a mixed-mode simulator. The selection of the V and W can be made to guarantee certain desirable linear circuit properties of the resulting macromodel, such as passivity [47], balanced controllability and observability [43], stability[44], etc.

The speed up achieved by simulating the reduced order macromodel instead of the full circuit DAE is directly correlated with the amount of order reduction performed. The smaller the resulting macromodel, the faster it will simulate. Wang et. al in [35] demonstrats LTI macromodeling of a two-stage op-amp using projection-based methods. The model order is reduced from 51 to 16, and a 60x improvement in runtime is observed using HSPICE.

### 2.4.2 Nonlinear Circuit Macromodeling

Nonlinear macromodeling has the same goal as LTI macromodeling, which is finding a lower order matrix representation of an analog circuit; however, it has the additional aim of capturing some nonlinear behavior of the original DAE's as well. Macromodeling algorithms for nonlinear systems are not as mature as those of LTI systems [39]. In most cases, a particular modeling technique and model candidate are needed for each type of nonlinear behavior to be preserved in the reduced model. For example, if the behavior is linear time-varying (LTV), the Padè-like moment matching algorithm presented in [36] can be applied to preserve moments of such a system. The model candidate is a set of multirate partial differential equations. For a nonlinear behavior described by a Volterra series approximation, the NORM [41] algorithm retains the moments of the Volterra kernels by using polynomial differential equations as the model candidate. More nonlinear macromodeling algorithms are listed in Table 2.

| Method       | Model Candidate        | Behavior Retained       | Application        |

|--------------|------------------------|-------------------------|--------------------|

| QLMOR [48]   | quadratic-linear       | moments of Volterra     | weakly nonlinear   |

|              | differential equations | kernels                 | circuits           |

| ISF [37]     | time-varying phase     | oscillator phase        | oscillators        |

|              | sensitivity            | sensitivity             |                    |

| PPV [38]     | scalar differential    | oscillator phase        | oscillators        |

|              | equation               | sensitivity             |                    |

| POD [39]     | linear differential    | deviation from training | nonlinear circuits |

|              | equations              | waveforms               |                    |

| TPWL [48]    | piecewise-linear       | moments of transfer     | nonlinear circuits |

|              | differential equations | function of each        |                    |

|              |                        | linearized segment      |                    |

| ManiMor [45] | piecewise-linear       | DC and AC response      | nonlinear circuits |

|              | differential equations |                         |                    |

Table 2 – Nonlinear macromodeling algorithms

The ad hoc nature of the above collection of algorithms is a good indication that nonlinear macromodeling is a difficult problem. In fact, many of these algorithms do not achieve much order reduction in their macromodels. For example, the POD method, which is based on the idea of projecting the nonlinear state space onto a linear sub-space, may return a macromodel that's as large as the full model [39]. The ManiMor algorithm fairs a little better. Gu et. al [45] [46] proposes that the trajectories of a nonlinear circuit are restricted not to a linear subspace, but more likely to a nonlinear manifold. Intuitively speaking, since a manifold presents a more "snug" fit to the space that contains the circuit's trajectories, it is usually lower-dimensional compared to a linear sub-space. In [45], a 4-stage CML buffer with inductive peaking is shown to be order-reduced from 52 to 5 by the ManiMor algorithm.

LTI macromodeling provided nearly two orders of magnitude of analog runtime reduction; however, these order-reduced models are still not commonly used in high-level validation of mixed-signal SoC's with large digital circuits [39]. Nonlinear macromodeling, though more accurate in the sense that some nonlinearity of the original model is captured in the reduced model, is even less likely to provide the necessary simulation acceleration. Behavioral modeling is a form of macromodeling that relaxes the stringent requirement of accuracy and the next section will focus on this approach to mixed-signal validation.

### 2.5 Behavioral Modeling

The LTI and nonlinear macromodeling methods seek to ensure that the reducedorder model faithfully captures circuit characteristics in the transistor-level description [39]. Full-chip functional validation, however, has more moderate expectation on accuracy; designers were willing to pay a price for the ability to simulate a much larger system with greater speed [1]. Behavioral modeling is a method of fulfilling this need. Behavioral models are hand-crafted (sometimes automatically generated) models written in a high-level language that require expert knowledge of the analog circuit being modeled [39]. Because the models are not derived directly from low-level transistor models, there will be some loss in accuracy [52]. The attractiveness of behavioral modeling, however, comes from the potential for 100-1000x simulation speedup [32] and at such speeds, a more complete validation of mixed-signal SoC seems more feasible. In addition, it is possible to include checking or assertions in the behavioral models to aid the validation effort. Many high-level modeling languages exist and the following discussion will be divided according to the language used.

#### 2.5.1 Simulink/Matlab

Simulink/Matlab has been a popular tool for system-level functional simulation and verification [64]. The Simulink libraries have wide-ranging fundamental building blocks including continuous time integration, derivative, state space and transfer function blocks, discrete time quantizers, filters and delay elements, mathematical operators, signal routing blocks and data visualization scopes. The system-level designers only have to select the correct blocks from the libraries, connect them and configure the simulation settings [64]. If only discrete time components exist in the model, the solver is discrete; for continuous time states, several DAE solvers are available and the user may choose between fixed step size or variable step size numerical integration methods – the variable step size integration method is a means of potential simulation acceleration. In fact, the MATLAB toolbox has been widely used (for bang-bang PLL's [65], clock/data recovery circuits [66], DC-DC regulator's [67], etc.) and is the de facto tool for discrete-time deltasigma modulator modeling [64]. A disadvantage of Simulink/Matlab is that these models must run in Matlab's simulator and cannot be easily connected to the digital system that needs to be validated in an SoC.

#### 2.5.2 SystemC-AMS

SystemC-AMS is a more recently available modeling language that has garnered some attention. This is a C++ based language that extends SystemC (a digital circuits modeling language) and provides three Modes of Computation (MoCs) – Timed Data Flow model (TDF), Linear Signal Flow model (LSF) and Electrical Linear Networks

model (ELN) [69]. TDF is a discrete-time modeling style which treats data as signals sampled in time while carrying discrete or continuous values [70]. Different blocks are allowed to have different time steps [69]. The LSF MoC enables the modeling of continuous time systems as a set of linear algebraic equations [70] – this is similar to Simulink's continuous model elements. In the ELN model, electrical primitives can be instantiated along with the rest of the design. Available primitives include [70] current/voltage sources, resistors, capacitors, inductors, transmission lines, transformers, ideal switches, etc. In literature, models of PLL's [69] have been demonstrated. Heterogeneous systems (e.g. CMOS video sensor [71], wireless sensor networks [72]) have also found SystemC-AMS to be a useful modeling language. Unfortunately, again, SystemC-AMS has its own simulator and therefore is difficult to connect to a digital system written in Verilog.

## 2.5.3 Verilog-A/Verilog-AMS/VHDL-AMS

These languages, like MATLAB/Simulink and SystemC-AMS, are capable of handling continuous as well as discrete systems; but they have the added advantage of easier integration into circuit design tools such as Cadence, which has mixed-mode simulation capabilities [64], making the connection to a digital system relatively easy. Verilog-A is an extension of Verilog-HDL and introduces analog functions such as integration, differentiation, delay, transition, Laplace transform and Z transform [74]; and its solver for continuous systems is similar to DAE solvers found in SPICE simulators. Verilog-AMS and VHDL-AMS are the union of Verilog/VHDL and Verilog-A, and therefore inherit the ability to handle both digital and continuous time analog signals [73]. Models of diodes [75], gain amplifiers [74], PLL's [73], delta-sigma modulators [76], etc. have been prototyped.

Labeled Hybrid Petri Nets (LHPN) [60] [62] is an interesting algorithm that automatically generates finite state machine (FSM) based models in Verilog-AMS. It relies on the concept of system identification [50] [51]. The general idea is to view the

circuit to be modeled as a black box, measure the circuit's output waveforms corresponding to a set of input training waveforms, and fit a parameterized model that relates the input and output.

All the languages here have a SPICE-like analog solver. Even though it is most likely solving a much smaller problem than a full circuit DAE, once the solver is invoked, it must execute all the steps described in Section 2.1 in order to solve differential equations. Therefore, using the continuous time analysis capabilities of these languages will result in longer simulation times compared to pure digital simulation. For example, David in [68] presents a PLL Verilog-AMS model that simulates approximately 125x faster than its transistor-level representation.

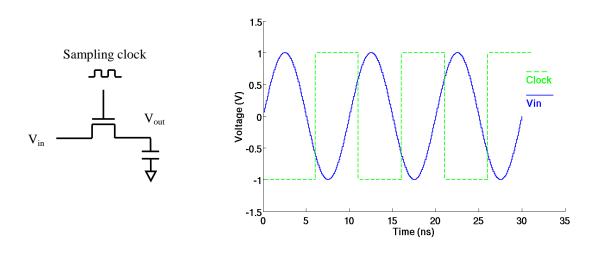

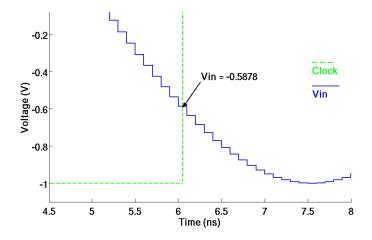

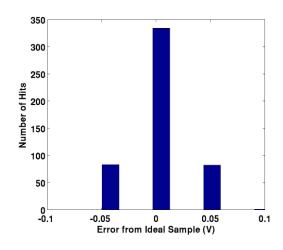

## 2.5.4 Digital Verilog with Real

Lastly, Verilog simulators with "real" value interconnect wires and basic algebraic capability have existed for several years [80] and modeling using digital languages (VHDL/Verilog/SystemVerilog) with these extended functionality has been demonstrated. Digital Verilog is inherently discrete-time, hence sampled data systems have a natural fit into the simulation environment [77]. The format of sampled data is illustrated in Figure 2. The signal updates periodically and at each update, the signal has a value and that value is held constant until the next update.

Figure 2 – Sampled data representation of continuous time signal

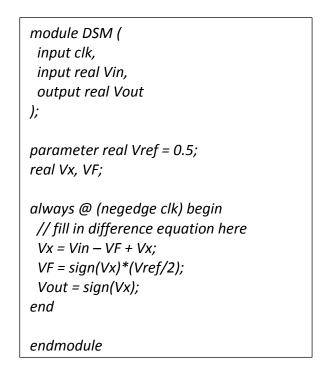

Some analog systems such as delta sigma modulators (DSM) and switched capacitor (SC) filters can be modeled with sampled data without much difficulty. Take the first order DSM in Figure 3 as an example. The output of the modulator will be sampled directly by a digital system and when properly designed, all nodes will settle when the clock edge arrives. In other words the system is synchronous. The same can be said of SC filters. Figure 4 shows the corresponding signal flow graph for the first order DSM assuming  $C_F = C$ .

Figure 3 – Switched capacitor implementation of 1<sup>st</sup> order DSM

Figure 4 – Signal flow graph for 1<sup>st</sup> order DSM

A difference equation that describes the system can be extracted from the graph as below:

$$V_{x}(k+1) = V_{in}(k) - V_{F}(k) + V_{x}(k)$$

(11)

Chapter 2. Mixed-Signal Validation Background

where

$$V_F(k) = \begin{cases} \frac{V_{ref}}{2}, V_{\chi}(k-1) > 0\\ -\frac{V_{ref}}{2}, V_{\chi}(k-1) < 0 \end{cases}$$

Using SystemVerilog as an example, the pseudo-code for the first order DSM is shown in Listing 1.

Listing 1 – Example model of first order delta-sigma modulator

Recall from Section 2.5 that MATLAB has been used extensively to model delta sigma modulators and switched capacitor filters. Here, digital Verilog languages with real number extensions provide similar capabilities. For other continuous time analog systems, various transformation techniques to approximate them as discrete-time systems can be found in literature. The most common is the bilinear transform [77], which converts analog transfer functions to discrete-time difference equations using a sufficiently high sampling rate (by the Nyquist criterion). The use of the forward Euler integration

technique to perform the conversion has also been demonstrated in [80]. A variety of circuits have been modeled using the above concepts; these circuits include successive approximation ADC's [77], auto-gain control circuit (AGC) [77], switched capacitor amplifiers [80], phase-interpolators [52], oscillators [78] and all-digital PLL's [79].

## 2.6 Summary

Validation of a mixed-signal SoC requires the concurrent simulation of both analog and digital in order to verify the complex interaction between the two [76]. Unfortunately, basic analog and digital simulators are inadequate for this job. The digital simulator cannot solve DAE's and the analog simulator is too slow to compute waveforms for the digital back-end, which nowadays is likely to contain several million gates [78]. This chapter examined several research areas that address the issue of mixedsignal validation.

Fast SPICE experiments with the ideas of cleverer matrix manipulation and computation to speed up analog simulation, as well as efficient digital structure recognition and storage to allow for relaxation on digital simulation accuracy and hence improved digital simulation speed in an analog environment. Currently, however, they often cannot provide adequate simulation speed for large mixed-signal SoC [80]. Macromodeling and piecewise-linear simulators try to reduce the complexity of the nonlinear system that analog solvers need to solve and hence accelerate simulation. Mixed-mode simulation leverages the efficiency of specialization, and advocates for the preservation of accuracy for analog as well as speed for digital. It accomplishes its goals by bringing together an analog simulator and a digital engine through appropriate continuous/discrete conversion interfaces and timing synchronization mechanisms.

Behavioral modeling seems to have the most potential in terms of simulation time reduction (up to three orders of magnitude). Many modeling languages and model examples have been reviewed; some are faster, others are more easily connected to digital designs. Overall, the models are varied. It is not uncommon for engineers to have their favorite language and write what was needed at the moment [80]. This ad hoc nature causes compatibility issues and is a detriment to the efficiency of the validation process. What's presented in the rest of this thesis is a set of guidelines that regularizes the process of creating behavioral models in an event-driven environment as well as an investigation of the applicability of these guidelines to mixed-signal SoC validation.

# Chapter 3

# **Behavioral Modeling Approach**

Based on the information provided in Chapter 2, behavioral modeling is currently the only approach that might be fast enough for mixed-signal SoC validation. In order for behavioral modeling to work well, the models must satisfy several criteria. When behavioral models are inserted into the top-level design for simulation, correlation between system success/failure and sub-circuit or interface correctness/error is dependent upon the equivalence of the behavioral models and their circuit implementation. Example equivalence checking methods include transfer matrix matching under linear system assumption [81], simulation trace matching [61], and finite-state-machine-based macromodel generation followed by state space exploration [83]. Regardless of the checking method used, to have the models verified at all stipulates that the pins of the model must match those of the schematics. This is the first criterion. Second, as discussed in Chapter 2, writing behavior models to raise abstraction level is a commonly-accepted solution to increase the simulation speed by hiding low-level details of the architecture [72]. Therefore, the models should simulate relatively quickly. Lastly, the mission of functional validation prior to tape-out is not only checking correctness of wire connections and signal routing, but also making a rough performance analysis "over night" [76]. Hence, capturing important circuit dynamics in the models is highly desirable.

With these goals in mind, this chapter will describe the necessary elements to writing behavioral models for SoC validation. First, a modeling language needs to be chosen and the reasons for choosing SystemVerilog as an example in this thesis will be discussed in Section 3.1. Then, in order to fit into a digital simulation environment that's unidirectional, proper circuit partitioning is necessary and will be the topic of Section 3.2. Next, even though SystemVerilog is supplemented with real number capabilities, it is still a discrete-time simulator, and therefore an appropriate method of representing analog signals is presented in Section 3.3. Lastly, given the proposed signal representation, the models must compute their outputs in an efficient fashion and an approach will be described in Section 3.4. Throughout all these steps, designer's knowledge is indispensable and will be relied upon to aid the modeling of analog circuits.

# 3.1 Modeling Language

Among the available modeling languages described in Section 2.5, SystemVerilog is used to write all the specific examples that follow; however, the methods presented in this thesis can be applied to any event-driven simulator with real number capabilities. The choice of this particular modeling language is rather arbitrary, but SystemVerilog is not without its many advantages. The digital languages (VHDL/Verilog/SystemVerilog) extended with real numbers have the potential for at least an order of magnitude increase in speed compared to Verilog-A/Verilog-AMS/VHDL-AMS [52]. Simulink and SystemC-AMS can achieve similar simulation speed at the system level, but models written in these languages have little resemblance to the actual physical implementation [9] and are very much disconnected with circuit design tools. SystemVerilog, on the other hand, is currently the go-to language for digital validation among all the digital modeling languages, and therefore eliminates the need to recreate the digital portion of the SoC for a different platform. Due to the above benefits, as well as in anticipation of the continued increase in analog/digital interaction and the size of mixed-signal SoC (and the

commensurate need for scalability), SystemVerilog is chosen as the representative modeling language.

# 3.2 Circuit Partitioning

Since the behavioral models need to run in a digital simulator - SystemVerilog to be specific – the first challenge to tackle is related to the unidirectional modeling framework of the digital environment. In general, digital gates are unidirectional [16] – the output of one gate drives the input of the next gate and the output of the driven gate doesn't affect the output of the driving gate. The digital simulator is designed to deal with unidirectional signal propagation and uses the fact that a gate's input changes cause it to re-evaluate that gate.

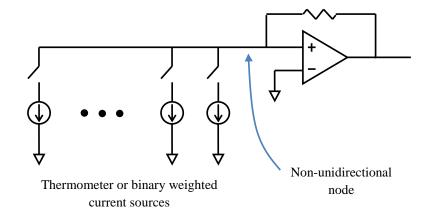

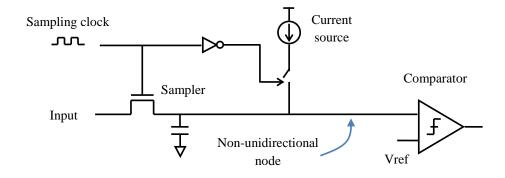

With analog circuits, however, unidirectionality is not guaranteed. A good example is current summing nodes. In a current DAC (Figure 5), for example, the output of the current sources is current, while the feedback resistor drives a voltage back to the input node of the buffer. This causes conflict. In another example, the frontend of a single-slope ADC (Figure 6) could be intuitively split into a sampler with a sampling cap, a switchable current source and a comparator. Equivalence checking will work under this particular way of partitioning, but the input of the comparator would have two drivers – the sampler's voltage output and the current source's current output. The current source injects charge into the capacitor, which then sets the voltage. Like the feedback resistor in the DAC example, this current source creates a non-unidirectional node at the comparator input.

Figure 5 – Current summing node in DAC

Figure 6 – Current summing node in single-slope ADC frontend

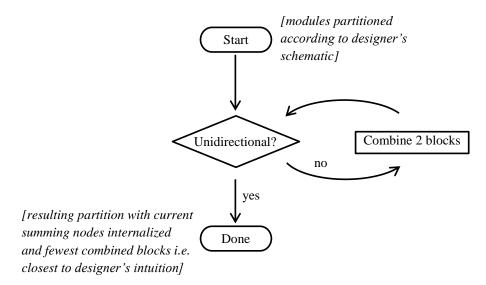

In both examples, a current summing node cannot be on the boundary of a standalone module; instead, circuit blocks must be combined so that these nodes are absorbed into the interior of a module. Equivalence checking would then be performed on these combined modules. For the current DAC, all the current sources need to be combined into a cell with a single current output that drives the buffer. Furthermore, by design, the input of the current buffer is a good virtual ground, hence the voltage at this node doesn't move much. With this design intuition, the buffer with the feedback resistor must be modeled as one block with a current input and voltage output. In the single-slope ADC frontend, the sampler and current source must be combined to form a block with a single voltage output, which then drives the comparator. It should be noted that the schematics

can retain hierarchy, but it is important to have a wrapper for the combined block that can be checked against the functional model. The implication for validation using a digital simulator then is that hierarchies that contain non-unidirectional nodes should be carefully planned as early as the schematic design phase.

A procedure to determine the appropriate boundary of analog wrapper modules is illustrated in Figure 7. To arrive at a model that has closer resemblance to the physical implementation, start with existing blocks in the schematic. Since these blocks most likely made intuitive sense to the analog designer, the models will be able to leverage the mathematical tools that were used, in the first place, to design these blocks to better capture the circuit dynamics. Non-unidirectional nodes usually occur when multiple current sources are summed or both current and voltage signals co-exist at a single point. A circuit designer would know best where these nodes are located in a schematic. If nonunidirectionality exists, combine as few of the blocks as possible until all current summing nodes are within a module. Smaller blocks are preferred since they are more likely to have well established theories that encapsulate their analog behaviors and hence are more beneficial towards the modeling of circuit dynamics.