# FINE-GRAIN IN-MEMORY DEDUPLICATION FOR LARGE-SCALE WORKLOADS

# A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

John Peter Stevenson December 2013

# © 2013 by John Peter Stevenson. All Rights Reserved. Re-distributed by Stanford University under license with the author.

This work is licensed under a Creative Commons Attribution-Noncommercial 3.0 United States License. http://creativecommons.org/licenses/by-nc/3.0/us/

This dissertation is online at: http://purl.stanford.edu/rp831pj6163

| I certify that I have | read this dissertation  | and that, in my  | opinion, it is fully | <sup>7</sup> adequate |

|-----------------------|-------------------------|------------------|----------------------|-----------------------|

| in scope and quality  | y as a dissertation for | the degree of Do | octor of Philosoph   | ıy.                   |

#### Mark Horowitz, Primary Adviser

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

**David Cheriton**

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

**Patrick Hanrahan**

Approved for the Stanford University Committee on Graduate Studies.

Patricia J. Gumport, Vice Provost for Graduate Education

This signature page was generated electronically upon submission of this dissertation in electronic format. An original signed hard copy of the signature page is on file in University Archives.

### Abstract

Memory is a large component of computer system cost and current trends indicate this cost is increasing as a fraction of the total. Emerging applications such as inmemory databases, virtual machines, and big-data key-value stores demand more memory relative to compute. Some of these high-memory applications incidentally store many duplicate values in memory: in some cases, duplicates account for over 75% of the total. Recent work on the HICAMP architecture provided a sophisticated hardware mechanism for memory deduplication to implement memory versioning, but without support for current software stacks. This thesis extends work on HICAMP by evaluating a deduplicated memory that is compatible with existing hardware and software. Memory content from actual workloads indicates that deduplicated memory effectively doubles capacity. After understanding the baseline cost-benefit tradeoff in terms of capacity, performance, and energy, this work proposes novel optimizations for machines with deduplicated memory. These optimizations reduce memory traffic and improve performance relative to both the baseline deduplicated memory and, in many cases, relative to the original machine. Energy consumption is reduced because memory devices are reduced with no penalty to performance. Further, deduplication reduces data transfer and improves performance for certain scientific applications. This thesis argues that in-memory deduplication is warranted by its own benefits, which are likely to grow in the future, and that it enables low-cost memory snapshots, as in the HICAMP architecture.

## Acknowledgments

Dedicated to my wife, Siejen.

Most of all, this thesis is a product of the family that has supported me. Completing this work is a significant occasion along a longer trajectory – an arc of life that I have been privileged to enjoy, and that I hope to repay in kind. Necessarily, this trajectory begins with my mother and father, both of whom deserve first acknowledgement. Mom and Dad – thank you both, for raising me, putting up with me, and most of all, for inspiring me to go farther than I dared think possible.

Another significant turning point in my life was the day I met my future wife, Siejen – a day and a time that I will remember fondly, forever. Now, years later, I love her more and can say that she has made me a better man. My life has been richer and more fulfilling during the time I have spent with her. Siejen – thank you for loving me, and for supporting me through this program.

Mom and Dad – you let me wander far from home to seek my fortune. Siejen – you joined me on this journey, for better or for worse, and the journey has taken you far from home also. Many years later, I have completed this thesis, and I have also found a new home: namely, that is wherever my best friend and wife happens to be – I am at home, and safe. Personally, I have derived a great amount of satisfaction from completing this task, and I want you all to be likewise proud of it, both now, and as I continue this work – you gave me the freedom to walk down this path.

Siejen and I have benefitted, both, from the support of the rest of our respective families. To Debbie and Bill Edwards, my sister, and her husband, thank you for opening your house to us and for inspiring me, at an early age, toward my future alma mater, the U.S. Naval Academy. To Shong Yin, Ph.D., and Susing Yin, Siejen's brother and sister, thank you for providing good advice and friendship during the course of this work. And finally, to Robert and Nancy Yin, Siejen's parents, thank you for believing in me and taking me in as a member of your family.

I owe a debt of gratitude to the U.S. Naval Academy, to its staff and faculty, and to the U.S. Navy. At age eighteen, I knew the advantages and disadvantages of both active and passive SONAR – critical knowledge for my future career in submarines – but, I did not know where Stanford was or anything much about such opportunities. Tom Brennan – thank you for suggesting that I pursue graduate education, I doubt very much I would have thought of that myself. Larry Tankersley – thank you for teaching the most wonderful physics class I can imagine, and if someday I have the privilege of teaching, I hope to emulate your style. Carl Wick – thank you for being my advisor and best advocate: you helped me navigate one of my early successes.

To Stanford, thank you for filling in the gaps in my undergraduate knowledge. Tom Lee – I always knew that causality had to be a problem with the "ideal opamp" model: I thoroughly enjoyed your courses, and learned a great amount. Umran Inan – you laid to rest another engineering model that had always bugged me, for essentially the same reason: I finally grok that voltage does not appear instantaneously, thanks to you, and of course, James Clerk Maxwell. David Miller – thank you for passing me. I so desperately wanted to take a course in quantum mechanics, having no idea what it was, and being totally unprepared for the material. Of course, you

inspired my short foray into song writing, and to claim rightful authorship for eternity, I now, as befits such mathematically inspired work, using LATEX, give the lyrics, sung to the music of *Jingle Bells:*<sup>1</sup>

Ohhh quantum well go to hell, I hate Erwin Schödinger  $\nabla^2 \psi$  makes me cry, divide h by  $2\pi$

During this time, I have made many good friends, and among whom, I am humbled and honored to be included as *their* colleague. Omid Azizi – thank you for being my friend and officemate, and thank you for lending me your analytical mind and incredible intelligence.<sup>2</sup> Zain Asgar – thank you for being my friend, for being a fellow circuit optimization enthusiast, and for coming up with all the good ideas on how to divert my time toward better uses, such as camping trips and balloon festivals. Ofer Shacham – thank you for being so welcoming when I joined Mark's group; I know we have followed similar paths from very different starting points and I look forward to knowing your family and knowing of your successes in the future.

The work on this thesis has also been influenced by the ongoing work at a small company, HICAMP Systems. Small, though it may be, the combined intellectual quotient of its staff is formidable. Alex Solomatnikov and Amin Firoozshahian – thank you for blazing the trail at HICAMP and for teaching me the basics, or advanced basics, of computer architecture. Mahesh Maddury, Chandan Egbert, and Christophe Joly – thank you for bringing real experience to the table and for steering a safe course for our fledgling company.

Along this path I have learned more from one faculty in particular, and I hope one day to pass on some of his wisdom – both academic, and life. Mark Horowitz, thank you for taking me on as your student, and for inspiring me. You delivered

<sup>&</sup>lt;sup>1</sup> The lyrics are somewhat hyperbolic, I actually love him, his equation, and his cat.

<sup>&</sup>lt;sup>2</sup> i.e. Thank you for pre-screening all my ideas.

my first lecture at Stanford, and I will always remember it. It won't be so vivid in the retelling, but I admired the delivery which turned the complex into the simple and unveiled powerful ideas with large amounts of engineering leverage. It started by proposing to take an idea, a big idea, and pack it into a little tiny rectangle. On that rectangle, the contents of the idea would be drawn in basic primary colors, and particular significance would be given to certain combinations of such colors, such as red drawn over green. I had no idea, but it turns out that microchips are just drawings, printed in layers of metal, on top of silicon. And making microchips is as simple as making such drawings, where the colors distinguish the layers and red over green makes a transistor. I was hooked, and that was just a beginning – there was more to come, much more. Mark, you've been generous to me, and all of your students – thank you.

Finally, this work is really the byproduct of the formidable intellect and visionary creativity of David Cheriton. I chose to do a Ph.D. at Stanford not just because it is a premier institution, but also because they had given me a very generous offer of financial support, namely, the David R. Cheriton Stanford Graduate Fellowship. This was somewhat of a better offer of financial support than I had received elsewhere, and I already had it in my mind that Stanford offered a tighter link to what is actually happening in the electronics industry. Early in my Ph.D. career, Siejen and I happened to cross paths with David in the middle of downtown Palo Alto – in one of my better life moments, I failed to not notice that this was happening, so I decided to introduce myself and my wife. In this conversation David said he had a new project, known as HICAMP, and asked if I would be interested. At the time, I knew a little bit about computer architecture, enough to recognize HICAMP as being unorthodox, brilliant, and quite fascinating. And the last of those qualities was enough for me – my only criteria was to do interesting work. David Cheriton – thank you for generously providing my Stanford Graduate Fellowship which supported me at Stanford for five

years and thank you for bringing me on board to work on HICAMP. I have enjoyed it immensely and I find every aspect of it incredibly fascinating.

I hope you the reader will agree: what follows is both interesting, and somewhat surprising. In these acknowledgements, my meaning of inspired is twofold: academic, of course, but also figurative – for example: the stars at night above the ship's swaying deck inspired me to think of mankind forging a path on new spacegoing vessels, through the galaxies, (or some such); and of course, for now I will keep to academic writing. Mark Horowitz and David Cheriton, thank you for inspiring this work.

## Contents

| $\mathbf{A}$ | bstra | nct                                        | V  |

|--------------|-------|--------------------------------------------|----|

| $\mathbf{A}$ | ckno  | wledgments                                 | vi |

| 1            | Inti  | roduction                                  | 1  |

|              | 1.1   | Cost of Memory                             | 2  |

|              | 1.2   | Efficient Use of Memory                    | 5  |

|              | 1.3   | Duplicates in Actual Workloads             | 6  |

|              | 1.4   | Deduplicated Memory: Performance and Power | 7  |

|              | 1.5   | Deduplicated Sparse Matrices               | 8  |

|              | 1.6   | HICAMP Architecture                        | 9  |

|              | 1.7   | Summary                                    | 11 |

| 2            | Dec   | duplicated Memory                          | 12 |

|              | 2.1   | Deduplicated Memory Organization           | 13 |

|              | 2.2   | Processor Reads and Writes                 | 14 |

|              | 2.3   | Content Lookup                             | 16 |

|              | 2.4   | Hash Bucket Overflows                      | 18 |

|              | 2.5   | Deduplication and Overhead                 | 21 |

|              | 2.6   | Duplicates In Real Workloads               | 22 |

| 0.7            |                                                                                                   |                                                                                                                                                                                                                                                                                                                                  |                                                          |

|----------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 2.7            | Opera                                                                                             | ting System Support                                                                                                                                                                                                                                                                                                              | 25                                                       |

| 2.8            | Summ                                                                                              | nary                                                                                                                                                                                                                                                                                                                             | 28                                                       |

| 3 Pei          | rformaı                                                                                           | nce Optimizations                                                                                                                                                                                                                                                                                                                | 29                                                       |

| 3.1            | Direct                                                                                            | Translation Buffer                                                                                                                                                                                                                                                                                                               | 30                                                       |

| 3.2            | Deduj                                                                                             | plicated Cache                                                                                                                                                                                                                                                                                                                   | 31                                                       |

|                | 3.2.1                                                                                             | Coherency                                                                                                                                                                                                                                                                                                                        | 32                                                       |

|                | 3.2.2                                                                                             | Physical Resources                                                                                                                                                                                                                                                                                                               | 34                                                       |

|                | 3.2.3                                                                                             | Content Lookup                                                                                                                                                                                                                                                                                                                   | 38                                                       |

|                | 3.2.4                                                                                             | In-Cache Allocation                                                                                                                                                                                                                                                                                                              | 38                                                       |

|                | 3.2.5                                                                                             | Zombie Suppression                                                                                                                                                                                                                                                                                                               | 40                                                       |

|                | 3.2.6                                                                                             | Prefetching                                                                                                                                                                                                                                                                                                                      | 41                                                       |

|                | 0 0 <b>-</b>                                                                                      | Multi-Bank Implementation                                                                                                                                                                                                                                                                                                        | 42                                                       |

|                | 3.2.7                                                                                             | With Dank Implementation                                                                                                                                                                                                                                                                                                         | 42                                                       |

| 3.3            |                                                                                                   | nary                                                                                                                                                                                                                                                                                                                             |                                                          |

|                | Summ                                                                                              |                                                                                                                                                                                                                                                                                                                                  | 44                                                       |

|                | Summ                                                                                              | nary                                                                                                                                                                                                                                                                                                                             | 44                                                       |

| Pei            | Summ                                                                                              | nary                                                                                                                                                                                                                                                                                                                             | 44<br><b>45</b>                                          |

| Pei            | Summ<br>rformai<br>Evalua                                                                         | nary                                                                                                                                                                                                                                                                                                                             | 44<br><b>45</b><br>47                                    |

| Pei            | Summ<br>rformai<br>Evalua<br>4.1.1                                                                | nary                                                                                                                                                                                                                                                                                                                             | 44<br>45<br>47<br>47<br>48                               |

| . Pei          | Summ<br>Formal<br>Evalua<br>4.1.1<br>4.1.2                                                        | nary                                                                                                                                                                                                                                                                                                                             | 44<br>45<br>47<br>47<br>48<br>49                         |

| . Pei          | Summ<br>Evalua<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4                                                | nary                                                                                                                                                                                                                                                                                                                             | 44<br>45<br>47<br>47<br>48<br>49<br>50                   |

| <b>Per</b> 4.1 | Summ<br>Evalua<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4                                                | nary                                                                                                                                                                                                                                                                                                                             | 44<br>45<br>47<br>48<br>49<br>50<br>52                   |

| 4.1            | Summ<br>Evaluation 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Perfor                                     | nary  nce and Power ation Methodology  Simulated Machine Configurations  Performance Model  Performance Metrics  Simulated Workloads                                                                                                                                                                                             | 44<br>45<br>47                                           |

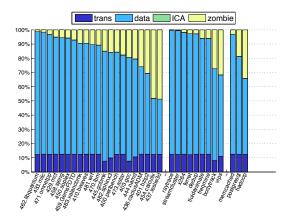

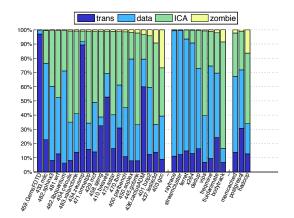

| 4.1            | Summ Evalua 4.1.1 4.1.2 4.1.3 4.1.4 Perfor 4.2.1                                                  | nary  nce and Power ation Methodology  Simulated Machine Configurations  Performance Model  Performance Metrics  Simulated Workloads  Synthetic                                                                                                                                                                                  | 44<br>45<br>47<br>48<br>49<br>50<br>52<br>53<br>54       |

| 4.1            | Summ<br>Evaluation 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Perfor<br>4.2.1<br>4.2.2                   | nce and Power ation Methodology Simulated Machine Configurations Performance Model Performance Metrics Simulated Workloads Synthetic Standard CPU Benchmarks                                                                                                                                                                     | 44<br>45<br>47<br>48<br>49<br>50<br>52<br>53             |

| 4.1            | Summ<br>Evaluation 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Perfor<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4 | nary  Simulated Power  ation Methodology  Simulated Machine Configurations  Performance Model  Performance Metrics  Simulated Workloads  mance  Synthetic  Standard CPU Benchmarks  Datacenter Workloads | 44<br>45<br>47<br>48<br>49<br>50<br>52<br>53<br>54<br>56 |

| 5 | Spa | rse Ma  | atrix-Vector Multiply                  | 62 |

|---|-----|---------|----------------------------------------|----|

|   | 5.1 | Hierar  | chical Deduplication                   | 63 |

|   | 5.2 | Dedup   | olicated Sparse Matrix Storage         | 66 |

|   |     | 5.2.1   | Row Major Array                        | 67 |

|   |     | 5.2.2   | Quad-Tree Symmetric                    | 67 |

|   |     | 5.2.3   | Hierarchical Compressed Sparse Row     | 69 |

|   |     | 5.2.4   | Hierarchical Coordinate Format         | 69 |

|   |     | 5.2.5   | Non-Zeros Dense Format                 | 70 |

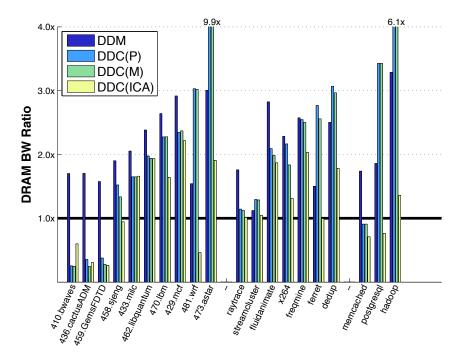

|   | 5.3 | Sparse  | e Matrix Compaction                    | 71 |

|   |     | 5.3.1   | Compaction Results                     | 72 |

|   |     | 5.3.2   | Storage Bounds                         | 73 |

|   | 5.4 | Dedup   | blicated Sparse Matrix-Vector Multiply | 74 |

|   |     | 5.4.1   | SpMV Evaluation Methodology            | 75 |

|   |     | 5.4.2   | SpMV Results                           | 78 |

|   | 5.5 | Iterate | or Register Hardware                   | 80 |

|   | 5.6 | Iterate | or Register SpMV                       | 82 |

|   | 5.7 | Sparsi  | ty Oblivious Algorithms                | 84 |

|   |     | 5.7.1   | Sparse Vector Add                      | 85 |

|   |     | 5.7.2   | General Matrix-Matrix Multiply         | 86 |

|   |     | 5.7.3   | Sparsity and Cache Oblivious           |    |

|   |     |         | Tree-Recursive Matrix-Matrix Multiply  | 87 |

|   | 5.8 | Summ    | ary                                    | 89 |

| 6 | HIC | CAMP    | and Related Work                       | 91 |

|   | 6.1 | The H   | TICAMP Architecture                    | 92 |

|   |     | 6.1.1   | The Need for Parallel Machines         | 92 |

|   |     | 6.1.2   | Transactional Memory                   | 94 |

|    |        | 6.1.3   | Multi-Versioned Memory        | 95  |

|----|--------|---------|-------------------------------|-----|

|    |        | 6.1.4   | HICAMP Memory Model           | 96  |

|    |        | 6.1.5   | Atomic Segment Update         | 98  |

|    |        | 6.1.6   | Advantages of HICAMP          | 99  |

|    | 6.2    | Relate  | ed Work                       | 100 |

|    |        | 6.2.1   | Page Deduplication            | 100 |

|    |        | 6.2.2   | Exploiting Zero Values        | 101 |

|    |        | 6.2.3   | In Memory Compression         | 101 |

|    |        | 6.2.4   | Sparse Matrix-Vector Multiply | 103 |

|    | 6.3    | Summ    | ary                           | 106 |

| 7  | Cor    | nclusio | n                             | 108 |

| Bi | ibliog | graphy  |                               | 112 |

## List of Tables

| 2.1 | Read and Write Sequences                                   | 15  |

|-----|------------------------------------------------------------|-----|

| 2.2 | In-Memory Content Lookup                                   | 17  |

| 2.3 | Hash Table Notation                                        | 18  |

| 2.4 | Duplicates in Real Workloads                               | 23  |

| 3.1 | Cached Reference Count States                              | 34  |

| 3.2 | DDC Physical Resources                                     | 35  |

| 3.3 | Translation and Data Line Eviction for In-Cache Allocation | 39  |

| 4.1 | Common Machine Parameters                                  | 48  |

| 4.2 | Individual Machine Configurations                          | 48  |

| 4.3 | Overall Results: DDM and DDC-ICA                           | 52  |

| 4.4 | Synthetic Benchmark Results: DDM and DDC-ICA               | 53  |

| 4.5 | Average speedup for all workloads and machines             | 54  |

| 4.6 | Average bandwidth for all workloads and machines           | 54  |

| 4.7 | Line Statistics Comparison                                 | 59  |

| 4.8 | Power Savings from Deduplicated Memory                     | 59  |

| 5.1 | Comparison of Deduplicated Matrix Formats                  | 72  |

| 5.2 | SpMV Machine Specifications                                | 75  |

| 5.3 | HCOO Compaction and SpMV Speedup                           | 79  |

| 6.1 | Comparison of Non-Symmetric SpMV Compaction Techniques     | 106 |

## List of Figures

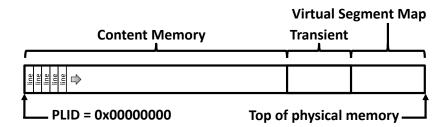

| 2.1 | Deduplicated Memory Layout                                     | 13 |

|-----|----------------------------------------------------------------|----|

| 2.2 | Address Translation and Content Deduplication                  | 14 |

| 2.3 | Write Sequence Dependencies                                    | 15 |

| 2.4 | Hash Array Layout                                              | 16 |

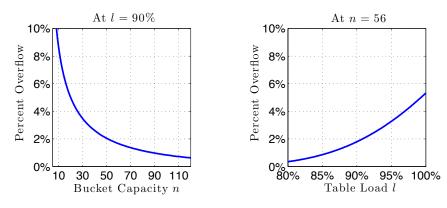

| 2.5 | Minimal Overflows                                              | 20 |

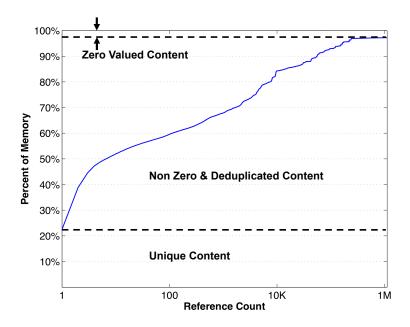

| 2.6 | Cumulative Reference Count Histogram                           | 24 |

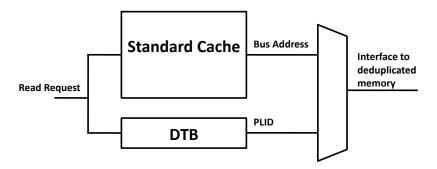

| 3.1 | Direct Translation Buffer                                      | 30 |

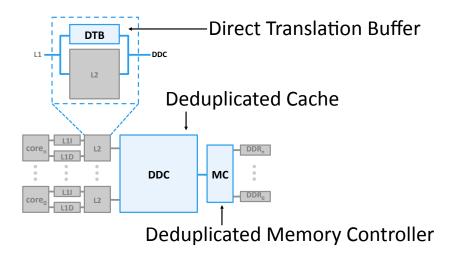

| 3.2 | CPU With DDC and DTB                                           | 31 |

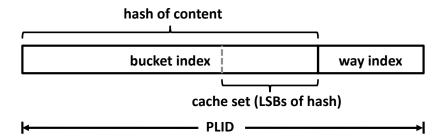

| 3.3 | PLID Composition                                               | 37 |

| 3.4 | Conceptual Illustration of a Deduplicated Cache                | 37 |

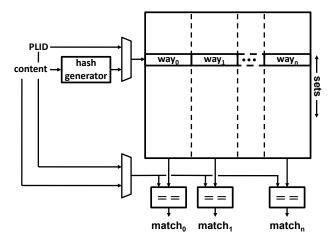

| 4.1 | SPEC CPU 2006: Compaction & Speedup Results                    | 55 |

| 4.2 | PARSEC & Datacenter Applications: Compaction & Speedup Results | 55 |

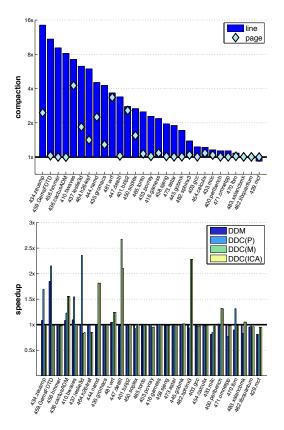

| 4.3 | Bandwidth Results                                              | 56 |

| 4.4 | DDC-P: Line Statistics                                         | 59 |

| 4.5 | DDC-ICA: Line Statistics                                       | 59 |

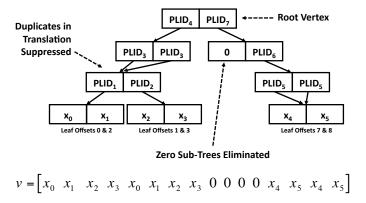

| 5.1 | Hierarchically Deduplicated Vector                             | 64 |

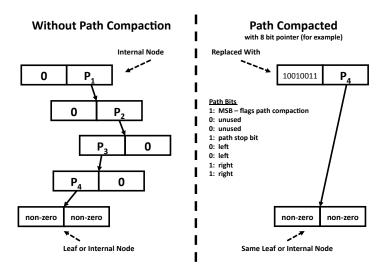

| 5.2 | Path Compaction                                                | 65 |

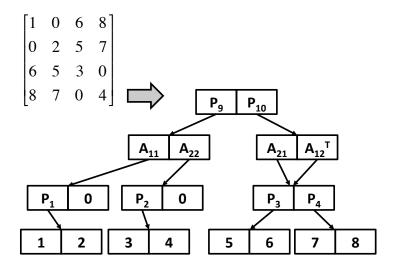

| 5.3 | Quad-Tree Symmetric Matrix                                     | 68 |

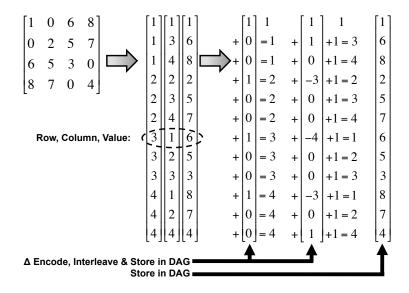

| 5.4  | Hierarchical Coordinate Encoding                                   | 70 |

|------|--------------------------------------------------------------------|----|

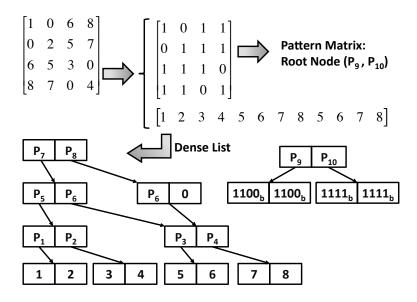

| 5.5  | Non-Zeros Dense Format                                             | 71 |

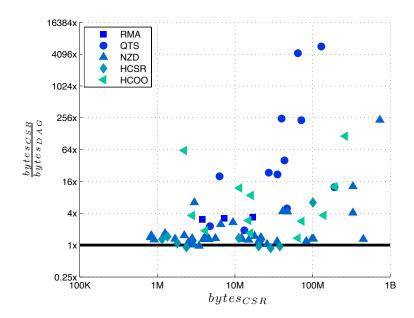

| 5.6  | Sparse Matrix Compaction Results                                   | 73 |

| 5.7  | DAG Traversal Code                                                 | 76 |

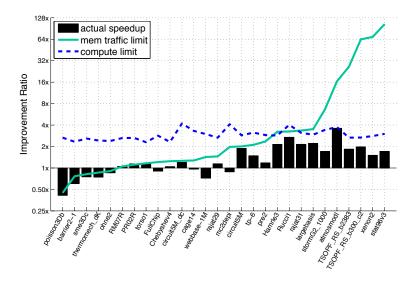

| 5.8  | SpMV Speedup and Performance Limits                                | 80 |

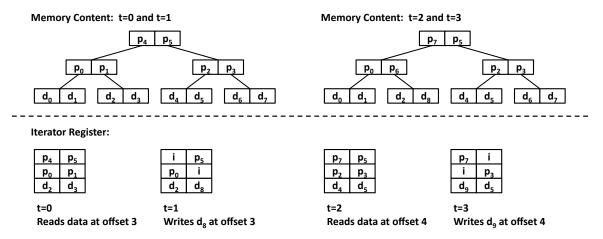

| 5.9  | Iterator Register Overwriting Portions of a DAG                    | 81 |

| 5.10 | SpMV Using an Iterator Register                                    | 83 |

| 5.11 | Sparsity Oblivious Vector Addition                                 | 85 |

| 5.12 | Sparsity and Cache Oblivious Tree-Recursive Matrix-Matrix Multiply | 87 |

|      |                                                                    |    |

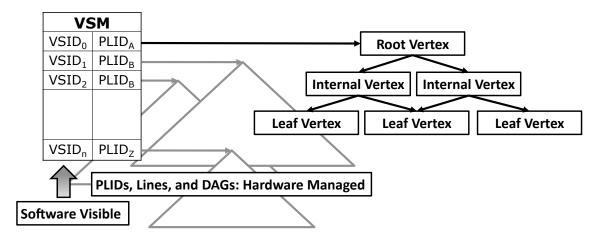

| 6.1  | HICAMP Architecture Memory Layout                                  | 96 |

| 6.2  | HICAMP Virtual Segment Map                                         | 97 |

## Chapter 1

#### Introduction

Computer technology has advanced at an ever increasing rate, a trend referred to as "Moore's Law." This increasing rate of return has been so reliable that we have come to believe that it is inevitable, but, continued advances require solving ever more difficult problems. Technology trends indicate that demand for memory capacity is growing at an increased rate while growth in capacity – Moore's Law – is slowing. To address this issue, this thesis studies deduplicated memory – namely, a computer memory that eliminates duplicate values to provide increased memory capacity. Historically, deduplication has not been used for main memory and there is very little on this topic in the literature. In-memory deduplication was first proposed in a different context, namely, to provide architectural support for parallel programs. Prior work on the HICAMP architecture [24] had used deduplication to provide efficiently versioned instances of memory. This thesis extends this prior work and applies deduplication to current CPU memory systems. The results indicate that deduplication provides effectively twice the capacity for many large-scale applications and that it also saves power. Although a significant departure from mainstream memory architecture, current trends may compel its use to increase capacity – once implemented, deduplication also opens the door to many further innovations, such as HICAMP.

#### 1.1 Cost of Memory

Memory has always been a significant cost in computer systems. Each new generation of memory technology requires an investment, but the size of that investment is now growing relative to the capacity increase delivered. At the same time, programmers have become accustomed to allocating large amounts of memory without worrying very much about its cost. The rise of internet technology, granting near ubiquitous access to communication, entertainment, and commerce, is fueling unprecedented demand for compute resources on many frontiers. This demand, in turn, has given rise to "cloud service providers" who specialize in providing the compute infrastructure and in hosting third-party applications. In the wake of this, a new sector, referred to as "big-data analytics" has emerged – these companies collect large amounts of seemingly trivial data and try to extract useful information. Collectively, these trends are driving an increased demand for memory.

In more detail, driven by emerging applications such as in-memory databases and key-value stores and by techniques such as server consolidation and virtualization, demand for memory is increasing relative to compute [47]. In-memory databases and key-value stores use terabytes of memory to minimize or completely avoid disk access thereby providing increased performance – in these applications, the ratio of memory to compute is very high. Further, memory is a significant cost in datacenters which run large-scale applications, such as the web services provided by Google or LinkedIn, and which provide hosting services, such as Amazon's Elastic Compute Cloud. The datacenter business model requires efficient utilization of all resources. In this context, virtualization and opportunistic batch scheduling have delivered significant increases in efficiency by effectively sharing CPU time across many applications, but it remains difficult to share memory resources. Therefore, each new workload directly increases memory pressure, but only marginally increases the load on other resources.

As an example of the foregoing, the popular website Twitter runs memcached, a key-value store, on a cluster of 500 machines with 30 TB of DRAM [57]. Today, vendors are selling in-memory database appliances with 4 TB of DRAM total, in which each server board hosts 512 GB [1]. The memory analysis results in this work, given in Chapter 2, indicate that "big-data" workloads also require servers with large memories – for example, Shark, an in-memory data mining engine [29], fully utilized 680 GB of DRAM on a cluster of 100 virtual machines hosted by Amazon Web Services. To quantify the cost of this memory, at the time of this writing, machines with 128 GB of DRAM are common [69]. At 128 GB of capacity, DRAM costs \$1400^2 or close to 50% of the entire machine cost. Further, DRAM is 20% to 30% of machine energy and because each memory module has a high fixed cost in power, this cost grows as a fraction of the total when the datacenter is underutilized [10]. Therefore, DRAM is a significant fraction – about 1/3 – of datacenter total cost of ownership (TCO).

Furthermore, the issue of memory capacity is likely to become more significant in the future: in addition to increased application demand for memory, the trend is toward slower DRAM scaling and higher DRAM pricing. Forecasts indicate that DRAM prices will go up by 40% and that the total market will expand by 28% in 2013 [3, 4]. Tighter supply reflects the increasing challenge of DRAM scaling. Current 1T-1C DRAMs require 25 fF of capacitance per bit, and it is difficult to use smaller capacitors because of data refresh overheads [53]. While scaling continues for other silicon designs, it is increasingly difficult to translate this into DRAM scaling because maintaining the minimum required cell capacitance requires higher aspect ratios which put cell reliability at risk [40, 54, 30]. Demand for higher peak bandwidth further exacerbates the capacity issue: to improve channel electrical characteristics

<sup>&</sup>lt;sup>1</sup> i.e. Hive (data warehouse software) on Spark (a distributed in-memory execution engine).

$<sup>^2</sup>$  16 DIMMs, ECC DDR3-1600, ABMX & New Egg accessed July 2013.

and hence improve bandwidth, the next generation DDR4 specification allows only one memory module per memory channel [60]. Because of chip pin-count limitations, the number of memory channels is unlikely to scale up significantly, therefore, at one-half the number of modules per channel, the cost of capacity for DDR4 is relatively higher than for DDR3: each module must provide twice the (normalized) capacity.

Given that the dominant memory technology, DRAM, is showing diminishing returns in terms of capacity, it makes sense to look for alternatives. Emerging nonvolatile memory technologies may enable a new level in the memory hierarchy referred to as "storage-class memory" or "SCM." An SCM solution would provide much more capacity than DRAM, with the additional benefit of retaining its data, even when powered down – this compares quite favorably to DRAM which needs millisecond scale refresh. Unfortunately, there is no viable SCM solution available today, and the most promising candidates for commercialization are still 5x to 10x slower than DRAM [9, 39]. Further, many of the non-volatile memory technologies face the challenge of limited write endurance and therefore require sophisticated wear leveling techniques, in effect, introducing a level of indirection. Even when SCM systems become available, it is unlikely that they will completely replace DRAM - rather, due to their relatively higher latencies, it is very likely that a large DRAM cache will be necessary to provide acceptable performance. Finally, given that deduplication can reduce the number of data writes into memory, the work in this thesis may be even more applicable to SCM, that is, to provide both increased capacity and increased write endurance.

This thesis answers to a critical need by addressing the issue of memory capacity. Emerging applications and the growing importance of datacenter computing are driving increased demand. Current price points make memory up to 50% of capital expenditure and 20% of operating expenditure, and worse, the memory continues to consume power, even when machines are idle. Empirically, DRAM scaling has already

slowed and will very likely continue to slow. Finally, no current technology is likely to completely replace DRAM. Together, these trends and observations indicate that memory capacity will become more, not less, of a concern in the future.

#### 1.2 Efficient Use of Memory

These trends, increased demand for memory capacity and slowing DRAM scaling, point to a need to make more efficient use of memory. Software techniques, both for compression and for deduplication, have been deployed to answer to this need, but these techniques find limited use due to significant costs and show little benefit relative to the opportunity. On the other hand, special purpose hardware can be used to the same end. Although such hardware requires a significant investment to design, verify, and deploy, these expenses appear warranted given that software solutions cannot fully exploit the opportunity without significantly harming user program performance.

As evidence of the need, three software techniques for increasing memory capacity have found wide-spread use. Virtual machine hosts use transparent page sharing to deduplicate memory at 4 KB page granularity [66]. Recently, the popular OS X operating system implemented page compression [5], and nearly every operating system provides virtual memory to user applications using demand paging. Although promising, these techniques all come with serious performance penalties.

In more detail, both compression and transparent page sharing steal CPU cycles from user applications. Therefore, when used, the operating system also throttles each of these techniques to a point where their performance impact is minimal. For example, in VMware ESX, transparent page sharing is limited to scan all of memory only once every ten minutes [32]. With such a slow scan rate, transparent sharing cannot deduplicate any pages that have been written to recently – a serious drawback that limits its potential upside. Moreover, to reduce page table lookup costs, virtual

machine hosts are compelled to use much larger page sizes which further limits the utility of transparent page sharing. Turing to page compression, OS X compresses only the least recently used pages and only under memory pressure, again, to minimize performance impact. Succinctly, page compression is a last resort to avoid paging to disk. And although demand paging provides the illusion of near infinite memory capacity, paging to disk is generally avoided if at all possible.<sup>3</sup>

Because software techniques incur high costs, the question of implementing special purpose hardware appears viable. In particular, a hardware solution would not steal any CPU time from the running applications. Although such hardware does not directly steal CPU cycles, it does potentially increase the memory access latency which incurs an indirect performance cost. Therefore, this thesis evaluates a direct hardware implementation of fine-grain memory deduplication, both in terms of its benefit and performance. The remaining paragraphs in this introduction provide a brief overview of each of the chapters – the reader may skip these entirely, or refer to them as a guide to what each chapter has to offer.

#### 1.3 Duplicates in Actual Workloads

While duplicates are known to be common for *virtualized* workloads, such as Amazon Elastic Compute Cloud (EC2), this thesis shows that they are also common in a broader class of *non-virtualized* datacenter workloads. Most computer architecture research questions are answered by running *benchmark* applications such as SPEC CPU, but these benchmarks do not contain representative data – rather, they use either random, constrained random, or null data. Therefore, to understand how common duplicate values are, this thesis turns to real workloads running in actual datacenters.

<sup>&</sup>lt;sup>3</sup> Of course, the need to avoid paging had motivated the otherwise expensive page compression.

Results from counting duplicate values in these large-scale application memories, including results from well known companies such as Yelp and LinkedIn, indicate that duplicates account for nearly 2/3 of all memory content. If this could be exploited with no overhead, then 2/3 of memory is made redundant, or capacity is increased by 3x. To eliminate duplicate values, but still provide the abstraction of memory, the relationship between original content and unique content must be memorized, but in a compressed form – this is known as the *translation*. Including the cost of translation, the savings are reduced to 2.21x: conservatively, a factor of 2x increased capacity, or 50% cost savings on memory. Looking at datacenter total cost of ownership, or TCO, this translates into 15% savings, or \$75 million over the lifetime of a datacenter.

#### 1.4 Deduplicated Memory: Performance and Power

Motivated by the high potential gains, this thesis investigates the cost of deduplicated memory in terms of application performance and memory system power. In the worst case, the time to read a memory location, or read latency, is doubled because a deduplicated memory read requires first a translation fetch, and then a data fetch. Furthermore, a deduplicated memory write requires first duplicate search and then translation update, thus making what was originally a single memory operation into several. Therefore, deduplicated memory can increase both read latency and memory bandwidth. Prima facie, higher read latency degrades program performance and increasing bandwidth requires more power.

This thesis proposes novel optimizations that reduce the performance impact of deduplicated memory. Using the optimizations, this work shows that, in general, performance remains largely unchanged. More specifically, translation fetch is removed from the critical path using a direct translation buffer: a cache similar to the well known translation lookaside buffer. The cost of the direct translation buffer is low,

relative to other caches, because the translation itself is a compressed representation of the original memory content. Further, the processor last level cache is extended to be duplicate aware, an optimization referred to as deduplicated cache or DDC. The DDC provides an effectively larger cache capacity, therefore reducing cache miss-rate, and therefore reducing memory bandwidth. To reduce memory accesses on write-back, the DDC also provides in-cache duplicate search. If a duplicate is not found by in-cache duplicate search, the DDC allocates an entry, and defers the costly global duplicate search until that entry is evicted and written back to main memory. A state-of-the art simulator is modified to model performance of systems with deduplicated memory. Simulation results indicate that a minority of applications suffer minimal performance degradation, and, on many applications, performance actually improves as a result of increased cache capacity.

In addition to providing increased capacity, deduplicated memory also saves power because the number of memory devices is reduced. With fewer memory devices, each individual device serves more requests and therefore power per device goes up. Although power per device increases, the savings on replacing two devices with one outweighs this increase. The deduplicated cache further improves power savings because it reduces the number of memory operations, in many cases to an amount lower than that required by the original non-deduplicated system.

#### 1.5 Deduplicated Sparse Matrices

Using hierarchical deduplication, as used by HICAMP, this thesis shows that inmemory representations of large scale physical problems – or *sparse matrices* – can be significantly reduced in size. In the deduplicated memory introduced in Section 1.4, no duplicate values remain from the original content, but its compressed representation, the translation, may have duplicate entries. A hierarchically deduplicated memory also deduplicates the translation, and that translation's translation, until the original content is described by the connections between a set of unique memory blocks. Because certain sparse matrices contain many replicated sub-matrices, hierarchical deduplication can provide compounded benefit: a factor in excess of 4096:1 compression is achieved by a hierarchy of 2:1 compressions. Using off-the-shelf hardware and software, this thesis shows that such memory savings improve performance in the context of scientific and industrial computing. HICAMP provides further speedup because it inherently recognizes the connections between unique memory blocks in hierarchical deduplication.

#### 1.6 HICAMP Architecture

This thesis was inspired by previous work on the HICAMP architecture [24], which had been introduced to provide architectural support for parallel programs. Technology trends have pushed parallel computing into the mainstream: once the domain of supercomputers, today, even cellular phones have highly parallel processors. When a program is structured such that many machines can simultaneously work on the same problem, conflicts over the actual state of memory can arise. This happens when two or more machines, unbeknownst to each other, simultaneously attempt to update the same memory location – a problem referred to as a memory race. Memory races are a challenging problem: programmers who are aware of the issue can still introduce subtle, but fatal, program bugs known as deadlocks. A deadlock occurs when the programmer stops one portion of the program to prevent a race, but inadvertently introduces a cyclic chain of such dependencies eventually blocking the progress of the entire program. The specter of deadlock causes many programmers to sacrifice parallel program efficiency for program correctness.

<sup>&</sup>lt;sup>4</sup> This is lossless compression, later referred to as "compaction."

HICAMP addresses these issues by providing a multi-version memory, made efficient by deduplication. In HICAMP, each concurrently executing portion of a program logically accesses and updates its own version of memory, including shared program state. As each concurrently executing task finishes, its updates are published, or committed, to the most up-to-date version of memory. Observing that most concurrent tasks do not produce true memory conflicts, HICAMP detects and resolves conflicting updates at the time of commit, thus allowing the most work to be accomplished in parallel.

1.7. SUMMARY 11

#### 1.7 Summary

As described above, and as noted in the literature, application trends are driving demand for memory capacity up relative to demand for compute performance. Further, the dominant memory technology is showing diminishing returns in terms of capacity. Therefore, this thesis addresses a critical problem, namely that of providing extra memory capacity.

Using techniques described by HICAMP, this thesis proposes fine-grain memory deduplication for current CPU architectures. By analyzing memory content in actual large-scale application memories, this thesis demonstrates that duplicates are common enough to be reliably exploited. It shows that the cost of duplicate suppression is very low, in terms of performance, and that memory system power is reduced.

Looking toward the future, continued performance gains must come from implementing parallel programs. As shown by the HICAMP Architecture, a multi-version main-memory is a natural fit for parallel programs. On the other hand, the cost of a multi-version memory is prohibitively high without duplicate suppression. Therefore, this thesis addresses the critical problem of providing extra memory capacity, and, by enabling multi-version memory, it also addresses the longer term problem of providing architectural support for parallel programs.

## Chapter 2

## Deduplicated Memory

The purpose of deduplicated memory is to provide extra capacity, but with the same physical resources – that is, to directly reduce the cost of memory capacity by never storing the same data twice. This chapter shows that deduplicated memory is feasible using current commodity memory devices and that it incurs only modest overhead. In specific, it shows that by reprogramming the CPU memory controller logic, deduplicated memory can be implemented using industry standard memory modules with no further changes. To prevent duplicate entries from being allocated, deduplicated memory must be able to check if some given data is already stored. Further, to maintain its function as a memory, deduplicated memory pays a cost, referred to as translation, to record the relationship between original memory content and the set of unique memory blocks that have been deduplicated. This chapter analyzes these costs. In specific, it shows that the proposed hash-based global content search is efficient and has few hash table overflows. Because of the cost of translation, deduplicated memory pays off only if enough duplicates exist. To motivate the remainder of the thesis, this chapter shows that duplicates are indeed common, that they occur with high reliability in many large-scale workloads, and that after accounting for the cost of translation, memory capacity can be doubled.

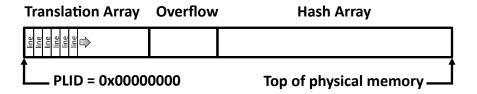

Figure 2.1: Deduplicated Memory Layout

#### 2.1 Deduplicated Memory Organization

A deduplicated memory, or DDM, presents the abstraction of a standard computer memory, but application memory content is made unique at some granularity. To preserve application memory, the relationship between original content and unique content must be memorized, but in a compressed form – this is referred to as the translation. The translation has one entry per nominal memory location and each such entry specifies a certain block of unique content. If, for example, an application stores the same sequence of values to memory several times, then multiple entries in the translation refer to the same block of unique content. Logically, entries in the translation must be smaller than the unique blocks of memory. To maintain compatibility with existing hardware and software, deduplicated memory exposes the same interface as standard computer memory. To write to deduplicated memory, first, a duplicate search is performed, and second, the translation is updated.

In a deduplicated memory, the CPU does not have direct access to physical memory. Rather, the physical memory is managed by the memory controller as an array of 64 byte memory lines. Shown in Figure 2.1, the lines are identified by physical line id, or PLID, and are divided into three regions: the translation array, the hash array, and the overflow. When there is no ambiguity, a line is referred to by its purpose: as in data line, a line that stores unique content in the hash array, or translation line,

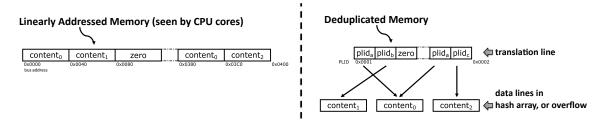

Figure 2.2: Address Translation and Content Deduplication

a line that stores several PLIDs and provides a mapping from processor bus address to deduplicated content.<sup>1</sup> As an optimization, a zero stored as a translation refers to a completely zero valued data line. Thus, the content referred to by the zero valued PLID never needs to be fetched from memory, and the PLID referring to zero valued content is known without the need for duplicate search.

To distinguish from locations in physical memory, this work refers to the nominal location of memory content, as seen by the CPU, as a bus address. Therefore, a bus address specifies a particular translation line, and also an entry in that translation line. That entry contains a PLID, which in turn specifies a particular data line. Figure 2.2 illustrates these ideas by showing the view of memory as seen by a CPU core and the actual memory content after deduplication. In the illustration, there are logically five lines stored in the system, but only three data lines and one translation are actually required.

#### 2.2 Processor Reads and Writes

A processor write causes the deduplicated memory to search for a pre-existing instance of the content being written. This operation, referred to as *content lookup*, returns a PLID that points to a data line. On lookup, if no pre-existing identical content can

<sup>&</sup>lt;sup>1</sup> A reference count line contains packed reference counts and is stored in the hash array, a signature line contains packed data line signatures and is stored in the hash array, an overflow line contains program data and is stored in the overflow region.

| Read Sequence            | Write Sequence                                         |

|--------------------------|--------------------------------------------------------|

| 1. Read translation line | 1. Hash Content                                        |

| 2. Extract PLID          | 2. Lookup content, using hash value from (1)           |

| 3. Read content          | 3. Read translation line                               |

|                          | 4. Extract PLID from translation line from (3)         |

|                          | 5. Update translation line from (3) with PLID from (2) |

|                          | 6. Write translation line from (5) back to memory      |

|                          | 7. Increment reference count of PLID from (2)          |

|                          | 8. Decrement reference count of PLID from (4)          |

Table 2.1: Read and Write Sequences

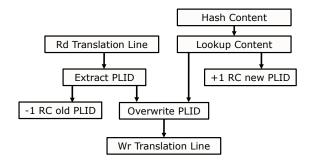

Figure 2.3: Write Sequence Dependencies

be found, a new data line is allocated. The write is recorded by storing the PLID in the translation array at an offset determined by the bus address. On read, the deduplicated memory returns a copy of either a data line or overflow line.

Table 2.1 shows the specific sequence of actions for a processor read or write. Without further optimization, deduplicated reads require two memory fetches, therefore potentially causing a CPU to stall while waiting on an additional memory read. On the other hand, the more complicated write sequence does not directly impact program performance because CPUs do not need to wait for writes to complete. Many steps in the write sequence can execute concurrently as illustrated in Figure 2.3. Logically, the write sequence requires only content lookup (Table 2.1 step 2), and translation update (Table 2.1 steps 3, 5, and 6): several other steps are listed for completeness; their purposes are explained in the following sections.

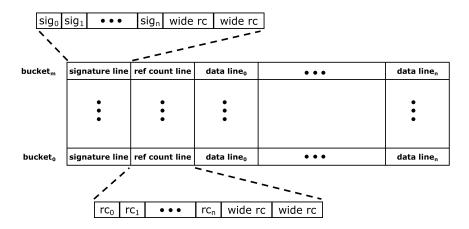

Figure 2.4: Hash Array Layout

#### 2.3 Content Lookup

A deduplicated memory must function both as a linearly addressable memory and as a content addressable memory, or CAM. Compared to a linearly addressable memory, which uses an array index to access content, a content addressable memory uses content as an index into the memory. Typical implementations of CAM in hardware, often used in internet routers and switches for IP lookup, provide very low latency at the expense of high power and low capacity. On the other hand, a deduplicated memory needs high capacity, but CAM functionality is only required on write – because write latency usually does not impact CPU performance, the deduplicated memory can trade latency for capacity when implementing CAM.

To distinguish from typical CAM hardware, deduplicated memory implements an operation referred to as *content lookup* which indexes memory using content and returns the PLID which points to the data line containing that content. If no pre-existing instance of the content is found, space is allocated, the content is written, and the PLID is returned.

#### Content Lookup

- 1. Read signature line from hash bucket

- 2. Compare signature of content against entries in signature line

- 3. If no signature match, but a zero entry exists in signature line:

- ... 3.1. Allocate: insert signature of content into signature line from (1)

- ... 3.2. Write signature line to memory

- ... 3.3. Write content to memory

- 4. If no signature match, and no zero entry in signature:

- ... 4.1. Allocate in overflow: read next free entry from overflow free list

- ... 4.2. Write content to memory at location given by (4.1)

- 5. If signature match(es) exist:

- ... 5.1. For each signature match, read and compare content

- ... 5.2. If a content match is found: Return PLID for content

- ... 5.3. If no content match is found: Allocate content, as in (3) or (4)

Table 2.2: In-Memory Content Lookup

To avoid the high cost of special purpose CAM hardware, deduplicated memory uses an efficient in-memory hash table described by Cheriton, et al., in their work on HICAMP [24]. Shown in Figure 2.4, it contains a number of hash buckets, m, each with a number of data lines, n. Each bucket also contains two additional memory lines of metadata: the reference count line and the signature line. The signature line is used to optimize content lookup. For each of the n data lines in its bucket, it contains either a signature (a small, non-zero, secondary hash value) or zero to indicate a free line. Because the content of every line in a given bucket is represented in a compressed form in each signature, reading the signature line effectively searches the entire hash bucket in a single DRAM operation. For content lookup, two common cases exist: either no signature match exists and a free line is immediately allocated based on a zero entry in the signature line, or exactly one signature match exists and a subsequent data line read and content comparison verifies that a duplicate has been found. If there is more than one signature match, multiple data line reads and content comparisons are required. Table 2.2 describes the complete content lookup sequence.

To provide efficient deallocation when content is no longer in use, the deduplicated memory keeps a reference count for each data line in the hash array. To minimize

| Symbol         | Meaning                                              |  |

|----------------|------------------------------------------------------|--|

| $\overline{m}$ | Number of hash buckets                               |  |

| n              | Bucket capacity (ways)                               |  |

| u              | u Number of unique memory lines                      |  |

| l              | Table load: $l = u / (m \cdot n)$                    |  |

| o              | Number of memory lines that spill to overflow        |  |

| $p_b$          | $p_b$ Probability of hashing to a given bucket       |  |

| k              | k Load of a given hash bucket                        |  |

| P(k)           | P(k) Probability that a given hash bucket has load k |  |

| N(k)           | Expected number of buckets with load k               |  |

Table 2.3: Hash Table Notation

reference count overhead, all reference counts for a given hash bucket are packed into a single memory line – the reference count line – which contains a narrow (1 byte) reference count for each data line in the bucket. If a given data line's reference count is greater than 250, a value between 251 and 254 indicates that its reference count is stored in one of the wide entries, also in the same reference count line. In the unlikely event that more wide reference count entries are needed than available,<sup>2</sup> the narrow reference count entry is assigned the value 255 to indicate "stuck at infinity," after which, it cannot be deallocated. The reference count lines are updated in accordance with the write sequence shown in Table 2.1.

#### 2.4 Hash Bucket Overflows

Even using an ideal hash function, as content is added to memory, some hash buckets fill up before others – therefore, the deduplicated memory includes an overflow provision. This section first analyzes overflow behavior in the hash table from Section 2.3 and then explains allocating memory content in the overflow provision.

To minimize overflows, deduplicated memory uses a highly associative hash table, that is, a hash table with many ways or entries in each bucket. An ideal hash function

<sup>&</sup>lt;sup>2</sup> Several highly referenced lines would need to map to the same bucket.

produces a uniform random distribution of hash values which, in turn, produces a binomial distribution in the hash buckets. Very strong hash functions with highly efficient hardware implementations already exist [14], therefore, deduplicated memory uses such a function. Using the notation shown in Table 2.3, the following analysis [18] provides hash table overflows as a function of table load and the number of ways per bucket. Assuming an ideal hash function, the following is by definition:

$$p_b = \frac{1}{m} \tag{2.1}$$

The probability of a bucket with a given load k, P(k), and the number of buckets with that load, N(k), follow from the binomial distribution:

$$P(k) = \binom{u}{k} p_b^k (1 - p_b)^{u-k}$$

(2.2)

$$N(k) = m \cdot P(k) \tag{2.3}$$

Using Equation 2.3, the total number of memory lines that spill to overflow can be calculated by summation:

$$o = m \cdot \sum_{k=n+1}^{\infty} (k-n) \cdot P(k)$$

(2.4)

When the hash table is under heavy load, the Poisson approximation can be used in place of the binomial distribution. Using the Poisson approximation, and normalizing the number of overflows, o, to the total number of entries in the table,  $m \cdot n$ , the percentage of lines that overflow is:

percent overflow =

$$\frac{1}{l \cdot n} \cdot \sum_{k=n+1}^{\infty} (k-n) \cdot \frac{(l \cdot n)^k}{k!} e^{-l \cdot n}$$

(2.5)

Figure 2.5: Minimal Overflows

Hash bucket overflows, therefore, occur with some probability based on hash table load, l, and bucket capacity (or ways), n.

Figure 2.5 plots the percentage overflow (Equation 2.5) both as a function of table load and as a function of bucket capacity. Two observations follow: the overflow percentage is a decreasing function of bucket capacity, and, with sufficiently high bucket capacity, there are few overflows, even at high table load.

For simplicity, and because few lines spill to overflow, overflow lines are not deduplicated. Using a well-known technique [64], a list of unused overflow lines, referred to as the *free list*, is kept in the unallocated overflow memory. If the content lookup operation (Table 2.2) cannot allocate in the hash bucket, it allocates an overflow line from the free list. Therefore, the number of memory operations for content lookup is bounded by the bucket capacity, n. Although O(n) operations are required in the worst case, the cost of content lookup seldom approaches this limit because the probability of multiple false signature matches is very low. Bucket overflow is normally detected without the need for content fetch and compare. Because the free list entries are packed, overflow allocation normally requires no additional memory accesses, and at most, requires one extra memory access to fetch the next free list entry.

# 2.5 Deduplication and Overhead

After deduplication, only unique memory lines remain. Ignoring the cost of translation, the maximum upside to deduplication is the ratio of total memory lines to unique memory lines, referred to as the *total-to-unique ratio* or *TTU*:

$$total-to-unique\ ratio = \frac{N_{lines-total}}{N_{lines-unique}}$$

(2.6)

A large total-to-unique ratio indicates that many duplicates exist. For example, with TTU = 100x, logically, only  $1/100^{th}$  of memory resources are required, or capacity is increased by 100x when using those resources provided.

The practical benefit, referred to as *compaction*, is limited by the overhead of storing the translation, and, to a lesser extent, limited by the overhead of reference count and signature metadata. Fundamentally, the ratio of memory line size to PLID size sets the maximum compaction. Smaller lines increase deduplication but also cost more in terms of translation overhead. Larger PLIDs allow more unique data lines to be stored, but also increase the overhead of translation. To demonstrate the benefits of deduplicated memory, this work uses the following parameters in its evaluation: a memory line size of 64 bytes, a PLID size of 4 bytes, and 56 ways per hash bucket.

In this implementation, the line-size to PLID-size ratio is 16 – therefore, the maximum compaction is effectively 16x, even if the TTU is 100x. With 56 ways per bucket, there is room for two wide (4 byte) reference count entries per hash bucket. As shown in Figure 2.5, with 56 ways, even under high table load, overflows remain low. Therefore, signature and reference count metadata incur approximately 2 extra bytes per unique data line. Revising the total-to-unique ratio to include all

overhead – translation, reference counts, and signatures – the deduplication benefit, hereafter referred to as *compaction*, is given by the following:

$$compaction = \frac{N_{lines-total}}{1/16 \cdot N_{lines-total} + 66/64 \cdot N_{lines-unique}}$$

(2.7)

The memory line size, 64 bytes, is chosen to match the cache line size used on many current CPU architectures. The PLID size, 4 bytes, is chosen to be evenly divisible into the memory line size, but also to be narrow and therefore limit the translation overhead. One limitation of using narrow 4 byte PLIDs is that only  $2^{32}$  memory lines or 256 GB of DRAM can be addressed. This limit can be overcome by using wider PLIDs, which increases the overhead of translation, or by using multiple deduplication domains. For example, a two-socket server board may implement a separate deduplicated memory for each socket. In this two-socket system, 512 GB of DRAM can be addressed, but up to two instances of a given line of content may exist at any given time. Although not investigated in this work, this strategy of using multiple deduplication domains is expected to provide nearly the same compaction: as shown in the next section, deduplication is effective for different memory sizes from 7 GB to 1024 GB and a large amount of the benefit comes from data lines with high reference counts.

# 2.6 Duplicates In Real Workloads

Given that the translation is a direct overhead to deduplicated memory, a key question is how common are duplicate memory lines, and how much compaction is achieved after including that cost. It is well known that many coarse grain duplicates exist in virtual machine hypervisors [66], therefore, fine-grain duplicates also exist in

| Company     | Workload     | Dataset                | Memory            | TTU   | Compaction |

|-------------|--------------|------------------------|-------------------|-------|------------|

| Facebook    | Tao          | Social Graph           | 144 GB            | 1.07x | 0.98x      |

| Lightminer  | Benchmark    | TPCH                   | $256~\mathrm{GB}$ | 1.76x | 1.54x      |

| SAP         | SAP HANA-One | Private                | 1024 GB           | 1.94x | 1.68x      |

| Quantifind  | Data Mining  | Social web data        | 64 GB             | 2.87x | 2.37x      |

| LinkedIn    | Profile Page | Professional Profiles  | 48 GB             | 3.09x | 2.52x      |

| Arista      | Build Server | Private                | 128 GB            | 3.10x | 2.53x      |

| UC Berkeley | Shark        | Conviva Server Logs    | 68 GB             | 3.18x | 2.58x      |

| NHN         | Memcached    | Private                | 48 GB             | 3.36x | 2.71x      |

| Yelp        | Hadoop (EMR) | Private                | 7 GB              | 4.21x | 3.25x      |

| Ayasdi      | Data Mining  | Patient Health Records | 96 GB             | 5.30x | 3.89x      |

| Geomean     | -            | -                      | -                 | 2.68x | 2.21x      |

Table 2.4: Duplicates in Real Workloads

these systems. On the other hand, there is no published work describing how many duplicate values exist in non-virtualized application memories. Furthermore, this question cannot be addressed using standard benchmark programs, such as SPEC CPU: such benchmarks typically use random, constrained random, or completely null data. To answer this question, this thesis provides data from actual large-scale deployed workloads.

A two step process is used to count duplicates. To avoid corrupting memory content, an image of physical memory is recorded to disk using the minimally invasive Linux Memory Extractor, or LiME [63]. After LiME, zest, a separate program, is used to count the number of unique memory lines. For these results, at least three images were recorded, and the reported values are for the largest number of unique lines found in each set. Little variation was observed in any given set of three, an observation consistent with prior results reported for memory compression (as opposed to deduplication) methods [28, 55].

Table 2.4 shows the results from zest, both as a total-to-unique ratio and as effective compaction. All of the workloads shown in Table 2.4 are non-virtualized. The results show that duplicate values are common in actual large-scale applications, and that in many cases, enough duplicates exist to provide an effective factor of 2x in

Figure 2.6: Cumulative Reference Count Histogram

memory capacity improvement. In aggregate, there are almost three times as many stored values as unique values.

Figure 2.6 shows that a significant amount of the savings comes from lines with a high reference count. In more detail, it shows the percentage of the original memory which had a reference count less than or equal to its corresponding coordinate on the abscissa.<sup>3</sup> About 22% of the original memory content was completely unique and therefore had a reference count of exactly one. On the other hand, 40% of the original memory had a reference count of 100 or more. The slope, measured at a given reference count, indicates the amount of memory that would have been consumed, i.e. without deduplication, by memory lines with that reference count.

Although much of the savings come from high reference count lines, the most common reference count is one, as indicated by its outsize contribution to the total:

<sup>&</sup>lt;sup>3</sup> Data in Figure 2.6 is from Quantifind.

namely 22% versus just a few percent, or less, for all reference counts greater than one. Despite this, the accumulated effect of deduplication pushes the total-to-unique ratio almost to three and the resulting compaction is 2.37x.

As expected, not all workloads create many duplicate entries in memory. For example, the application Tao, running at Facebook, has a total-to-unique ratio of only 1.07x which is not enough to cover the overhead of translation: for Tao, compaction is 0.98x. Other workloads, not sampled in this study, may also have a very low total-to-unique ratio. For such workloads, deduplication does not pay off and only incurs the cost of extra memory operations for content lookup and capacity overhead for translation.

On the other hand, all results in Table 2.4, except Tao, have a high, or very high, total-to-unique ratio. Since Table 2.4 includes all data from all respondents, this suggests that duplicate values are common even in workloads not yet sampled. Based on this data, by geometric mean, average compaction is 2.21x. Thus the results indicate that duplicates are indeed common in deployed large-scale applications. And, for many applications, deduplicated memory reliably provides 2x compaction.

## 2.7 Operating System Support

Although deduplicated memory, as described to this point, is transparent to the operating system, some modification to operating system memory management is prudent. As shown in Section 2.6, many applications have a very high steady-state total-to-unique ratio – on average, 2.68x – but, if a new application is started, or if application behavior changes, this total-to-unique ratio may drop. If the operating system is unaware of the current degree of compaction, there is a risk that a write to the DDM will fail: this happens if the write maps to a full hash bucket and there are no free overflow lines. Such a write failure can, in turn, cause an unrecoverable

CPU error – an unacceptable situation. To prevent such unrecoverable errors, the operating system memory manager needs to know both the apparent size of memory and the actual utilization of memory resources.