# BALANCING EFFICIENCY AND FLEXIBILITY IN SPECIALIZED COMPUTING

# A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

Rehan Hameed December 2013

## Abstract

CMOS-based integrated circuits have hit a power wall, and future performance increases cannot rely on increased power budgets. This means we need to create more energy efficient solutions if we want performance to continue to scale.

A proven way to gain high efficiency is to build special-purpose ASIC chips for the application of interest. These designs can achieve 2-3 orders of magnitude higher energy efficiency and performance compared to general-purpose processors. However ASIC design has become prohibitively expensive making it difficult to justify the investments in design effort for all but the few applications with very large volumes and stable code bases. General-purpose processors amortize the design cost over a large number of applications, and provide standard development tools, resulting in higher productivity and lower development costs. However, this flexibility comes at a cost of much higher energy consumption.

This thesis examines the tradeoff between flexibility and efficiency with an aim to develop architectures that combine the low energy consumption of customized units with the reusability of general purpose processors. A number of approaches are already being tried to lower the energy consumption of programmable systems, such as a move to homogenous and heterogenous multi-core systems, augmenting the processors with hardware accelerators, and creating application-specific processors. However our work takes a step back to first understand and quantify what makes a general purpose processor so inefficient and whether it is at all possible to get close to ASIC efficiencies within a programmable framework. The insights from this work are then used as a basis to derive new architectural ideas for efficient execution.

Specifically, we propose building domain customized functional units as a solution

for balancing efficiency with flexibility. As a case study, we look at the domain of imaging and video processing. These workloads are becoming ubiquitous across all computing devices and have very high computing requirements often served by special purpose hardware. At the same time there are a large number of emerging applications in this domain with diverse requirements, so going forward there is a great need for flexible platforms for this domain. Thus it is an ideal candidate for our study. We demonstrate two programmable functional units for this domain - the Convolution Engine and the Bilateral Engine. A number of key computational motifs common to most applications in this domain can be implemented very efficiently using these engines. The resulting performance and efficiency is within 2-3x of custom designs but an order of magnitude better than general-purpose processors with data-parallel extensions such as SIMD units.

We also argue that domain customized functional units demand a slight change in the mindset of system designers and application developers – instead of always wanting to fit the hardware to algorithm requirements, we optimize a number of key computational motifs and then restructure our applications to make maximum use of these motifs. As an example, we look at modifying the *bilateral filtering* algorithm – a key non-linear filter common to most computational photography applications – such that it is a good fit for the capabilities of our proposed hardware units. The resulting implementation provides over 50x energy reduction over the state of the art software implementation for this algorithm.

Our work suggests that identifying key data flows and computational motifs in a domain and creating efficient-yet-flexible domain customized functional units to optimize these motifs is a viable solution to address the energy consumption problem faced by designers today.

# Acknowledgements

I would like to thank the little green men from Mars.

# Contents

| $\mathbf{A}$ | Abstract |                                               |    |

|--------------|----------|-----------------------------------------------|----|

| $\mathbf{A}$ | ckno     | wledgements                                   | vi |

| 1            | Inti     | roduction                                     | 1  |

|              | 1.1      | Motivation                                    | 1  |

|              | 1.2      | Thesis Overview                               | 3  |

| <b>2</b>     | Ene      | ergy Constraints And The Need For Flexibility | 6  |

|              | 2.1      | Technology Scaling and Energy Constraints     | 7  |

|              | 2.2      | Energy Efficiency and Processor Systems       | 11 |

|              |          | 2.2.1 Multi-Core Systems                      | 12 |

|              |          | 2.2.2 Heterogenous Multi-Core Systems         | 14 |

|              | 2.3      | Imaging and Video Systems                     | 15 |

| 3            | Ove      | erheads In General Purpose Processors         | 18 |

|              | 3.1      | Anatomy of a Typical RISC Instruction         | 19 |

|              | 3.2      | Removing Processor Overheads                  | 22 |

|              | 3.3      | Our Methodology                               | 25 |

| 4            | Rer      | noving Processor Overheads - H.264 Case Study | 27 |

|              | 4.1      | H.264 Computational Motifs                    | 28 |

|              | 4.2      | Analysis Methodology                          | 29 |

|              | 4.3      | Broad Specializations                         | 33 |

|   |      | 4.3.1 Building a Wider SIMD                        |

|---|------|----------------------------------------------------|

|   | 4.4  | Application Specific Customizations                |

|   |      | 4.4.1 IME Strategy                                 |

|   |      | 4.4.2 FME Strategy                                 |

|   |      | 4.4.3 CABAC Strategy                               |

|   | 4.5  | Area Cost of Magic Instructions                    |

|   | 4.6  | Magic Instructions Summary                         |

|   | 4.7  | Beyond H.264                                       |

| 5 | Cor  | avolution Engine 49                                |

|   | 5.1  | Convolution Abstraction                            |

|   | 5.2  | Target Applications                                |

|   |      | 5.2.1 Motion Estimation                            |

|   |      | 5.2.2 SIFT                                         |

|   |      | 5.2.3 Mapping to Convolution Abstraction           |

|   | 5.3  | Convolution on Current Data-Parallel Architectures |

|   | 5.4  | Convolution Engine                                 |

|   |      | 5.4.1 Load/Store Unit and Register Files           |

|   |      | 5.4.2 MAP & Reduce Logic                           |

|   |      | 5.4.3 SIMD & Custom Functional Units 6             |

|   |      | 5.4.4 A 2-D Filter Example                         |

|   |      | 5.4.5 Resource Sizing                              |

|   |      | 5.4.6 Convolution Engine CMP                       |

|   |      | 5.4.7 Programming the Convolution Engine 6         |

|   |      | 5.4.8 Controlling Flexibility in CE                |

|   | 5.5  | Evaluation Methodology                             |

|   | 5.6  | Results                                            |

|   | 5.7  | Convolution Engine Conclusion                      |

| 6 | Bila | ateral Filtering 83                                |

|   | 6.1  | Bilateral Filtering                                |

|   |      | 6.1.1 Gaussian Blur                                |

| $\mathbf{B}^{\mathbf{i}}$ | ibliog | graphy  |                                              | 105 |

|---------------------------|--------|---------|----------------------------------------------|-----|

| 7                         | Cor    | nclusio | ns                                           | 102 |

|                           | 6.6    | Concl   | usion                                        | 100 |

|                           |        | 6.5.2   | Results                                      | 98  |

|                           |        | 6.5.1   | Simulation Methodology                       | 97  |

|                           | 6.5    | Accele  | eration Results                              | 97  |

|                           |        | 6.4.1   | Path Divergence                              | 97  |

|                           | 6.4    | Hardy   | vare Acceleration of Modified Bilateral Grid | 95  |

|                           | 6.3    | Extra   | cting Locality - Modified Bilateral Grid     | 90  |

|                           |        | 6.2.2   | Permutohedral Lattice                        | 89  |

|                           |        | 6.2.1   | Bilateral Grid                               | 86  |

|                           | 6.2    | Bilate  | ral Filtering - Existing Implementations     | 85  |

|                           |        | 6.1.2   | Bilateral Blur                               | 84  |

# List of Tables

| 2.1 | Scaling Results for Circuit Performance. Reproduced from [23]                                                                           | 9  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Intel's optimized H.264 encoder vs. a 720p HD ASIC. The second row scales Intel's SD data to HD. Original 180nm ASIC data was scaled to |    |

|     | 90nm                                                                                                                                    | 19 |

| 3.2 | Energy cost of accessing a 32-bit word from various levels of memory hi-                                                                |    |

|     | erarchy and register file (45nm technology node). Third column shows                                                                    |    |

|     | the ratio of these energy costs to the cost of a 32-bit ADD operation.                                                                  | 22 |

| 4.1 | SIMD resource sizes used for each processor. CABAC does not benefit                                                                     |    |

|     | from SIMD, so no SIMD unit is added to the EC processor                                                                                 | 33 |

|     | ,                                                                                                                                       |    |

| 5.1 | Comparison of various hardware solutions in terms of the flexibility                                                                    |    |

|     | they offer in various components. Last column summarizes the energy                                                                     |    |

|     | efficiency achieved by each design point relative to the base RISC, for                                                                 |    |

|     | H.264 study in previous chapter. Designs are listed in the order of                                                                     |    |

|     | increasing efficiency                                                                                                                   | 50 |

| 5.2 | Mapping kernels to convolution abstraction. Some kernels such as sub-                                                                   |    |

|     | traction operate on single pixels and thus have no stencil size defined.                                                                |    |

|     | We call these matrix operations. There is no reduce step for these                                                                      |    |

|     | operations                                                                                                                              | 54 |

| 5.3 | Sizes for various resources in CE                                                                                                       | 63 |

| 5.4 | Energy for filtering instructions implemented as processor extensions    |    |

|-----|--------------------------------------------------------------------------|----|

|     | with 32, 64 or 128 ALUs. Overhead is the energy for instruction fetch,   |    |

|     | decode and sequencing                                                    | 65 |

| 5.5 | Major instructions added to processor ISA                                | 67 |

| 6.1 | Execution time and storage requirements of grayscale vs RGB bilateral    |    |

|     | filtering schemes for an HD video frame. Decimation factor is 16 in all  |    |

|     | dimensions. Entries refers to the array or hashtable entries required    |    |

|     | to store the points in high dimensional space. Bytes refers to the size  |    |

|     | of storage structure in bytes. Direct algorithm is direct application of |    |

|     | Equation 6.3                                                             | 87 |

| 6.2 | Quality comparison of various schemes for RGB bilateral filtering of a   |    |

|     | high definition video frame. The metric for output quality is the PSNR   |    |

|     | relative to an exact solution of equation 6.4                            | 91 |

# List of Figures

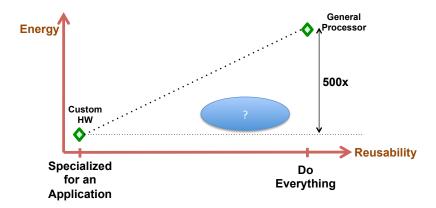

| Design Space for Programmability vs Energy Efficiency Tradeoff. We     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| would like a new design point lying somewhere in the blue region,      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| with energy consumption close to custom hardware, and having high      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| flexibility.                                                           | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

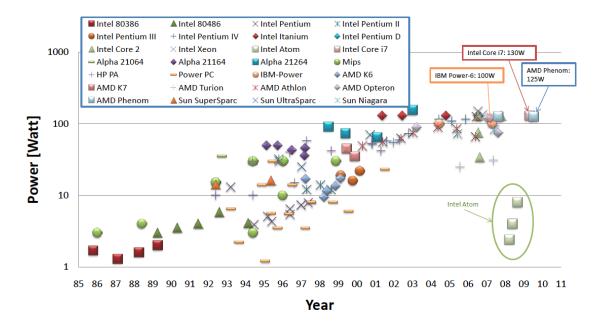

| Microprocessor power consumption over the years [52]                   | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

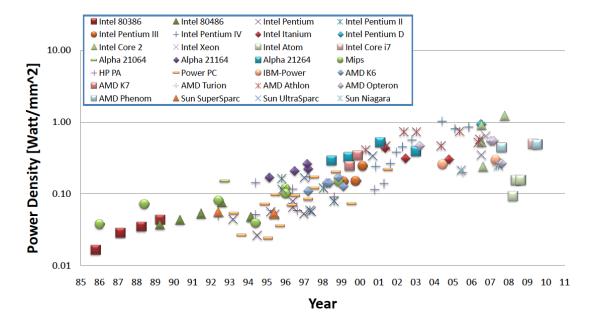

| Microprocessor power densities over the years [52]                     | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

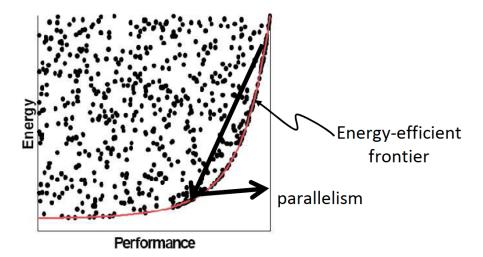

| The energy-performance space. The Pareto-optimal frontier line rep-    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| resents efficient designs—no higher performance design exists for the  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| given energy budget. The recent push for parallelism advocates more,   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| but simpler, cores. This backs off the higher performance high-power   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| points and uses parallelism to keep/increase performance [52]          | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Two widely used mobile SOC platforms                                   | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Simplified image capture pipeline which converts RAW data from sen-    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| sor into RGB images or video frames. (TODO: update with a better       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| pipeline)                                                              | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

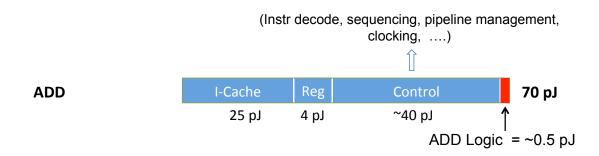

| Energy breakdown of a typical 32-bit RISC instruction in 45nm tech-    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| nology. Assumes a 32-KByte I-Cache.                                    | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

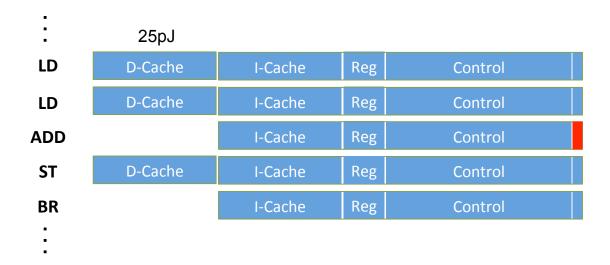

| Further overheads on top of a RISC instruction. Executing the ADD      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| instruction requires further support instructions such as loads and    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| stores, branches, address calculations and so on. The loads and stores |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| involve costly D-Cache accesses.                                       | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                        | would like a new design point lying somewhere in the blue region, with energy consumption close to custom hardware, and having high flexibility.  Microprocessor power consumption over the years [52].  Microprocessor power densities over the years [52].  The energy-performance space. The Pareto-optimal frontier line represents efficient designs—no higher performance design exists for the given energy budget. The recent push for parallelism advocates more, but simpler, cores. This backs off the higher performance high-power points and uses parallelism to keep/increase performance [52].  Two widely used mobile SOC platforms.  Simplified image capture pipeline which converts RAW data from sensor into RGB images or video frames. (TODO: update with a better pipeline)  Energy breakdown of a typical 32-bit RISC instruction in 45nm technology. Assumes a 32-KByte I-Cache.  Further overheads on top of a RISC instruction. Executing the ADD instruction requires further support instructions such as loads and stores, branches, address calculations and so on. The loads and stores |

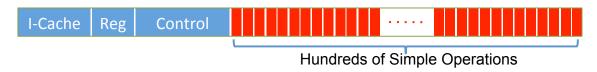

| 3.3 | Amortize the cost of instruction fetch and control overheads over a                                                                 |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------|----|

|     | large number of simple operations                                                                                                   | 21 |

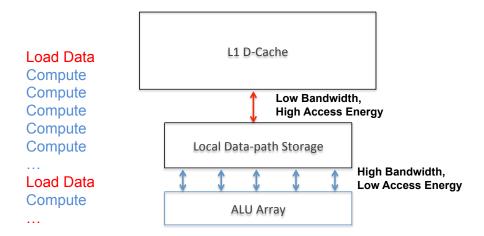

| 3.4 | Amortize each memory access over a large number of instructions                                                                     | 23 |

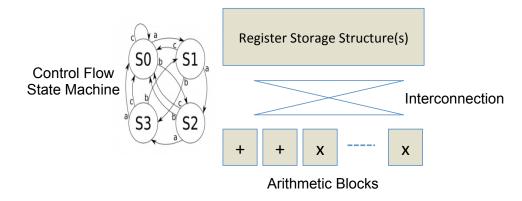

| 3.5 | Four distinct components of a computing machine                                                                                     | 24 |

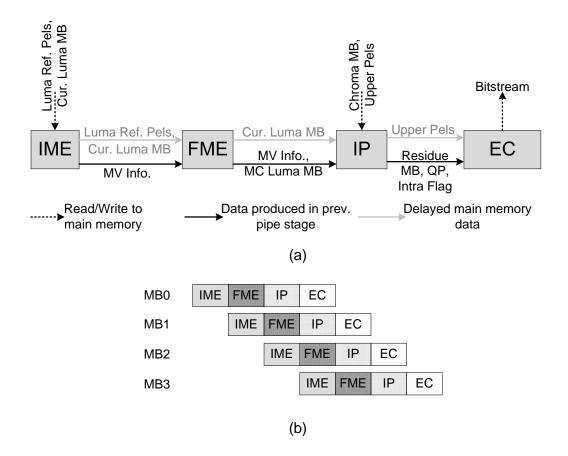

| 4.1 | Four-stage macroblock partition of H.264. (a) Data flow between stages. (b) How the pipeline works on different macroblocks. IP in- |    |

|     | cludes DCT + Quant. EC is CABAC.                                                                                                    | 30 |

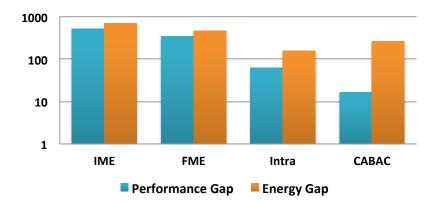

| 4.2 | The performance and energy gap for base CMP implementation when                                                                     |    |

|     | compared to an equivalent ASIC. Intra combines IP, DCT, and Quant.                                                                  | 31 |

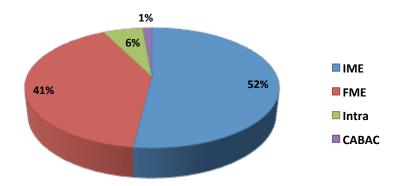

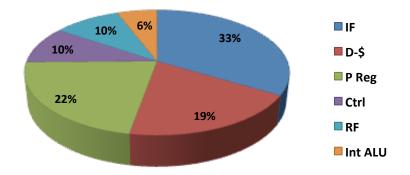

| 4.3 | Processor energy breakdown for a 32-bit RISC implementation of the                                                                  |    |

|     | high definition H.264 encoder. The graph shows distribution across                                                                  |    |

|     | H.264 sub-algorithms. Note: Intra combines IP, DCT, and Quant                                                                       | 32 |

| 4.4 | Processor energy breakdown for base implementation. IF is instruction                                                               |    |

|     | fetch/decode. D-\$ is data cache. P Reg includes the pipeline registers,                                                            |    |

|     | buses, and clocking. Ctrl is miscellaneous control. RF is register file.                                                            |    |

|     | FU is the functional units                                                                                                          | 32 |

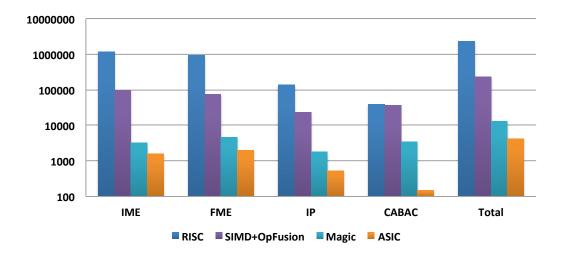

| 4.5 | Each set of bar graphs represents energy consumption (mJ) at each                                                                   |    |

|     | stage of optimization for IME, FME, IP and CABAC respectively.                                                                      |    |

|     | The first bar in each set represents base RISC energy; followed by                                                                  |    |

|     | RISC augmented with SIMD+OpFusion; and then RISC augmented                                                                          |    |

|     | with magic instructions. The last bar in each group indicates energy                                                                |    |

|     | consumption by the ASIC.                                                                                                            | 35 |

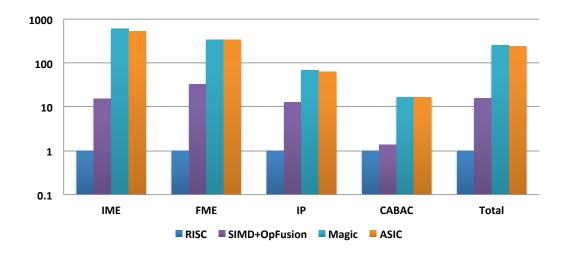

| 4.6 | Speedup at each stage of optimization for IME, FME, IP and CABAC.                                                                   | 35 |

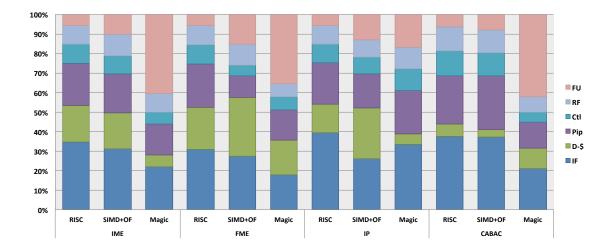

| 4.7 | Processor energy breakdown for H.264. SIMD+OF is SIMD with op-                                                                      |    |

|     | eration fusion. IF is instruction fetch/decode. D-\$ is data cache. Pip                                                             |    |

|     | is the pipeline registers, buses, and clocking. Ctl is random control.                                                              |    |

|     | RF is the register file. FU is the functional elements. Only the top                                                                |    |

|     | bar or two (FU, RF) contribute useful work in the processor. For this                                                               |    |

|     | application it is hard to achieve much more than 10% of the power in                                                                |    |

|     | the FU without adding custom hardware units                                                                                         | 36 |

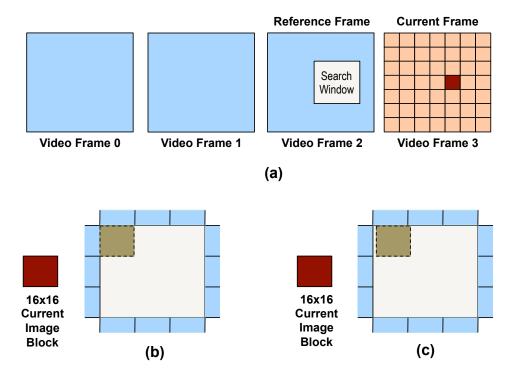

| 4.8  | (a) IME operates on a stream of video frames. Here we are encoding         |    |

|------|----------------------------------------------------------------------------|----|

|      | frame 3 using a previous frame in the stream as reference (frame 2).       |    |

|      | The red square is a $16x16$ image $macroblock$ , and the goal is to find   |    |

|      | its closest match within a 48x48 search window in the reference frame.     |    |

|      | (b) A blowup of the search windows, showing the first 16x16 search         |    |

|      | location in the search window which is compared against the current        |    |

|      | macroblock (c) The second search block is shifted from the first search    |    |

|      | block by just one pixel - most of the pixels from previous comparison      |    |

|      | are re-used                                                                | 37 |

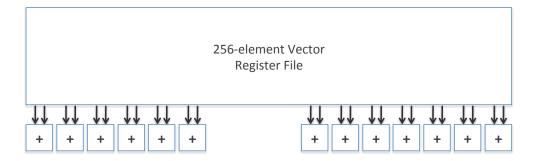

| 4.9  | A very wide hypothetical SIMD unit with 256-element compute array          |    |

|      | and a register file with 256-element wide vector registers                 | 39 |

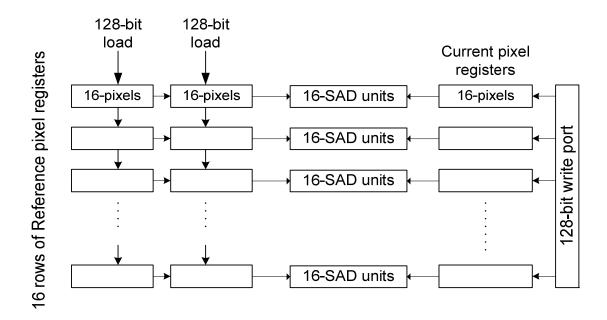

| 4.10 | Custom storage and compute for IME 4 X 4 SAD. current and ref-pixel        |    |

|      | register files feed all pixels to the 16 X 16 SAD array in parallel. Also, |    |

|      | the ref-pixel register file allows horizontal and vertical shifts. $$      | 42 |

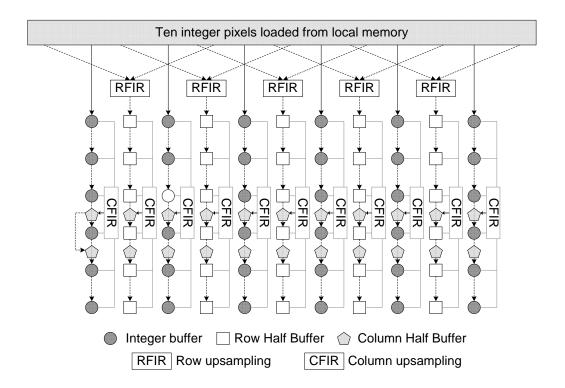

| 4.11 | FME upsampling unit. Customized shift registers, directly wired to         |    |

|      | function logic, result in efficient upsampling. Ten integer pixels from    |    |

|      | local memory are used for row upsampling in RFIR blocks. Half up-          |    |

|      | sampled pixels along with appropriate integer pixels are loaded into       |    |

|      | shift registers. CFIR accesses six shift registers in each column simul-   |    |

|      | taneously to perform column upsampling                                     | 43 |

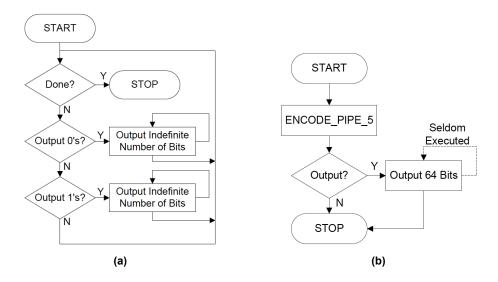

| 4.12 | CABAC arithmetic encoding loop. (a) H.264 reference code. (b) Af-          |    |

|      | ter insertion of magic instructions. Much of the control logic in the      |    |

|      | main loop has been reduced to one constant time instruction EN-            |    |

|      | CODE_PIPE_5                                                                | 44 |

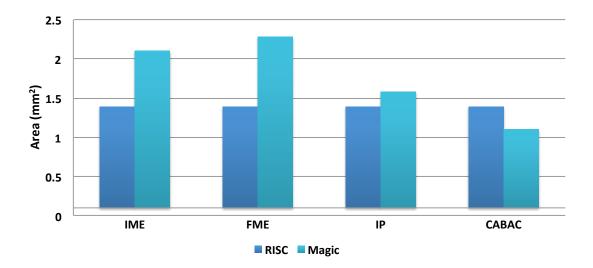

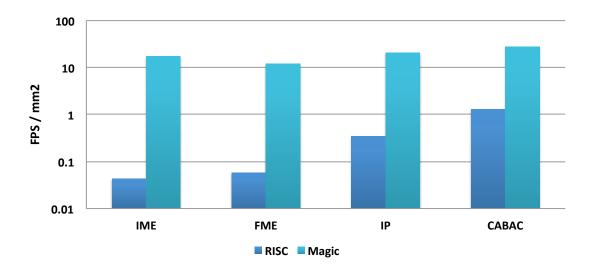

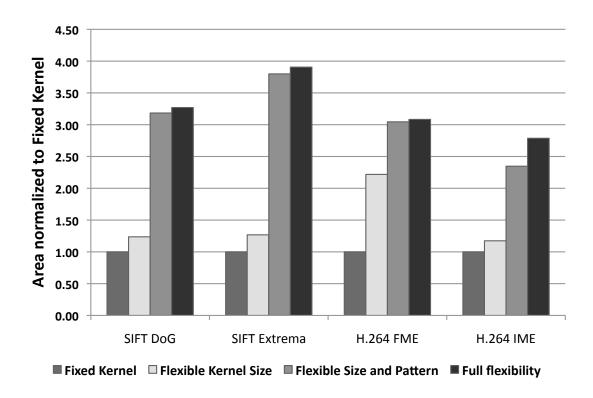

| 4.13 | Area in $mm^2$ for magic instruction designs compared to the area of base  |    |

|      | processor (90nm technology). These numbers include both processor          |    |

|      | core area, as well as I-Cache and D-Cache area                             | 45 |

| 4 14 | Area efficiency of magic vs RISC cores                                     | 46 |

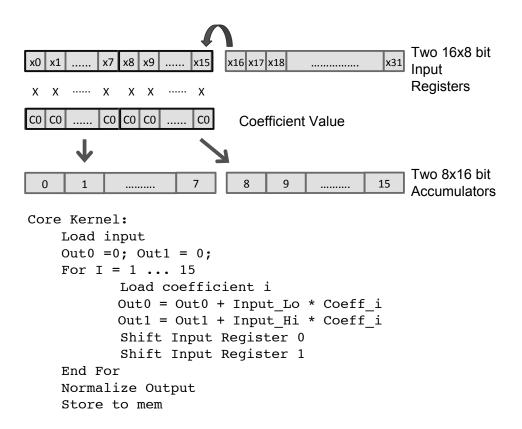

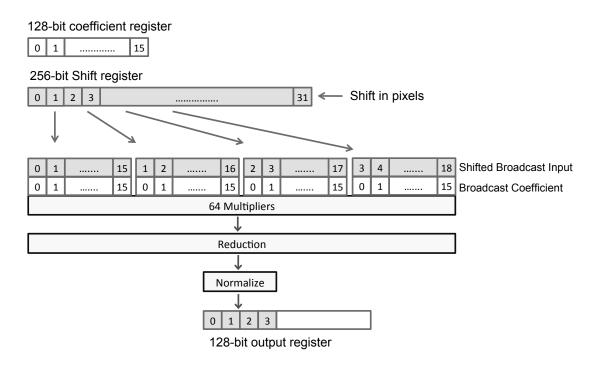

| 5.1  | We use the n-tap 1D convolution presented here to explain our SIMD              |    |

|------|---------------------------------------------------------------------------------|----|

|      | implementation. For SIMD the equation is parallelized across outputs            |    |

|      | and executed one column at a time.                                              | 55 |

| 5.2  | 1D Horizontal 16-tap convolution on a 128-bit SIMD machine, similar             |    |

|      | to optimized implementation described in [56]. 16 outputs are com-              |    |

|      | puted in parallel to maximize SIMD usage. Output is stored in two               |    |

|      | vector registers and two multiply-accumulate instruction are required           |    |

|      | at each step.                                                                   | 56 |

| 5.3  | 1D Horizontal 16-tap convolution using a shift register with shifted            |    |

|      | broadcast capability. Computes 4 output pixels per instruction                  | 57 |

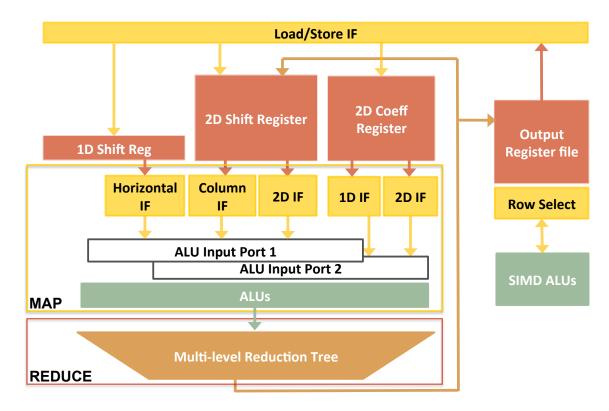

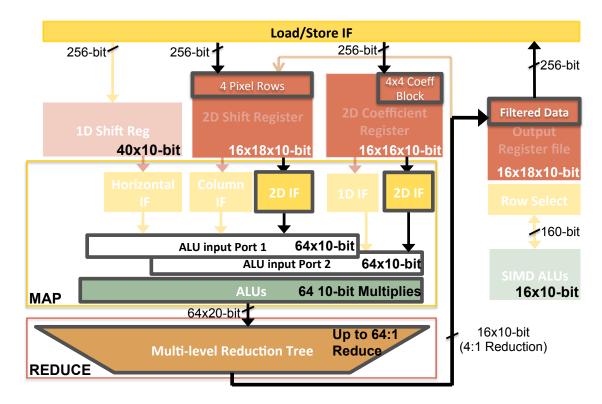

| 5.4  | Block Diagram of Convolution Engine. The interface units (IF) connect           |    |

|      | the register files to the functional units and provide shifted broadcast        |    |

|      | to facilitate convolution                                                       | 59 |

| 5.5  | Executing a 4x4 2D Filter on CE. The grayed out boxes represent units           |    |

|      | not used in the example. The sizes of all of the resources are defined.         |    |

|      | The of choice these particular resource sizes will be explained in a later      |    |

|      | section.                                                                        | 62 |

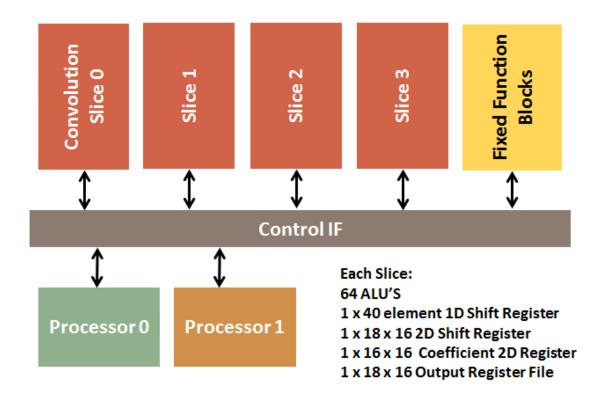

| 5.6  | Convolution Engine CMP                                                          | 66 |

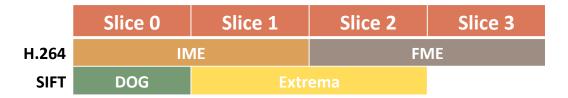

| 5.7  | Mapping of applications to Convolution Engine CMP                               | 71 |

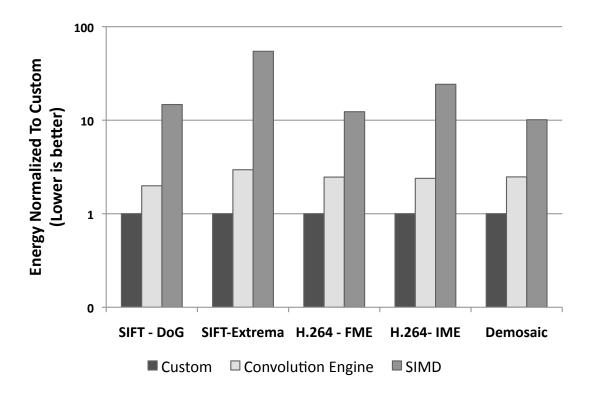

| 5.8  | Energy consumption normalized to custom implementation: Convolu-                |    |

|      | tion Engine vs custom cores and SIMD                                            | 73 |

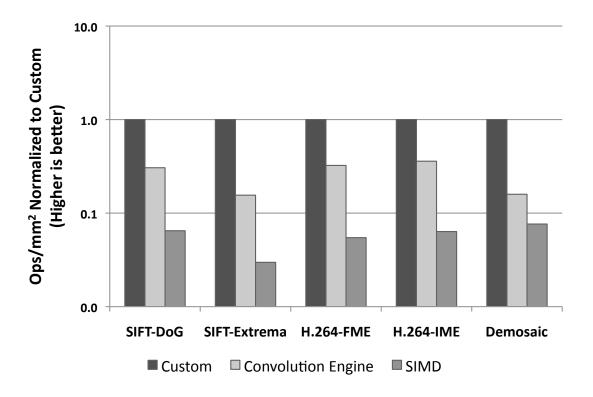

| 5.9  | Ops/mm2 normalized to custom implementation: Number of image                    |    |

|      | blocks each core processes in one second, divided by the area of the            |    |

|      | core. For H.264 an image block is a $16 \text{x} 16$ macroblock and for SIFT it |    |

|      | is a 64x64 image block                                                          | 74 |

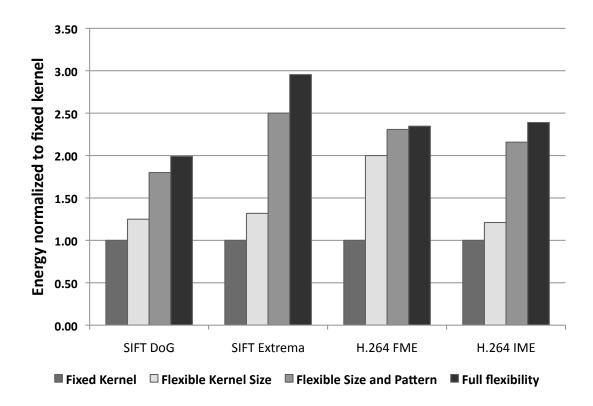

| 5.10 | Change in energy consumption as programmability is incrementally                |    |

|      | added to the core                                                               | 76 |

| 5.11 | Change in area as programmability is incrementally added to the core.           | 77 |

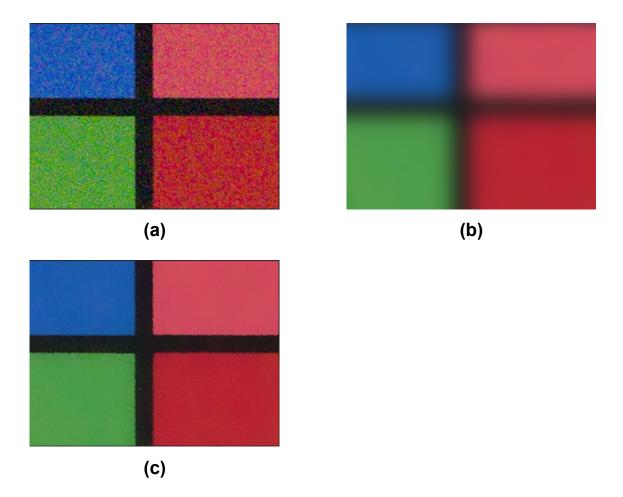

| 6.1  | Smoothing using a standard gaussian blur kernel vs a bilateral filter.          |    |

|      | (a) Original image (b) Gaussian blur (c) Bilateral filter                       | 82 |

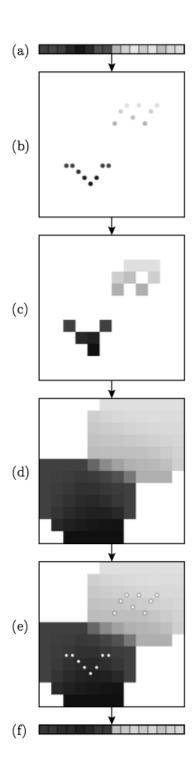

| 6.2 | The splat, blur and slice steps used in bilateral grid algorithm - repro-    |    |

|-----|------------------------------------------------------------------------------|----|

|     | duced from [9]. (a) Input "image" is a 1D grayscale signal. (b) Each         |    |

|     | pixel in the image is treated as a point in the 2D (x, I) space with a       |    |

|     | 2D position vector. (c) Each pixel is assigned to the coarse grid square     |    |

|     | it falls in. The size of the square depends on the decimation factor.        |    |

|     | (d) The entire 2D space is blurred using a 2D blur kernel. The lighter       |    |

|     | pixels group is at a distance from the darker pixel group so no signif-      |    |

|     | icant mixing of the two occurs. (e) For slicing the blurred 2D space         |    |

|     | is sampled at positions corresponding to the original image pixels. (f)      |    |

|     | Output pixels are now blurred without crossing the edges                     | 88 |

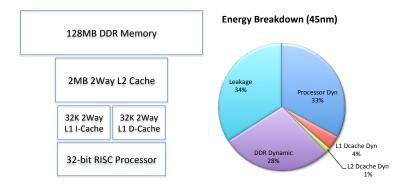

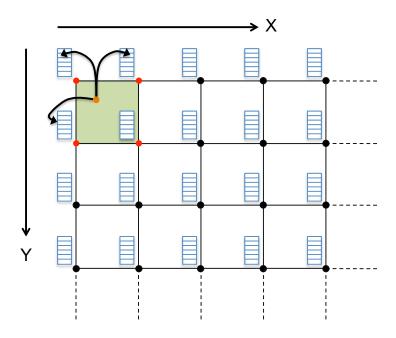

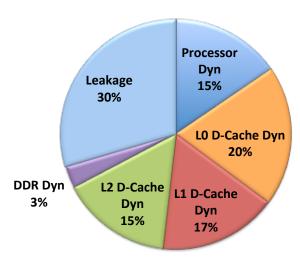

| 6.3 | Permutohedral Lattice based implementation of bilateral filtering on a       |    |

|     | Tensilica based 32-bit RISC platform. The system includes $32\mathrm{KB}$ L1 |    |

|     | instruction and data caches, as well as a 2MB L2 cache. DDR accesses         |    |

|     | account for more than $40\%$ of dynamic energy dissipation. Leakage          |    |

|     | energy is also very significant and mostly comprises the leakage from        |    |

|     | the large L2 cache                                                           | 90 |

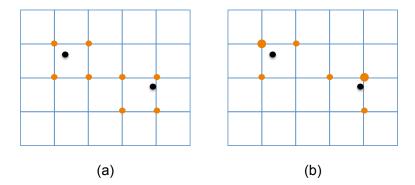

| 6.4 | (a) In regular bilateral grid algorithm each pixel imparts its energy to     |    |

|     | all the $2^d$ vertices of the d-dimensional hyper-cube that it falls in. In  |    |

|     | this 2D illustration, each pixel updates all 4 vertices of its enclosing     |    |

|     | square. (b) In the modified grid scheme, each pixel updates its closest      |    |

|     | grid vertex as well as the d neighbors - one along each dimension            | 91 |

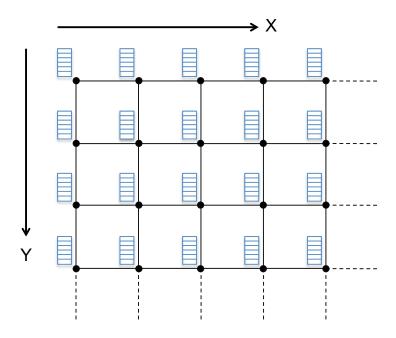

| 6.5 | Modified Bilateral Grid uses an XY-Grid of hash tables to represent          |    |

|     | the decimated space (5D for RGB case). The X-Y grid represents the           |    |

|     | points along X, Y axes of the 5D space, and the hash table at each grid      |    |

|     | location stores the sparsely populated RGB sub-space corresponding           |    |

|     | to that X Y co-ordinate                                                      | 92 |

| 6.6  | X, Y co-ordinates of the grid correspond directly to the X, Y pixels     |     |

|------|--------------------------------------------------------------------------|-----|

|      | locations in the image. Assuming a decimation factor of 32 in X, Y,      |     |

|      | the green highlighted square in X, Y grid corresponds to the first 32x32 |     |

|      | block in the image. The highlighted pixel in that 32x32 block updates    |     |

|      | the hash-table on its nearest XY vertex, as well as the neighboring      |     |

|      | hash-tables along X and Y                                                | 94  |

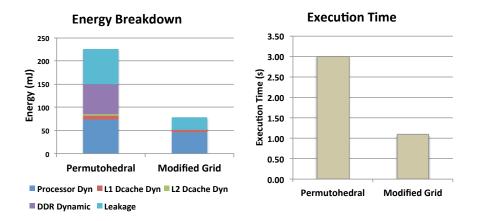

| 6.7  | Energy consumption and execution time for permutohedral lattice based    |     |

|      | algorithm vs our modified bilateral grid. The test image is an HD video  |     |

|      | frame. The decimation factor is 32 in spatial dimensions and 16 in RGB   |     |

|      | dimensions                                                               | 94  |

| 6.8  | Proposed data-path for modified bilateral filtering. It consists of an   |     |

|      | array of 4-way SIMD units, which are all operated by the same in-        |     |

|      | struction stream. While not explicitly shown, each SIMD unit has its     |     |

|      | own address generation unit as well as a dedicated port to access the    |     |

|      | L0-cache                                                                 | 96  |

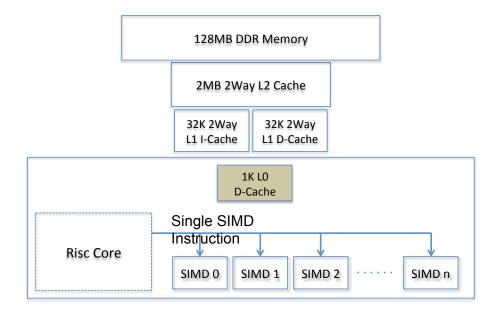

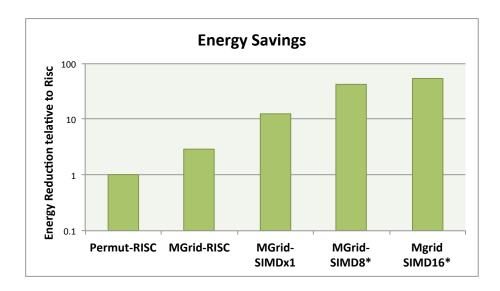

| 6.9  | Energy consumption for various implementations of RGB bilateral fil-     |     |

|      | tering for a HD video frame. Permut refers to Permutohedral Lattice      |     |

|      | implementation, MGrid refers to Modified Grid algorithm. For Modi-       |     |

|      | fied Grid we present results for RISC implementation as well as SIMD     |     |

|      | implementations with one, 8 and 16 SIMD units. Results are normal-       |     |

|      | ized with respect to Permutohedral Lattice RISC implementation. The      |     |

|      | results marked with '*' use a combination of simulation and manual       |     |

|      | estimation                                                               | 99  |

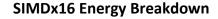

| 6.10 | Energy consumption breakdown for 16-SIMD-Unit implementation of          |     |

|      | Modified Grid bilateral filtering.                                       | 100 |

## Chapter 1

## Introduction

#### 1.1 Motivation

A major challenge faced by computer architects today is to create new architectures which achieve higher performance at fixed power. Most computing systems today are power limited. In case of servers and desktops, power is constrained by our inability to cool these devices effectively once power crosses a threshold. Mobile and embedded devices not only have even lower cooling limits, but also aim to maximize battery life by minimizing power consumption. While these have very different power envelops—a few hundred watts for servers vs. a few watts for mobile platforms—both operate under strict power limits. Since power is operations/sec x energy/operation, we need to decrease the energy cost of each operation if we want to continue to scale performance at constant power.

With such an emphasis on low energy designs it might be a shock to know that current general purpose processors are extremely inefficient when it comes to energy consumption. Studies such as [30] and [21] have shown that a general purpose processor often consumes up to 1000 times higher energy compared to dedicated hardware solutions for compute intensive applications! In past this steep cost of programmability was hidden by the energy reduction achieved through voltage scaling in successive generations of semiconductor fabrication technology. However with voltage-scaling coming to a stop, and at the same time power budgets hitting a ceiling, we can no

Figure 1.1: Design Space for Programmability vs Energy Efficiency Tradeoff. We would like a new design point lying somewhere in the blue region, with energy consumption close to custom hardware, and having high flexibility.

longer continue to waste this much energy. This suggests we should move away from general purpose processors and create custom ASICs which make much more efficient use of energy and silicon area. Indeed, this has been the approach for many high-volume applications. However with today's billion transistor chips, designing and manufacturing an ASIC has become extremely expensive, and very few applications have a big enough market to justify the cost.

Processors have a big advantage that you design a processor once and then re-use it again and again over a larger number of applications, effectively amortizing the design cost as well as the manufacturing cost. Moreover processors provide a well-established development environment, as well as a much greater ability to react to changes in application requirements.

This thesis explores the large design space between ASICs and GP processors. As depicted in Figure 1.1, we want to look for new tradeoff points in this space which have energy consumption close to custom hardware and, yet, do not give up too much in flexibility compared to a fully programmable processor. Ideally such design points would fit somewhere in the blue region of Figure 1.1.

#### 1.2 Thesis Overview

Chapter 2 discusses in detail the energy constraints faced by designs today as well as the challenges faced by future hardware systems designed under these constraints. Specially, we concentrate on image processing applications, which are rapidly becoming an integral part of most computing systems and at the same time have very high computation requirements.

We approach the goal of creating flexible, yet efficient designs by first understanding what are the sources of energy overheads in a general purpose processor, and quantifying the contribution of each of these to the overall inefficiency of the processors. Chapter 3 explores this topic by presenting energy breakdown of a typical RISC instruction and also relates that to the energy cost of cache and DRAM memory accesses. For most of the instructions, cost of an ALU operation is less than 1% of instruction energy - much of the energy cost goes into (i) fetching and decoding the instruction stream to implement a programmable control flow, and (ii) moving data from a memory / cache to the ALU inputs. Conceptually, the primary mechanisms for reducing these overheads include (i) amortizing the instruction sequencing cost by executing tens to hundreds of ALU operations per instruction, and (ii) minimizing cache / memory accesses by capturing most of the data-reuse in low-energy, high bandwidth storage structures local to the processor data-path. To gain high efficiency, then, we would like to incorporate these characteristics into a general purpose computation framework.

Of course not every application class can achieve 3 orders of magnitude energy reduction. Highest gains are achieved for applications which have a high degree of parallelism as well as significant data locality. While these conditions might seem restrictive, these span most of the applications for which efficient custom solutions exist.

One architectural idea which already employs similar principles is a SIMD unit which is now common in most modern processors including embedded processors [56, 1]. By restricting the domain of computation to 1-D data-parallel operations, a SIMD unit loses some flexibility but gains performance and energy efficiency. However, are

these types of broad specialization strategies good enough to overcome the energy overheads and get close to the efficiency of an algorithm specific custom hardware? And, if not, then how much further specialization is needed to bring the processor close to dedicated hardware designs?

Chapter 4 attempts to answer these question with a case study on HD H.264 video encoding - a highly compute intensive application often implemented as a custom ASIC. We transform a generic multi-processor RISC system into to a highly specialized multiprocessor optimized for this application. Initially we incorporate only broad specializations and optimizations, including SIMD, VLIW, and fused operations. While the resulting processor system achieves around 10x energy reduction for data-parallel components of the application, it still leaves a lot on the table consuming about 50x more energy overall compared to the ASIC. Further specialization brings the customized processors within 2-3x of the ASIC solution. However, the specialized data-paths that we add to achieve that, look fairly similar to their ASIC counter parts. Unlike the ASIC, the programmable control flow breaks the ties from a specific algorithm flow. However, in practice the highly algorithm-tuned nature of the data-path implies that these customized processors are not very useful beyond the algorithm they are designed for.

Chapter 5 shows that truly re-usable specialized cores can be created by specializing for recurring data-flow patterns instead of specializing for a specific application. The key is identifying patterns which are not only re-used across a range of applications, but also meet both the parallelism and data-reuse requirements that we have outlined. One such common motif in our target imaging domain is a convolution-like data flow: apply a function to a stencil of the data, then perform a reduction, then shift the stencil to include a small amount of new data, and repeat. Chapter 5 looks at building a flexible Convolution Engine for this motif. We show that the resulting unit is able to accelerate a diverse set of applications which are typically implemented today using a combination of multiple custom hardware units and programmable application processors and GPUs. Impressively it can do that with about two orders of magnitude less energy compared to a general processor, and in fact the energy consumption is within 2-3x of custom hardware. It is even an order of magnitude

better than a SIMD unit which is already specialized for data parallel algorithms.

Of course not everything in the imaging domain maps to this convolution abstraction. One such example is bilateral filtering [58], which is a non-linear filtering technique widely used in computational photography algorithms [9]. Bilateral filtering has a large working set and thus does not immediately offer the short term data re-use exploited in the convolution abstraction. However, as Chapter 6 shows the algorithm still has a large degree of locality. By restructuring the algorithm to expose that locality, we bring it to a form which we know how to optimize using similar techniques as used for the convolution based algorithms. The work on optimizing bilateral filtering also reinforces our belief that a domain customized approach requires a slight change in the mindset about how we approach hardware design. Instead of tailoring the hardware to the requirements of each individual algorithm we would like to identify widely applicable computational motifs which we can implement efficiently in hardware and then restructure the algorithms if needed to make use of these highly optimized computational motifs.

The convolution engine together with the bilateral engine provides the core capabilities required to accelerate a large number of imaging applications. This includes a multitude of emerging computational photography applications which aim to enhance the imaging experience and quality through use of advanced image processing techniques, but which are currently limited by the power or performance limitation of current imaging platforms.

## Chapter 2

# Energy Constraints And The Need For Flexibility

For years digital integrated circuit chips have been on a growth path which is nothing short of extraordinary. In just 30 years, we have gone from simple chips with only a few thousand transistors to today's extremely complex designs with billions of transistors - a million-fold increase. This growth has been made possible by semiconductor technology scaling - with every new generation we could not only fit exponentially higher number of transistors in a given chip area, but could also switch these transistors at exponentially lower energy to keep power in check. Designers leveraged these ever-increasing number of lower-energy transistors, and at the same time used higher and higher amounts of power, delivering bigger and faster designs with explosive growth in performance.

However, power consumption of these chips has hit the maximum limit in recent years, and at the same time energy reduction through technology scaling has slowed down. Thus, the traditional approach to getting more performance - using a larger number of transistors and running them at faster speed - no longer works as that would exceed the power limit. Energy consumption has thus become a primary design constraint today, and we need innovations in computer architecture creating designs which could do more work with the same number of transistor switches. In other words, these new designs have to make more efficient use of the transistor resources.

Another consequence of this exponential growth is a huge increase in design cost of the chips - a billion transistor chip is much more complex than a thousand transistor chip. In fact, the cost of designing a new dedicated hardware is now prohibitive for most applications [49, 29]. This is leading chip designers to use more and more programmable and reusable components such as processors. This, however, goes against the need to create energy efficient designs - as we and others [21] show, a general purpose processor can consume a hundred to a thousand times more energy compared to a dedicated hardware design. This puts us in a dilemma - given the energy constraints, we would like to move away from these inefficient processors and create efficient custom designs. However, the design complexity and reuse considerations push towards using programmable processor systems.

In this chapter, we discuss the implications of these constraints for future system design. Section 2.1 explains in detail how technology has evolved over the years and why scaling is no longer the answer. Section 2.2 then explains some approaches currently in use to solve this issue, including a move to multi-core systems as well as heterogenous systems, and limitations of these approaches. Specifically in 2.3 we look more closely at heterogeneous systems currently in use by most embedded imaging systems and explain why these designs are not well-equipped to meet the future needs of such systems within the given power constrains.

## 2.1 Technology Scaling and Energy Constraints

Technology scaling over the past few decades has been fueled by our ability to make the transistors smaller and smaller through advances in photolithography process, and pack a larger and larger number of these transistors on a single chip. Apart from increasing the transistor count, these smaller transistors also require less energy to switch them. Shacham et al. have presented a detailed account [52] of how semi-conductor technology has scaled over the years, as well as the corresponding trends in processor performance and power over that period. In this section, we summarize some of these trends to help understand the current landscape for hardware system design.

As Shacham et al. point out, understanding semiconductor technology scaling trends is best done by considering Moore's Law [41] and Dennard scaling [23]. Moore's Law, presented by Gordon Moore in 1965, predicted that the number of transistors on a chip will grow exponentially, roughly doubling every two years. Semiconductor chips have closely followed that trend, resulting, as stated previously, in a million-fold increase in transistor count over the last 30 years.

Dennard's work [23] on the other hand established scaling principles which would allow not only increasing transistor densities but at the same time gain higher transistor switching speeds at constant power dissipation. Under Dennard scaling, when we shrink transistor dimensions by k, the operating voltage is scaled by the same factor k to maintain a constant electric field. Table 2.1 reproduced from [23] lists the impact this has on various aspects of device performance. As the table suggests, following this scaling scheme, not only does the number of transistor in a given area increase by  $k^2$ , the delay decreases by k, which in turn means the design could run at k-times higher frequency. At the same time, despite the increased switching frequency, the switching power per transistor goes down by  $1/k^2$ . If we then account for the fact that we have now  $k^2$  time more transistors in the same area, the total power to switch all the transistors in that area remains constant. The implication is that we now have  $k^2$  more transistors switching at k-times higher frequency, without requiring any increase in silicon area or power. Thus technology scaling alone could enable increasingly higher performance chips without increasing the power budget, as long as designers could find ways to convert these extra transistors into higher performance.

However, as Shacham et al. further point out, in practice the semiconductor chips have deviated from the scaling path prescribed by Dennard, targeting even higher performance than would be achievable through Dennard scaling. Designers have pushed for higher frequencies through deeper pipelines, faster circuit configurations, etc. and have also increased chip areas to get even more transistors. The result is that instead of power density as well as power remaining constant, both of these have been increasing rapidly. One illustration of that can be seen in Figures 2.1 and 2.2 reproduced from [52] which present historical power and power density data for

| Device or Circuit Parameter      | Scaling Factor |

|----------------------------------|----------------|

| Device dimension $t_{ox}$ , L, W | 1/k            |

| Doping Concentration $N_a$       | k              |

| Voltage V                        | 1/k            |

| Current I                        | 1/k            |

| Capacitance $\epsilon A/t$       | 1/k            |

| Delay time/circuit VC/I          | 1/k            |

| Power dissipation/circuit VI     | $1/k^2$        |

| Power density VI/A               | 1              |

Table 2.1: Scaling Results for Circuit Performance. Reproduced from [23].

microprocessor designs. While this did not present a problem initially, gradually the chips started becoming too hot to cool economically. At the same time, more and more of the computing started moving to mobile platforms which are constrained by limited battery life and even lower power envelopes. These factors explain why power in Figure 2.1 tapered off soon after year 2000.

While hitting this power wall placed limitations on the techniques designers could employ, Dennard scaling was still available at hand to continue to scale performance within a fixed power budget. However in recent years even Dennard scaling has stopped. With leakage current becoming significant and accounting for a major component of chip power, it is no longer possible to scale down the threshold voltage,  $V_{th}$ . Consequently, we can no longer decrease the operating voltage,  $V_{dd}$ , without adverse impact on performance. Thus voltage scaling has pretty much stopped starting with the 90nm technology node. In the absence of voltage scaling, if we switch, as before,  $k^2$  times higher number of transistors at k-times higher frequency, there will be a sharp increase in power, which is not feasible. In fact, even without increasing the frequency, switching  $k^2$  times higher number of transistors at constant frequency would still increase the power. Thus we need to perform a larger number of computations per second to get higher performance, but can't proportionally increase the total number of transistors switched per second and consequently the energy dissipated per second. That in turn implies that each individual operation has to be performed using a lower number of transistor switches, using lower energy. This requires a move to

Figure 2.1: Microprocessor power consumption over the years [52].

Figure 2.2: Microprocessor power densities over the years [52].

fundamentally more efficient ways to perform computations.

### 2.2 Energy Efficiency and Processor Systems

As the last section elaborated, increasing performance of a system without an increase in power now requires performing each computation at a lower energy. One way to achieve that goal is to move away from programmable processors towards custom hardware design. Given their programmable nature, general purpose processors have higher overheads and as a result incur a large degree of wasted work to accomplish a given task. As seen with the H.264 ASIC example in the previous chapter, a hardware block specialized for a single algorithm can perform that task using much less resources and consequently much lower energy. Thus an obvious way to handle the energy constraints is to build custom hardware instead of programmable.

However, the NRE cost of designing and verifying an ASIC is increasing exponentially due to increased complexity and there are very few applications which have a broad enough market to justify this cost of designing dedicated hardware [49, 29]. A processor on the other hand can be designed once and then used for a large number of applications thus amortizing the cost over many systems.

Moreover, the software cost of designing drivers and firmware for each new chip is also increasing exponentially and in fact becoming the dominant cost now. Processors, on the other hand, have a well established software infrastructure and familiar development tools thus substantially reducing the software cost. Another advantage of a processor based design is the ability to adapt to changes in algorithms and requirements. With a custom hardware any changes late in the design cycle are costly both in terms of re-design effort as well as time to market. Processors can accommodate such changes at any point during or after the release. A huge testament to the advantages of programmable platforms can be found in the overwhelming popularity and rapid adoption of smartphones. What were once largely fixed function devices with a limited use case, now offer a very diverse set of functionalities as evidenced by millions of third-party applications in place for iOS and android-based smartphones.

There are thus compelling reasons to use processors as basic building blocks for

digital systems, and many applications which were once based on completely custom ASICs are now making more and more use of flexible processors. This desire to leverage flexibility of a processor-based designs, however, competes against the need for specialization to improve energy efficiency. Moreover, in order to extract higher and higher performance out of these processors, designers have employed more and more aggressive techniques such as out of order execution, branch target buffers, larger caches, deep pipelining, speculative execution and so on. These aggressive higher-performing processors not only take huge area, but as Azizi et al. [11] show, they are also even more inefficient in terms of energy consumption, thus further exacerbating the situation.

There is thus a growing interest in building more energy efficient programmable systems. This has also driven a move towards parallel multi-core systems based on simpler processor cores.

#### 2.2.1 Multi-Core Systems

As the last section alluded, pushing processor performance to higher levels requires aggressive energy-hungry techniques. To illustrate that better, Figure 2.3 reproduced from [52] shows the tradeoff space for energy vs performance in processor design. The red-line marks the efficient frontier consisting of designs which achieve the lowest energy consumption for a given performance level. As the figure shows, performance can be scaled to modest levels without a huge increase in energy consumption. However once we push the performance beyond a certain point, large incremental increases in energy consumption are incurred for relatively small gains in performance. Traditionally the processors were being built with a goal to maximize single core performance and the designs were pushed to limit extracting every last bit of performance using aggressive techniques. Resulting designs, while fast, made highly inefficient use of energy.

The emergence of the power wall, however, has forced designers to rethink this strategy. Instead of pushing the performance of a single core to the steepest region of the energy vs. performance curve, designers have moved towards systems with

Figure 2.3: The energy-performance space. The Pareto-optimal frontier line represents efficient designs—no higher performance design exists for the given energy budget. The recent push for parallelism advocates more, but simpler, cores. This backs off the higher performance high-power points and uses parallelism to keep/increase performance [52].