### APPLICATION OPTIMIZED COMPUTING

A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

> Wajahat Qadeer December 2013

© 2013 by Wajahat Qadeer. All Rights Reserved. Re-distributed by Stanford University under license with the author.

This work is licensed under a Creative Commons Attribution-Noncommercial 3.0 United States License. http://creativecommons.org/licenses/by-nc/3.0/us/

This dissertation is online at: http://purl.stanford.edu/xz888kk6027

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

### Mark Horowitz, Primary Adviser

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

### **Christoforos Kozyrakis**

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

#### **Stephen Richardson**

Approved for the Stanford University Committee on Graduate Studies.

#### Patricia J. Gumport, Vice Provost for Graduate Education

This signature page was generated electronically upon submission of this dissertation in electronic format. An original signed hard copy of the signature page is on file in University Archives.

## Abstract

All computing systems are power limited, whether it is the 1W limit of a cell phone, or the 100W limit of a server. Triggered by the end of voltage scaling, the restricted power budgets are the result of energy per transistor switch scaling slower than the number of transistors on the chip. Since technology scaling no longer provides the energy savings it once did, to scale performance (operations/sec), we must improve the energy per operation by reducing the number of transistors involved in each operation. This fundamental change is forcing the design community to find new approaches to energy efficient computing.

Most designs use pre-designed processor based solutions because of their flexibility and availability. However, they are usually not the most energy efficient solutions. The need for better energy efficiency has pushed these systems to become multicore. By reducing the peak performance of a processing core, the energy required per instruction can be reduced, either because the processor can be operated at a lower voltage, or because simpler core architectures can be used. Unfortunately, the efficiency gains provided by parallelism are finite and further gains will be difficult.

To better understand the potential of producing general-purpose chips with better efficiency, this thesis tries to analyze in detail the types of inefficiencies that exist in general-purpose systems — designs that can be outclassed by up to 3 orders of magnitude in both performance and energy-efficiency by ASIC designs. To collect this data, we classify applications using the dominant sources of energy: compute, control and memory. For compute and control bound applications we gather this data by first identifying the types and magnitudes of energy overheads that exist in a generalpurpose Tensilica based extensible RISC chip multiprocessor (CMP) system and then by exploring the architectural support and customizations needed to transform a general-purpose system to have the same energy efficiency as an ASIC.

Because the fundamental operations in compute bound applications are generally very low-power, amortization of overheads introduced by programmability requires execution of hundreds of these operations in one cycle. Interestingly, a high percentage of compute bound applications share common data-flow characteristics, which we exploit to create a flexible yet efficient domain specific processor, called the Convolution Engine. Although, control bound applications also operate on low-power control flow operations, sequential dependencies restrict the number of control flow operations fuseable into one instruction to between ten and fifteen. This restriction also defines the extent of achievable efficiency for control bound applications.

Unlike the low-power operations abundant in compute and control bound applications, the fundamental cost of a memory fetch is considerable. Improving the system efficiency of memory bound applications not only requires improving the efficiency of the processing elements, but also requires substantially increasing reuse in data fetches.

# Acknowledgement

I owe where I am today, in large part, to the help and encouragement of some of the marvelous people I have come to know at Stanford. First and foremost, I would like to thank Professor Mark Horowitz for his guidance, patience and encouragement. Not only is Mark a great advisor, more importantly, he is an amazing person and I cannot thank him enough for his support throughout my doctoral work.

I would like to extend my gratitude to my co-advisor Professor Christos Kozyrakis for teaching some of the most wonderful processor design courses, for sharing his vast knowledge with me and for always providing great feedback on my research. I would also like to thank Doctor Stephen Richardson for not only serving on my defense and reading committees, but also for being one of the most helpful and amazing people I know. I am also grateful to Professor Sanjay Lall for being the chair of my defense committee and Professor Subhashish Mitra for serving on my defense committee.

It's impossible to mention everyone that has helped me over the years, but I would like to extend a special thanks to my friend and colleague Rehan Hameed for his help and support throughout my stay at Stanford. Many thanks to Alex Solo-matnikov, Amin Firoozshahian, Ofer Shacham, Omid Azizi, Megan Wachs, Andrew Danowitz, John Brunhaver and other members of the VLSI group for their support, guidance and assistance. I would also like to acknowledge the administrative staff, especially Teresa Lynn and Mary Jane Swenson, for their assistance with numerous miscellaneous issues.

My stay at Stanford would have been incomplete without my amazing friends at and near Stanford. I would like to thank them for always trying to keep me on track, for the long squash sessions and for the amazing photography trips. Finally, I would like to add that I am eternally grateful to my parents, S. A. Qadeer and Rizwana Qadeer. If it had not been for their sacrifices, support and love, I would never have dreamed of being here. My greatest thanks to my wife, Tehmina, and my daughter, Zahra, for their love, support and encouragement and for always standing by me even in the most difficult of situations.

# Contents

| Ał       | ostra      | act                                                                             |

|----------|------------|---------------------------------------------------------------------------------|

| Ac       | ckno       | wledgement                                                                      |

| 1        | Intr       | roduction                                                                       |

| <b>2</b> | Bac        | ckground                                                                        |

|          | 2.1        | Embedded Low-Power Multiprocessor (ELM)                                         |

|          | 2.2        | SIMD Architectures and Vector Machines                                          |

|          | 2.3        | Extensible Processors                                                           |

|          | 2.4        | Application Classes                                                             |

|          |            |                                                                                 |

|          | Βοι        | und Applications                                                                |

|          | 3.1        | Н.264                                                                           |

|          |            | 3.1.1 Motion Estimation                                                         |

|          |            | 3.1.2 Intra-Prediction, Discrete Cosine Transform and                           |

|          |            | $Quantization  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ |

|          |            | 3.1.3 CABAC                                                                     |

|          | 3.2        | Experimental Methodology                                                        |

|          | 3.3        | SIMD and Operation Fusion                                                       |

|          | <u>າ</u> 4 |                                                                                 |

|          | 3.4        | Custom Instructions for Compute Bound                                           |

|          | 3.4        | Custom Instructions for Compute Bound<br>Applications                           |

|   |                | 3.4.2   | FME Strategy34                                                                                                      |

|---|----------------|---------|---------------------------------------------------------------------------------------------------------------------|

|   | 3.5            | Custo   | m Instructions for Control Bound                                                                                    |

|   |                | Applie  |                                                                                                                     |

|   |                | 3.5.1   | CABAC Strategy                                                                                                      |

|   | 3.6            | Custo   | m Instructions Area Comparison                                                                                      |

|   | 3.7            | Custo   | m Instructions Summary                                                                                              |

|   | 3.8            | Concl   | usion $\ldots \ldots 41$ |

| 4 | Con            | voluti  | on Engine: Balancing Efficiency and Flexibility in                                                                  |

|   | $\mathbf{Spe}$ | cialize | d Computing 43                                                                                                      |

|   | 4.1            | Comp    | utational Models                                                                                                    |

|   | 4.2            | Applie  | cations $\ldots \ldots 47$      |

|   |                | 4.2.1   | Motion Estimation                                                                                                   |

|   |                | 4.2.2   | Scale Invariant Feature Transform (SIFT)                                                                            |

|   |                | 4.2.3   | Demosaic                                                                                                            |

|   |                | 4.2.4   | Mapping to "Map" and "Reduce" Abstraction                                                                           |

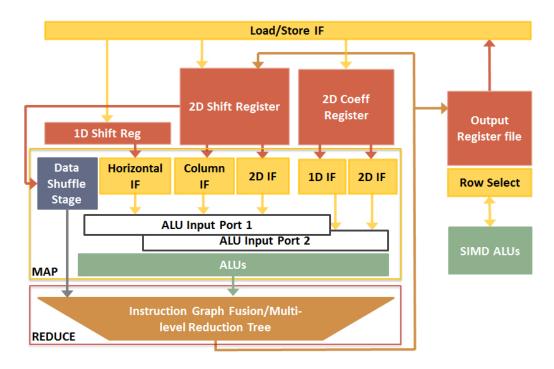

|   | 4.3            | Convo   | lution Engine                                                                                                       |

|   |                | 4.3.1   | Register Files and the Load/Store Unit 60                                                                           |

|   |                | 4.3.2   | Map & Reduce Logic                                                                                                  |

|   |                | 4.3.3   | Instruction Graph Fusion                                                                                            |

|   |                | 4.3.4   | Lightweight SIMD                                                                                                    |

|   |                | 4.3.5   | Custom Functional Units                                                                                             |

|   |                | 4.3.6   | A 2-D Filter Example                                                                                                |

|   |                | 4.3.7   | Resource Sizing                                                                                                     |

|   |                | 4.3.8   | Convolution Engine CMP                                                                                              |

|   |                | 4.3.9   | Programming the Convolution Engine                                                                                  |

|   | 4.4            | Evalu   | ation Methodology                                                                                                   |

|   |                | 4.4.1   | H.264 Motion Estimation                                                                                             |

|   |                | 4.4.2   | SIFT                                                                                                                |

|   |                | 4.4.3   | Demosaic                                                                                                            |

|   | 4.5            | Result  | 5s                                                                                                                  |

|          |       | 4.5.1   | Generating Instances with Varying Degrees of                                                     |     |

|----------|-------|---------|--------------------------------------------------------------------------------------------------|-----|

|          |       |         | Flexibility                                                                                      | 79  |

|          | 4.6   | Conclu  | asion                                                                                            | 82  |

| <b>5</b> | Ana   | lysis o | f Memory Bound Applications                                                                      | 84  |

|          | 5.1   | Speech  | $\mathbf{Recognition}  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $ | 85  |

|          |       | 5.1.1   | CMU Sphinx Speech Recognition                                                                    | 86  |

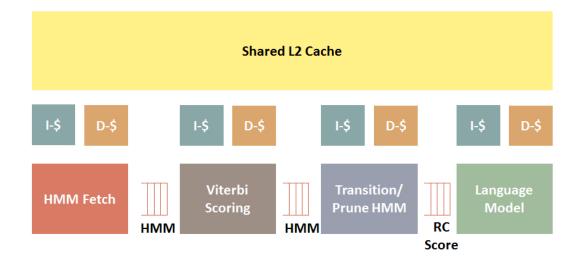

|          | 5.2   | Baselin | ne Speech Recognition System                                                                     | 89  |

|          |       | 5.2.1   | Pruning Stage                                                                                    | 90  |

|          |       | 5.2.2   | Patch List                                                                                       | 90  |

|          |       | 5.2.3   | CMP System                                                                                       | 90  |

|          | 5.3   | Experi  | imental Methodology                                                                              | 92  |

|          |       | 5.3.1   | Processor Optimization Strategy                                                                  | 93  |

|          |       | 5.3.2   | Memory Optimization Strategy                                                                     | 93  |

|          | 5.4   | Result  | s                                                                                                | 95  |

|          |       | 5.4.1   | Processor Optimization Results                                                                   | 96  |

|          |       | 5.4.2   | Memory Optimization Results                                                                      | 98  |

|          | 5.5   | Conclu  | sion                                                                                             | 102 |

| 6        | Con   | clusio  | n                                                                                                | 104 |

| Bi       | bliog | raphy   |                                                                                                  | 107 |

# List of Tables

| 3.1 | Description of VLIW and SIMD resources employed for each sub-          |     |

|-----|------------------------------------------------------------------------|-----|

|     | algorithm.                                                             | 29  |

| 4.1 | Mapping kernels to map and reduce abstraction                          | 55  |

| 4.2 | Sizes for various resources in the convolution engine                  | 68  |

| 4.3 | Energy required for filtering instructions using 32, 64 and 128 ALUs.  | 68  |

| 4.4 | Convolution engine instructions                                        | 71  |

| 5.1 | Memory energy consumption at various levels of hierarchy               | 84  |

| 5.2 | Last level cache misses for the major consumers of memory energy       |     |

|     | before memory optimization                                             | 94  |

| 5.3 | Last level cache misses for the major consumers of memory energy after |     |

|     | memory optimizations.                                                  | 101 |

# List of Figures

| 1.1  | Historic microprocessor power consumption statistics                             | 2  |

|------|----------------------------------------------------------------------------------|----|

| 1.2  | Historic microprocessor power per SPEC (Standard Performance Eval-               |    |

|      | uation Corp.) benchmark score vs. performance statistics                         | 3  |

| 2.1  | Energy breakdown for a high definition H.264 encoder using a Tensilica           |    |

|      | RISC processor.                                                                  | 8  |

| 3.1  | Comparison of functional unit energy with that of a typical RISC in-             |    |

|      | struction in 90nm                                                                | 14 |

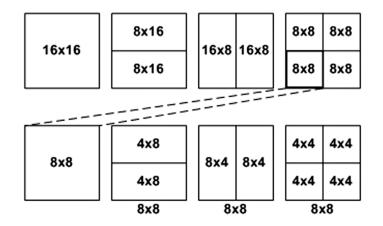

| 3.2  | Supported macro-blocks in H.264                                                  | 16 |

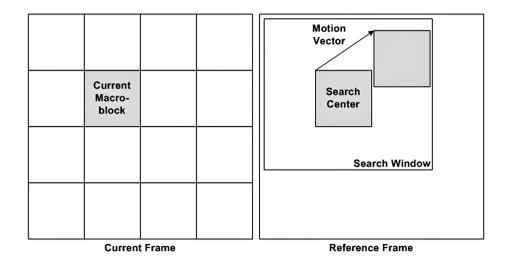

| 3.3  | H.264 Integer Motion Estimation Search Procedure                                 | 17 |

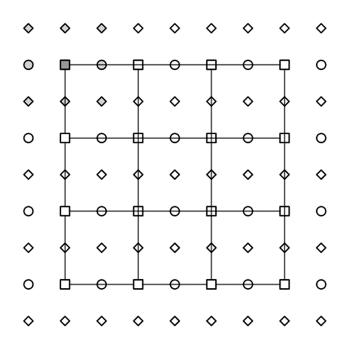

| 3.4  | FME search locations.                                                            | 19 |

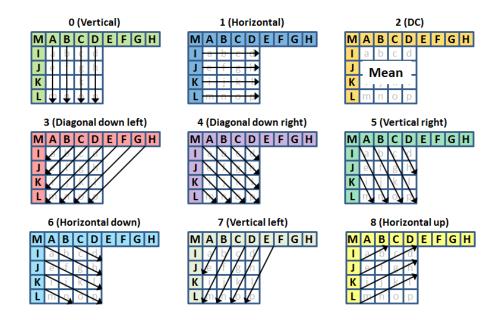

| 3.5  | Luma intra-prediction modes for a 4x4 block. $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 20 |

| 3.6  | Illustration of binarization procedure for CABAC                                 | 22 |

| 3.7  | CABAC context modeling example                                                   | 23 |

| 3.8  | Binary arithmetic coder encoding flow.                                           | 24 |

| 3.9  | Four stage macroblock partition of H.264.                                        | 25 |

| 3.10 | Performance and energy gap of base CMP when compared to an equiv-                |    |

|      | alent ASIC.                                                                      | 26 |

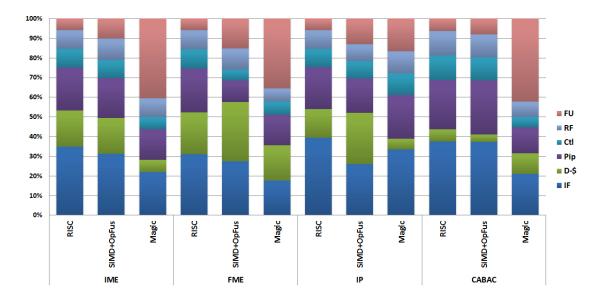

| 3.11 | H.264 energy distribution over different sub-algorithms                          | 27 |

| 3.12 | H.264 processor energy breakdown for base CMP                                    | 28 |

| 3.13 | Comparison of energy consumption at different levels of optimization             |    |

|      | for each sub-alogrithm of H.264                                                  | 29 |

| 3.14 | Speedup comparison at different levels of optimization for each sub-                                          |    |

|------|---------------------------------------------------------------------------------------------------------------|----|

|      | alogrithm of H.264. $\ldots$ | 30 |

| 3.15 | Processor energy breakdown for H.264 at each level of optimization. $\ .$                                     | 31 |

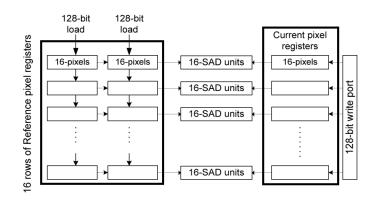

| 3.16 | Custom storage and compute for IME 4x4 SAD                                                                    | 33 |

| 3.17 | FME upsampling unit.                                                                                          | 35 |

| 3.18 | A simplified version of a control bound loop from BAC                                                         | 37 |

| 3.19 | CABAC Arithmetic Encoding Loop.                                                                               | 38 |

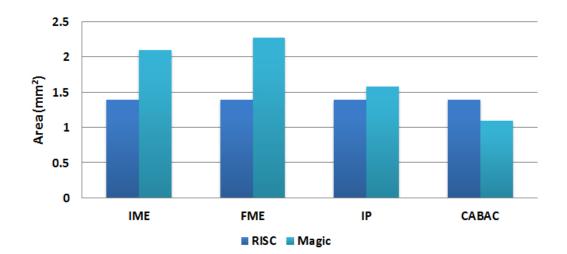

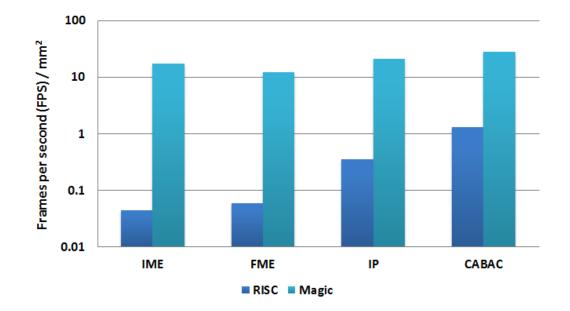

| 3.20 | Area comparison of "magic" instructions with the simple Tensilica                                             |    |

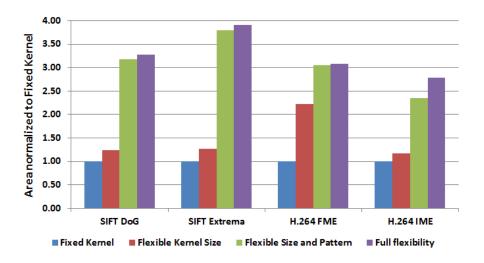

|      | RISC processor for IME, FME, IP and CABAC                                                                     | 39 |

| 3.21 | Comparison of area efficiency $(FPS/mm^2)$ for IME, FME IP and                                                |    |

|      | CABAC                                                                                                         | 40 |

| 4 1  |                                                                                                               |    |

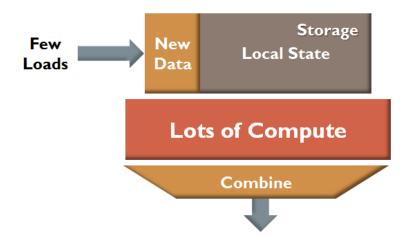

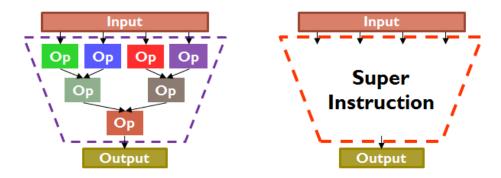

| 4.1  | Constraints a flexible engine must satisfy to remain efficient.                                               | 44 |

| 4.2  | Fusion of individual operations in a super instruction by the generalized                                     |    |

|      | reduction stage.                                                                                              | 47 |

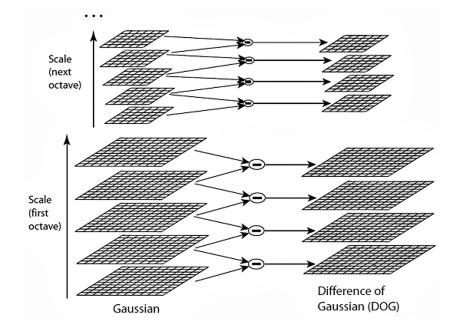

| 4.3  | SIFT difference of Gaussian                                                                                   | 49 |

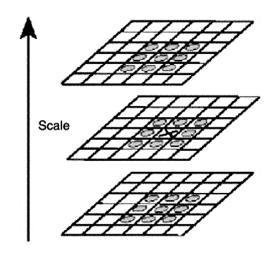

| 4.4  | SIFT Extrema detection                                                                                        | 50 |

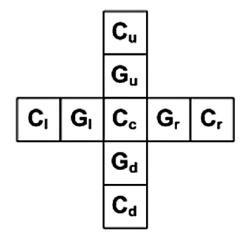

| 4.5  | Luminance interpolation in Demosaic                                                                           | 52 |

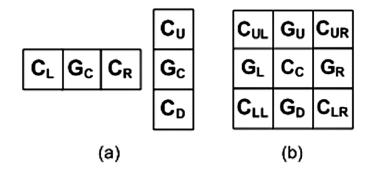

| 4.6  | Chromiance interpolation in Demosaic                                                                          | 53 |

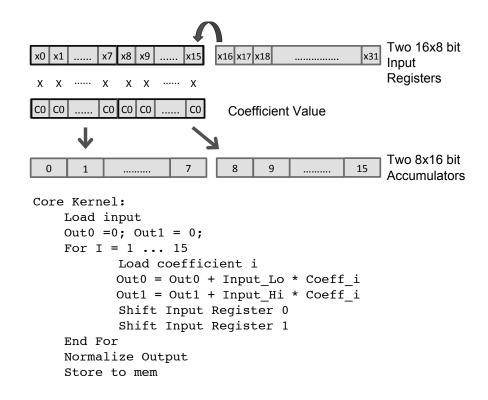

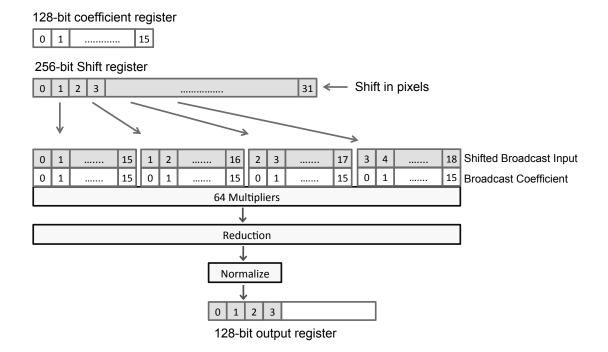

| 4.7  | SIMD implementation of generic 1D convolution                                                                 | 55 |

| 4.8  | 128-bit SIMD implementation of a 16-tap 1D horizontal convolution.                                            | 56 |

| 4.9  | Shift register based implementation of 16-tap 1D horizontal convolution                                       | 57 |

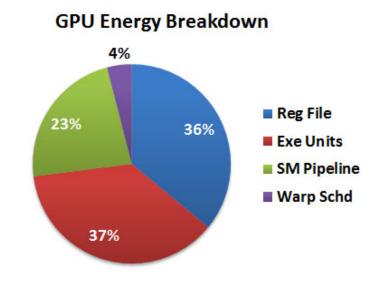

| 4.10 | GPU energy breakdown for SAD                                                                                  | 58 |

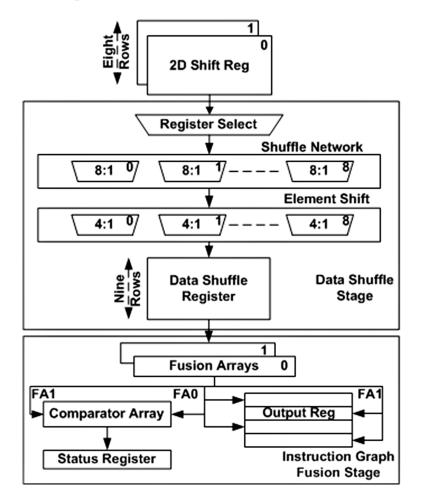

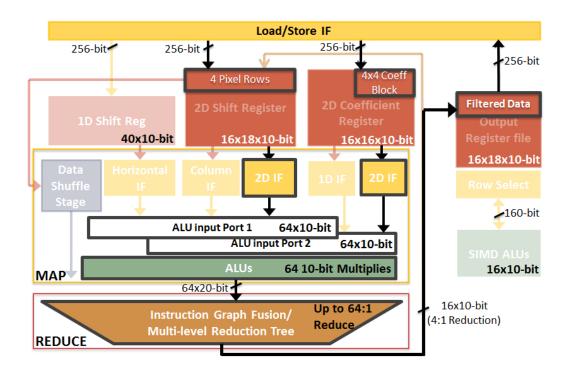

| 4.11 | Block diagram of the convolution engine                                                                       | 59 |

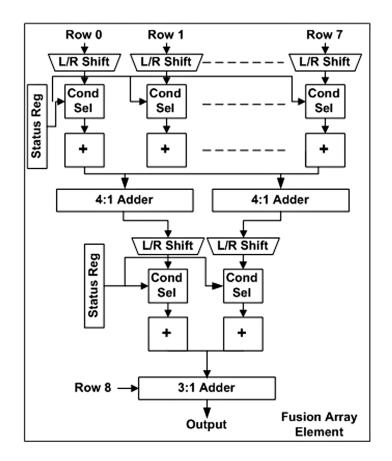

| 4.12 | Complex graph fusion unit.                                                                                    | 63 |

| 4.13 | Instruction graph fusion unit.                                                                                | 64 |

| 4.14 | Execution of a 4x4 2D Filter on the convolution engine                                                        | 66 |

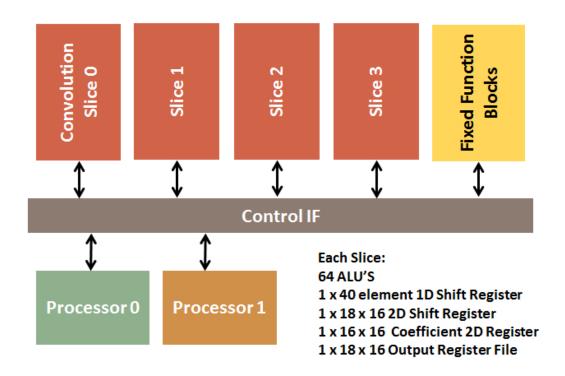

| 4.15 | Communication connections among components of convolution engine                                              |    |

|      | СМР                                                                                                           | 69 |

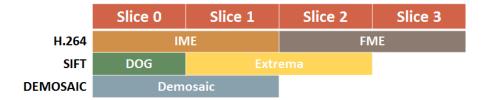

| 4.16 | Mapping of applications to convolution engine CMP                                                             | 74 |

|      |                                                                                                               |    |

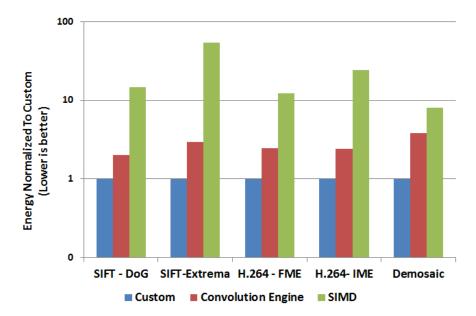

| 4.17 | Energy consumption comparison among convolution engine, custom                   |     |

|------|----------------------------------------------------------------------------------|-----|

|      | cores and SIMD.                                                                  | 77  |

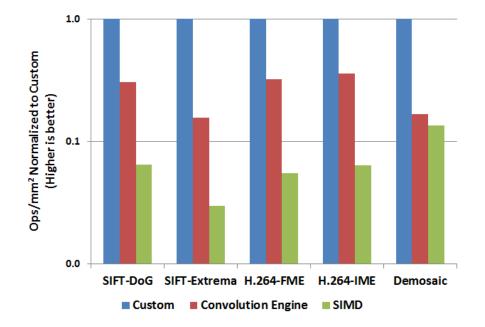

| 4.18 | Comparison of operations per $mm^2$ among convolution engine, custom             |     |

|      | cores and SIMD.                                                                  | 78  |

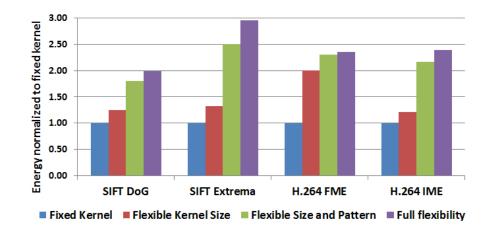

| 4.19 | Change in energy consumption as programmability is incrementally                 |     |

|      | added to the core                                                                | 82  |

| 4.20 | Increase in area as programmability is incrementally added to the core.          | 82  |

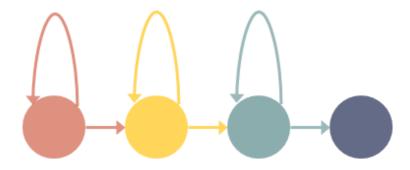

| 5.1  | Four state HMM model used for representing tri-phones in Sphinx 3.0.             | 86  |

| 5.2  | Four stage HMM level partition of Sphinx 3.0                                     | 91  |

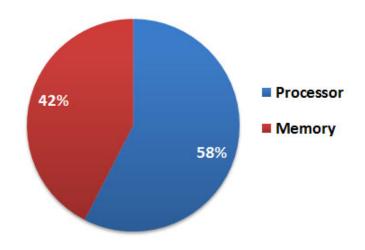

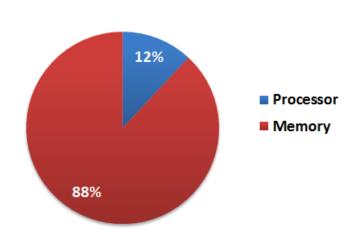

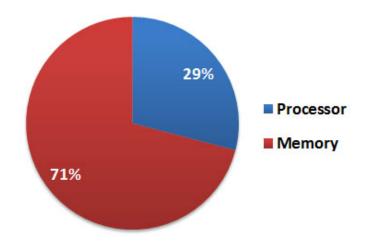

| 5.3  | Energy distribution between the processing elements and the memory               |     |

|      | for the base CMP system.                                                         | 92  |

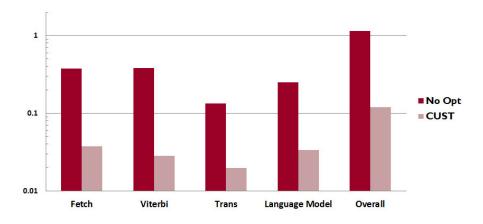

| 5.4  | Improvement in performance over the base system that was operating               |     |

|      | at real-time after the application of custom instructions. $\ldots$ . $\ldots$ . | 96  |

| 5.5  | Improvement in energy per frame over the base system after the appli-            |     |

|      | cation of custom instructions.                                                   | 96  |

| 5.6  | Energy distribution between the processing elements and the memory               |     |

|      | after processor customizations                                                   | 97  |

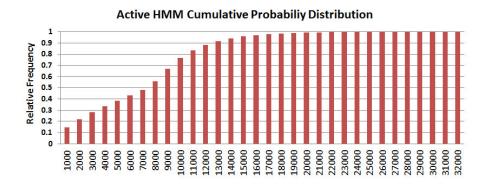

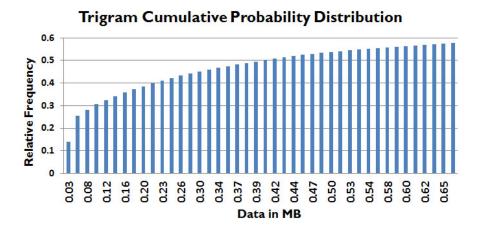

| 5.7  | The plot captures the total size of the HMM data structure in the                |     |

|      | current frame on the x-axis and the relative frequency a structure of            |     |

|      | this size is likely to occur in a given frame on the y-axis. $\ldots$ .          | 98  |

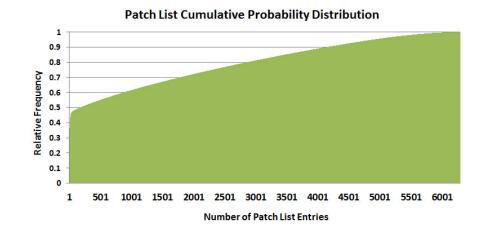

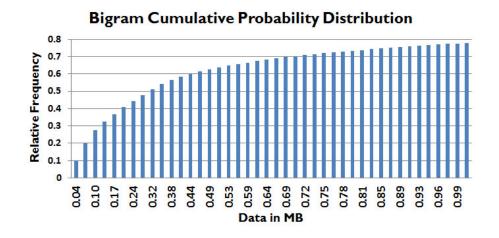

| 5.8  | Relative frequency of a given amount of memory needed to store Patch             |     |

|      | List entries in the current frame                                                | 99  |

| 5.9  | Relative frequency of a given amount of memory needed to store Tri-              |     |

|      | gram word candidates in the current frame                                        | 100 |

| 5.10 | Relative frequency of a given amount of memory needed to store Bi-               |     |

|      | gram word candidates in the current frame.                                       | 101 |

| 5.11 | Energy distribution between the processing elements and the memory               |     |

|      | for the optimized CMP system.                                                    | 102 |

# Chapter 1

# Introduction

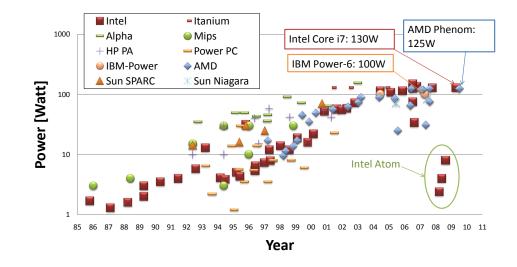

Over the past two decades, chip designers have leveraged technology scaling and rising power budgets to rapidly scale performance. Aided by Dennard's constant field scaling theory [1] chipmakers achieved a triple benefit: each generation supplied more gates per  $mm^2$ , gate delay decreased, and energy per gate switch decreased. Thus scaling alone brought about a significant growth in computing performance while maintaining a constant power profile. However, as shown in Figure 1.1, power and power density continued to increase, which caused a dramatic increase in processor power over the past 20 years. The reason was a combination of designers not following constant field scaling exactly and creating more aggressive designs, thereby increasing performance more quickly than Dennard predicted.

Unfortunately, rising costs of cooling high performance designs exacerbated by the changes to technology scaling beyond 90nm severely compromised our ability to keep power in check rendering most chips power limited. Consequently, almost all systems designed today, from high-performance servers to wireless sensors, are becoming energy constrained. In this power-constrained, post-Dennard era, creating energy-efficient designs is critical. Continually increasing performance in this new era requires lower energy per operation, because the product of operations per second (performance) and energy per operation is power, which is constrained.

Years of research have taught us that the best — and perhaps only — way to save energy is to cut waste. Clearly, the first step is to reduce waste in the design. Clock

Figure 1.1: Historic microprocessor power consumption statistics. Power consumption has increased by over two orders of magnitude in the past two decades. However, as evidenced by the Intel Atom, there is a recent trend of lower power processors for the growing market of battery-operated devices [2]. (PA: Precision Architecture.)

gating prevents a logic block's gates from switching during cycles when their output isn't used, reducing dynamic energy with virtually no performance loss. Power gating goes even further by shutting off power to an entire block when it's unused for longer periods of time, reducing idle leakage power, again at low performance costs.

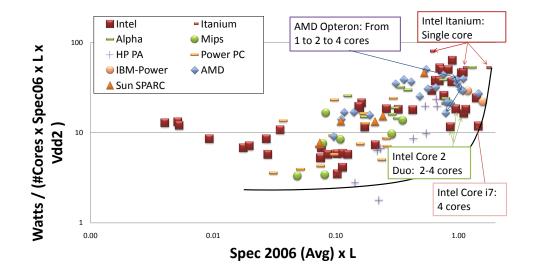

However, power is also wasted indirectly when we waste performance. Higher performance requirements necessitate higher-energy operations, so removing performance waste reduces energy per operation. Using multiple simpler units rather than a single aggressive one, therefore, saves energy when processing parallel tasks. At the system level, this observation is driving the recent push for parallel computing. Backing off from peak performance to create simpler cores enables considerable reductions in energy per operation as shown in Figure 1.2. Although this also harms performance, we can reclaim this lost performance through additional cores at a far lower energy cost. Of course, this approach sacrifices single-threaded performance, and it also assumes that the application is parallel, which isn't always true. However, given the power constraints, this move to parallelization was a trade-off that industry had to make.

Figure 1.2: Historic microprocessor power per SPEC (Standard Performance Evaluation Corp.) benchmark score vs. performance statistics. Performance numbers (x-axis) are the average of the single-threaded SPECint2006 and SPECfp2006 results [3]. To account for technology generation, we normalized the numbers according to feature size L, which is inversely proportional to the inherent technology speed. The y-axis shows power per SPEC score, which is a measure of energy per operation. Energy numbers are normalized to the number of cores per chip and to the technology generation; since  $E = CV^2$  (where E is energy, and C is the capacitance), E is proportional to  $LV^2$ . Note how the move to multicore architectures typically sacrifices single-threaded performance, backing off from the steep part of the curve [2].

Unfortunately, though, we can't rely on parallelism to save us in the long term, for two reasons. First, as Amdahl noted in 1965, with extensive parallelization, serial code and communication bottlenecks rapidly begin to dominate execution time. Thus, the marginal energy cost of increasing performance through parallelism increases with the number of processors, and will start increasing the overall energy per operation. The second issue is that parallelism itself doesn't intrinsically lower energy per operation; lower energy is possible only if sacrificing performance also yields a lower energy design. Unfortunately, this trade-off follows the law of diminishing returns. After we back away from high-power designs, the remaining savings are modest.

Looking forward, the best tool in our power-saving arsenal is customization, because the most effective way to reduce waste is to find a solution that accomplishes the same task with less work. By tailoring hardware to a specific application, customization not only results in energy savings by requiring less work but also improves performance, allowing an even greater reduction of the required energy. The idea of specialization is well-known, and is already applied in varying degrees today. The use of single instruction, multiple data (SIMD) units (such as Intel's streaming SIMD) extension (SSE), vector machines, or graphics processing units) as accelerators is an example of using special-purpose units to achieve higher performance and lower energy [4]. To estimate the potential gain possible through customization we execute a single video compression application, a 720p high definition H.264 encoder, on a Tensilica RISC processor. A staggering 500x difference in energy dissipation per frame is observed between the general-purpose (GP) software based implementation compared to a typical ASIC designed for real-time 720p H.264 encoding [5]. The huge difference is the consequence of the efficiency overheads that exist in a general-purpose (GP) processor due to flexible instructions and data fetch.

However, despite the clear energy efficiency advantage of ASICs, the number of new ASICs built today is not skyrocketing but decreasing, because designing them is too expensive. The design and verification cost for a state-of-the-art ASIC today is well over \$20 million, and the total NRE costs are more than twice that, owing to the custom software required for these custom chips [6][7]. Interestingly, fabrication costs, though very high, account for only roughly 10 percent of the total cost today [6]. That means high design, verification, and software costs are the primary reasons why the number of ASICs being produced today is actually decreasing [7], even though they're the most energy-efficient solution.

Thus, despite the fact that multiprocessors lag far behind ASICs in terms of efficiency, their flexibility enables them to amortize high NRE costs across many applications. However, the desire to achieve ASIC-like compute efficiencies with multiprocessor-like application development costs remains strong and is pushing designers to explore new design methodologies and programmable development platforms. But to fully realize the potential of producing general-purpose chips with better efficiency, we need to fundamentally understand why specialized hardware is more efficient compared to general-purpose systems and how we can leverage that knowledge to build efficient programmable units. Additionally, we need to identify if the huge efficiency gap between ASICs and programmable units is limited to a few applications. If not then what sets the limit? And finally we need to determine how general we can make the flexible core while still maintaining a high level of efficiency.

Identification of sources of inefficiency in general-purpose systems requires first understanding the limitations of existing system optimization techniques across a broad spectrum of applications and determining how well they compare to custom hardware. We review the limitations of the existing low-power architectural techniques in Chapter 2 and present our strategy for detecting the fundamental shortcomings of current programmable systems. Before introducing our energy optimization techniques for the applications that we use in our study, we describe in the same chapter how we classify applications using the dominant consumers of energy: compute, control and memory.

Chapter 3 then looks in more depth at understanding the sources of inefficiency in compute and control bound applications with the help of a 720p HD H.264 encoder. We choose H.264 because it demonstrates the large energy advantage of ASIC solutions (500x) and because there exist commercial ASICs that can serve as a benchmark. Moreover, H.264 contains a variety of computational motifs, from highly compute bound (motion estimation) to control intensive ones (Context Adaptive Binary Arithmetic Coding [CABAC]). Aided by the benchmark ASIC, we analyze the source of the energy overhead in H.264's compute and control bound algorithms, and the rough strategy that we need to use to reduce it.

For compute bound applications, the problem is that the very low per-cycle energy cost of the fundamental operations means that the relative overhead from other sources such as instruction fetch becomes prohibitively large. Since it is generally not possible to reduce these overheads, the only way to get high efficiency is to perform 100s of fundamental operates in each cycle. This then makes the amortized overhead per operation small enough to yield efficient computation. Although, control bound applications also benefit from the aggregation of low-power control flow instructions into a single instruction, it's generally not possible to fuse together more than 10–20 operations; therefore, the efficiency gains are limited.

Because compute bound applications operate on short data and generally possess enough data-parallelism to enable 100s of operations per cycle, our efficiency analysis reveals that they offer the highest efficiency gains. Fortunately, compute bound applications must share a number of characteristics to be compute bound and in Chapter 4 we exploit those features to develop a specialized processor that offers high efficiency while still retaining sufficient programmability. This flexible engine, which we refer to as the Convolution Engine, works for a reasonable percentage of compute bound applications within the domain of imaging and video systems.

After studying efficiency trade-offs between flexibility and customization for compute and control intensive applications, we turn our attention to memory bound applications. In this regard, we analyze Speech Recognition and present our strategies for improving energy efficiency in Chapter 5. We learn that the situation for memory bound applications is fundamentally different, since the energy cost of a memory fetch is significant. While efficiency can be gained by reducing non-memory overhead through parallelism, this will only give a small (3x) energy saving. Instead, efficient hardware solutions use both parallelism and other compute optimization to reduce the compute power, along with exploitation of application characteristics to increase locality in the data fetches. This increased reuse often enables the use of better utilization of smaller and closer on-chip memories, which have much lower energy costs compared to DRAM.

# Chapter 2

# Background

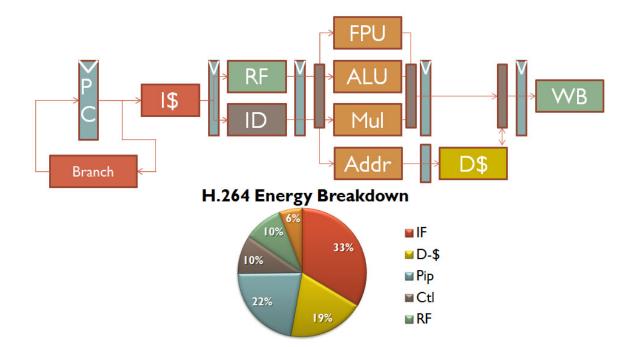

The main benefit that general-purpose (GP) processors possess over ASICs is programmability, but therein lie most of the overheads. Identification of processor inefficiencies stemming from these overheads requires determination of the major consumers of energy in a processor pipeline. With the help of a simple RISC pipeline, shown in Figure 2.1, this chapter highlights major consumers of energy in a processor pipeline, and then provides a brief overview of prior optimization work.

Figure 2.1 depicts the inner workings of a simple RISC pipeline. The pipeline works by fetching an instruction from the instruction cache, which is then transferred to the instruction decode unit. The register file is accessed in parallel with the decode unit and the fetched data is then processed by the arithmetic execution stage. The memory execution stage follows the arithmetic unit and if the fetched instruction requires a memory access, an interaction with the data cache takes place here. And in the end we have the write-back stage.

Execution of a high definition 720p H.264 encoder on a Tensilica RISC processor with a 7-stage pipeline not much different from the one described above, we get an energy breakdown presented in the pie-chart in Figure 2.1. The pie chart reveals that the instruction fetch and decode units (IF) consume the most energy. The energy dissipated in the data cache (D-\$) comes in second followed by the pipeline registers. Interestingly, the arithmetic unit that performs the useful work takes just 6% of the total energy meaning that the rest is all overhead. Yet there must be more to this

Figure 2.1: A simple RISC pipleine is presented at the top and the pie-chart represents the energy breakdown obtained after the execution of a high definition H.264 encoder on a Tensilica core with a 7-stage pipeline. In the pie-chart IF represents instruction fetch and decode energy; D-\$ stands for data-cache energy; Pip stands for energy dissipated in the pipeline registers; energy consumed by the control logic is represented by Ctl; and RF represents the energy dissipated in the register file.

story because if we optimize away the whole overhead we get an improvement of just 20x, not the 500x mentioned in Chapter 1.

Optimization strategies commonly engaged to improve the efficiency of GP processors attempt to reduce or amortize overheads associated with programmability over a larger number of operations. In the first group lie the architectural techniques ranging from instruction registers to hierarchical register files which attempt to reduce the energy consumption of the major overheads. Traditional Vector Processors are a good example of the second group: they use a single instruction to operate on multiple operands [8].

The other approach to efficient computing drops the processor framework, or relegates the processor to handling the UI, and some control, and builds a customized engine for each application. However, as explained in Chapter 1, this requires an enormous design effort, and is becoming hard to justify except for very high volume applications. Somewhere between these two extremes lie extensible processors, which we describe in Section 2.3. These processors provide the framework of a CPU, but allow the user to add his/her own customized instructions. This thesis relies on the Tensilica extensible processor system to generate the data for the experiments presented in later chapters. The next section looks at these optimization techniques in detail, and briefly reviews the contemporary implementations of these ideas.

### 2.1 Embedded Low-Power Multiprocessor (ELM)

The low-power ELM processor [9][10] aims to bridge the enormous efficiency gap between ASICs and GP processors. The design is influenced by the observation that computation doesn't limit the efficiency of embedded processors, instead the burden falls on the inefficient delivery of instructions and data to the functional units. ELM features several innovative mechanisms for improving locality through carefully sized and strategically placed storage structures resulting in enhanced instruction issue and data supply efficiency [9][10].

As a part of the strategy to improve locality, ELM introduces software managed instruction registers placed in close proximity to the functional units. These registers eliminate costly instruction cache accesses by storing the critical code close to the functional units to reduce the fetch energy. In addition to the instruction registers, small operand registers are also added close to the functional units. These registers capture transient data, eliminating the penalty for accessing the big monolithic register file. The big register file also gets its share of enhancements in the form of indexed registers. With the help of register pointers, this scheme eliminates overhead instructions prevalent in compute-intensive applications that benefit from data-reuse in the register files. All these optimizations combine to substantially simplify the design and deliver extremely high efficiency. They estimate an energy per operation of 10pJ in a 45nm technology for short integer data. While this is 10x better than a RISC processor, it is comparable to what SIMD machines can achieve, and still about 10x worse than ASICs.

### 2.2 SIMD Architectures and Vector Machines

Single Instruction Multiple Data (SIMD) is frequently employed in parallel processors to control multiple functional units all performing the same operation on different data. Because SIMD units operate on multiple operands in parallel, appropriately designed SIMD units have a profound effect on the aggregate throughput and efficiency of data-parallel applications. The improvement in efficiency is caused by the amortization of overheads inherent in instruction fetch, decode and pipeline registers over a large number of functional operands. However, the usefulness of SIMD units wanes if the application possesses limited parallelism or is not able to aggregate enough parallel operands to fully utilize the SIMD array. The need to match the SIMD width limits the usefulness of a large SIMD array for many applications. While too wide a width results in waste especially in terms of area and leakage, too small a width entails inefficient exploitation of parallelism.

Large SIMD and vector processors are effective for applications with large dataparallelism [11][12]. To bring the efficiency and performance benefits of SIMD processing to mainstream applications, many contemporary processors have added smaller SIMD units to their pipelines. One of the well-known examples is Intel's streaming SIMD extension (SSE) [13][14] which in addition to operating on multiple parallel data elements, also offer high efficiency complex instructions. The complex instructions are essentially fused data-flow graphs consisting of multiple instructions fused into one operation, further improving the efficiency of SIMD units. As we will see in the next chapter, leveraging these units can also improve energy efficiency for data-parallel applications by upto 10x.

GPUs are generally considered to be the most successful SIMD machines today [11]. They contain a large number of SIMD cores, each running 8–32 data operations in parallel and are optimized for massively data parallel graphics applications. They employ a large number of low control overhead cores, sacrificing single thread performance in favor of very high throughput. To further improve throughput they host a large numbers of threads on each core and threads switch on high memory latency operations. By specializing for their workload characteristic, GPUs are able to get much higher throughput performance and lower energy per operation than general purpose processors. However, these machines are designed for performance and not energy efficiency and many of the features especially in the memory system are not low-energy. To support multiple independent threads, the memory system is designed with a minimal focus on locality resulting in high energy dissipation in the register file and memory system making GPUs unfeasible for our applications. Thus, the resulting energy efficiency is only modestly better than a CPU [15].

### 2.3 Extensible Processors

Extensible processors such as Tensilica's Xtensa provide a base design and instruction set which the designer can extend with custom instructions and datapath units, based on application requirements [16]. Extending the ISA for a given application can be done either manually or using automated tools. Tensilica provides an automated ISA extension tool [17] which has been shown to achieve speedups of 1.2x to 30x for EEMBC benchmarks [18] and signal processing algorithms [19]. Other tools have similarly demonstrated significant gains from automated ISA extension [20][21]. While automatic ISA extension can be very effective, manual creation of custom ISA extensions allows for even higher gains. In various app notes [22][23][24], Tensilica reports speedups of 40x to 300x for kernels such as FFT, AES encryption and DES encryption. We will use this system for the experimental data presented later in the thesis.

To determine the nature and degree of customization which should be supported by future programmable systems, we examine the sources of inefficiency present in a programmable CMP platform and explore which aspects of customization are critical for performance enhancements. We use the approach of customizable processors to incrementally transform a generic CMP into a specialized energy efficient design, to better understand the cost/benefit of different specializations.

### 2.4 Application Classes

The dominant energy consumer in an application governs that application's optimization strategy. If the leading energy consumers are arithmetic operations, the optimization strategy needs to facilitate parallel operation of functional units with minimal data-memory fetches; however, if fetches to memory are abundant, enhancing data localization may present itself as the main challenge. Identification of these consumers requires sifting through an application's instruction energy profile, pruning non-critical operations and grouping the remaining operations as being compute, control or memory. In this thesis we perform this step with the help of Tensilica's XEnergy simulation environment that uses heuristics based upon a database of empirical data and the energy estimates are reported to be within 30% of synthesized RTL [25]. Aided by these energy simulations, we identify leading energy consumers within an application and classify that application as being compute bound, memory bound, or control bound. Despite the simplicity of the process, complications arise when an application exhibits multiple dominant consumers. In this case, we draw inspiration from Amdhal's law and associate the application with the energy consumer that presents itself as the bottleneck in the optimization process.

This classification into compute, control or memory bound applications permits us to explore optimization strategies specifically beneficial for each class of applications, which appreciably enhances their impact. Furthermore, this categorization also enhances our ability to identify algorithmic patterns common across a wide range of applications within each domain, which we can exploit to build efficient yet programmable hardware. We explore this issue further in the next two chapters.

# Chapter 3

# Understanding Sources of Inefficiency in Compute and Control Bound Applications

Compute bound applications are highly arithmetic intensive and perform a considerable amount of arithmetic operations. Unaffected by sequential dependencies, these applications possess a high degree of data-level parallelism permitting them to operate on hundreds of data elements in parallel. A high level of data locality is vital to keep the compute units occupied without frequently accessing the memory, otherwise the application risks becoming memory bound. Thus, for an application to remain compute bound and still meet the data supply needs of the functional units, it must generate little memory traffic and perform a substantial number of operations per memory fetch. Some typical examples of compute intensive imaging applications include H.264 motion estimation, Scale Invariant Feature Transform (SIFT)[26], Demosaic[27], etc.

Performance of compute bound applications responds well to multiprocessor optimization techniques such as single processor multiple data (SPMD). However, energy

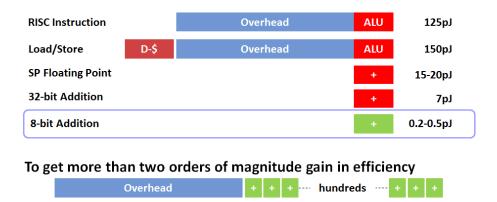

Figure 3.1: Comparison of functional unit energy with that of a typical RISC instruction in 90nm. Strategy for amortizing processor overheads includes executing hundreds of low-power operations per instruction.

gains of general multiprocessing are modest, especially compared with other generally used data-parallel optimization techniques such as SIMD. Widely regarded as the most efficient general-purpose optimization for compute intensive applications, SIMD units are commonly added as datapath extensions to processing cores and their sizes range from ten to twenty elements. Because SIMD units can simultaneously execute tens of data operands in a single cycle, they are able to amortize processor overheads across multiple data elements resulting in an order of magnitude better efficiency compared to SPMD cores However, the resulting efficiency is still 50x off our goal.

Although, scalability issues of SIMD units restrict their efficiency gains, the reason for the lower efficiency can be explained with the help of Figure 3.1, which compares the energy dissipation of various arithmetic operations with the instruction energy of an extremely simple RISC processor. The energy dissipation of arithmetic operations that perform the useful work in a computation remains much lower than the energy wasted in the instruction overheads. The crux of the problem is that the compute intensive applications such as H.264 typically operate on short data requiring just 0.2-0.5pJ (90nm) of energy per operation, which is even an order of magnitude lower than that of a 32-bit RISC ALU whose energy dissipation stands at 7pJ (90nm) shown in Figure 3.1.

Because ASICs perform just the basic low-energy operations and throw away

all the processor overheads including those that reside inside the ALU, they can eclipse general-purpose processors by as much as three orders of magnitude in efficiency. Thus, to achieve higher efficiency, a general-purpose processor not only needs to amortize overheads that exist inside a processor by performing hundreds of lowenergy operations in a cycle, it must also waste almost no energy on memory accesses which stands at 25pJ (90nm) per memory fetch. However, the situation changes dramatically if the basic arithmetic operation in an application requires higher energy such as a floating point operation. In such a case, amortization of processor overheads can be achieved even by executing tens of operations in parallel instead of hundreds, though the resulting efficiency also remains limited to an order of magnitude.

To better understand the potential of creating general-purpose (GP) solutions for compute bound applications, we investigate the sources of overhead in GP systems using a single video compression application, 720p HD H.264 video encode. To build this understanding, we start with a simple RISC chip multiprocessor (CMP) and incrementally transform it to an optimized multiprocessor with specialized hardware units. On this task, a general-purpose software solution takes 500x more energy per frame and 500x more area than an ASIC [5] to reach the same performance. While memory is never an issue in this application, one component, Context Adaptive Binary Arithmetic Coding (CABAC), is control dominated, and after the compute has been optimized, limits both the energy and the performance of the application. We then explore how to reduce the overhead of control bound applications.

### 3.1 H.264

To understand how we customize a generic CMP to efficiently implement H.264, we must first understand the basic components of the H.264 algorithm. Three major functions comprise more than 99% of the total execution time in our base CMP implementation: a) Motion Estimation comprised of Integer Motion Estimation (IME) and Fractional Motion Estimation (FME) b) Intra Prediction (IP), Discrete Cosine Transform and Quantization (DCT/Quant) and c) Context Adaptive Binary Arithmetic Coding (CABAC). We implement the H.264 baseline profile at level 3.1; however, we

Figure 3.2: H.264 supports forty one different macro-block types starting from 16x16 going all the way down to 4x4 and motion estimation is performed separately for each one of these blocks.

use CABAC in place of CAVLC because CABAC is more complex and more challenging to improve [28][29]. CABAC is also more representative of advanced coding steps in other applications

#### 3.1.1 Motion Estimation

A digital video stream consists of a sequence of frames that are closely spaced in time. Because of this proximity, the frames contain a significant amount of redundant information which if not removed, wastes storage as well as precious bandwidth when the stream is transmitted over a network. Motion estimation (ME) eliminates this redundancy by identifying the regions of least change between the current frame and its neighbors using a process known as *block matching*. This procedure involves comparing blocks of pixels in the current frame called *macro-blocks* against expanded regions of pixels in the adjacent frames called *search windows* to find a match. These matched blocks enable the transmission of only the difference between frames; thus, conserving storage as well as network bandwidth.

ME is widely regarded as a key component of many modern day video codecs such as H.264 because it sets the compression efficiency of the video stream. In H.264 ME facilitates high compression efficiency by sub-dividing the current macro-block, a two

Figure 3.3: H.264 Integer Motion Estimation Search Procedure.

dimensional block of 16x16 pixels, into smaller sized regions ranging from 4x4 pixels to 16x16 pixels as shown in Figure 3.2. An improved matching accuracy ensues when a match is sought for each one of these blocks of pixels within the search window. However, this improvement in matching accuracy comes at the cost of computational intensity which increases many fold. Thus, it should come as no surprise that ME accounts for 90% of the execution time when a high definition H.264 encoder is executed in software using JM8.6 reference code [30]. For this implementation we use the Fast Full Search, which will be explained later.

While ME is highly computationally intensive, a small ASIC (in  $mm^2$ ) can easily satisfy the stringent performance and energy requirements of motion estimation; however, it poses a significant challenge for general purpose processors. The energy efficiency of general-purpose processors for H.264 motion estimation tends to be over two orders of magnitude worse compared to an ASIC. To determine the reason behind this dismal display of efficiency from general purpose hardware, we must first understand how ME works. The computation of ME takes place in two steps: it starts with integer motion estimation (IME), which is responsible for finding the match between the current frame and its neighbors, and ends with fractional motion estimation which takes the match from IME and further refines it by searching at sub-pixel granularity.

#### Integer Motion Estimation (IME)

As has been stated above, IME forms the first step in the block matching process. The algorithm that yields the best search results in H.264 is called Full Search (FS). In FS the current frame is divided into 16x16 sized macro-blocks and for each macro-block and its sub-blocks presented in Figure 3.2, a block match is obtained in the reference frame using the process illustrated in Figure 3.3. Aided by motion displacements of already matched macro-blocks, a prediction of the location of the search window is made inside the reference frame. All the pixel locations within the search window are evaluated for a match using Sum of Absolute Difference (SAD) as the cost function shown in Equation (3.1). Motion Vectors (MV) are used to depict the motion between the matching blocks. These motion vectors are transmitted to the decoder along with the residual difference between the matched blocks.

$$SAD = \sum \sum abs(reference - current)$$

(3.1)

Although, FS yields the best search results, it performs a significant amount of redundant calculations by searching the whole window for each sub-block. Fast Full Search (FFS) eliminates these excess calculations by reusing SAD results of smaller blocks to form matches for their larger counterparts in addition to introducing early termination of unfeasible search locations. Despite these modifications that aid in reducing the computational complexity of FS, IME still takes up 56% of the total H.264 encoder execution time and 52% of total energy. Although, numerous fast variants of block matching have been proposed which require less computation[31][32][33], they are sub-optimal and sacrifice search quality by searching fewer locations. Furthermore, some of these algorithms are less suitable for a hardware implementation because they contain a non-deterministic number of pixel matching iterations, irregular workload distribution between iterations and the presence of branch instructions.

Figure 3.4: The squares represent IME's best match for a 4x4 block. The greyed out locations at the top left represent the nine locations searched in FME to match the top left pixel.

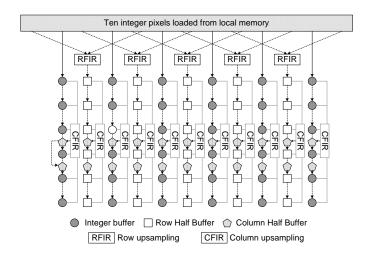

#### Fractional Motion Estimation (FME)

While IME performs motion estimation at integer pixel granularity, it is possible that motion may be better represented at the sub-pixel level. The task of Fractional Motion Estimation (FME) is to refine the match obtained by IME to finer granularities. Consider Figure 3.4 which illustrates the first step of the process. In this step, the pixels in the reference frame adjacent to the IME match are up-sampled to a half pixel granularity using Equation (3.2). Similar to IME, FME also subtracts the upsampled reference pixels from the pixels of the current macro-block; but, to better approximate the processing of the proceeding H.264 pipeline, FME performs maching using a modified SAD algorithm called Sum of Absolute Transformed Difference (SATD). In this algorithm a Hadamard Transform is performed on the residues to approximate the effects of the Discrete Cosine Transform (DCT) which resides further down the pipeline — DCT is tasked with zeroing out as many residues as possible without compromising fidelity. Using SATD as the cost metric, nine locations including the

Figure 3.5: Luma intra-prediction modes for a 4x4 block [28][34][35].

original match are searched. In the second step of the process, the half-pixel search is further refined by searching eight locations around the half-pixel match at a quarter pixel granularity providing us with the final motion vector (MV). The algorithm used for quarter pixel up-sampling is a simple bi-linear filter.

$$x_{upsampled} = x_{-2} - 5x_{-1} + 20x_0 + 20x_1 - 5x_2 + x_3 \tag{3.2}$$

FME is also data parallel like IME, but it has some sequential dependencies and a more complex computation kernel which makes it more challenging to parallelize. FME takes up 36% of the total execution time and 40% of total energy.

### 3.1.2 Intra-Prediction, Discrete Cosine Transform and Quantization

Unlike IME and FME, intra-Prediction uses previously encoded neighboring image blocks from the current frame to form an alternate prediction for the current imageblock. To maintain a high prediction accuracy, intra-prediction supports a large number of luminance and chrominance prediction modes: nine luminance modes for 4x4 blocks, four luminance modes for 16x16 blocks and four chrominance modes. Generation of the prediction for each block requires intra-prediction to compare the prediction results of various linear combinations of previously encoded and reconstructed neighboring blocks from the left and the top. Figure 3.5 presents the formation of nine luminance prediction modes employed for predicting 4x4 blocks. Although, the algorithm is dominated by arithmetic operations, the computation is much less regular than the motion estimation algorithms and the performance is marred by sequential dependencies between current blocks and their neighbors.

The residual data obtained by subtracting the predicted image block from the current image block is then transformed using a 4x4 integer approximation to the Discrete Cosine Transform (DCT) [36]. A set of coefficients are produced by the transform, which are then quantized (quant) and sent to CABAC. The precision of the quantization process is governed by the quantization parameter (QP), which is typically chosen to strike a balance between the quality of the output bit-stream and the compression ratio. Although, the basic function of DCT and Quant is relatively simple and data parallel, it is invoked a large number of times for each 16x16 image block, which calls for an efficient implementation. For the rest of this paper, we merge the operations of intra-prediction, DCT and Quant into the IP stage. The combined operation accounts for 7% of the total execution time and 6% of total energy.

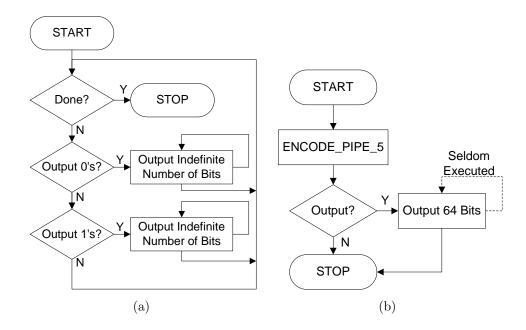

#### 3.1.3 CABAC

The coding efficiency of H.264 is significantly enhanced by the use of Context Adaptive Binary Arithmetic Coding (CABAC). It is extensively utilized to deliver high quality video at low-bitrates. While it takes less than 2% of the execution time and

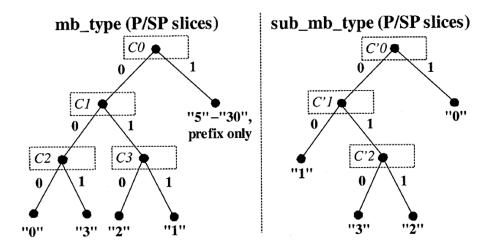

Figure 3.6: Illustration of the binarization for (a) macro-block type (mb\_type) and (b) sub-macro-block type (sb\_mb\_type) for two different slice types [37].

total energy in a high definition H.264 encoder, CABAC often becomes the bottleneck in parallel systems due to its sequential nature. To entropy encode the H.264 bit-stream CABAC employs a three step process: binarization of non-binary input syntax elements (SE), context modeling of binarized bin strings and binary arithmetic coding [37].

#### Binarization

In CABAC binarization is regarded as the "pre-processing" step to the subsequent stages of context modeling and arithmetic coding. The main task of binarization is to reduce the alphabet size of the non-binary syntax elements such as macroblock type and motion vector difference for encoding by converting the input syntax elements into binary codes while binary valued syntax elements bypass this stage. As shown in Figure 3.6, the input syntax elements are uniquely mapped to sequences of binary decisions called bins, interpretable in the context of a binary code tree [38]. Because of the reduction in the alphabet size, less complex binary arithmetic coders become available, substantially reducing the compute requirements. The conversion also allows maintenance of statistical properties at the level of individual bins; thus, improving coding efficiency.

|  |   | B |  |

|--|---|---|--|

|  | A | С |  |

|  |   |   |  |

Figure 3.7: Illustration of a context template consisting of two neighboring syntax elements A and B to the left and on top of the current syntax element C[37].

### **Context Modeling**

The context modeling (CM) is tasked with assigning probability models to select "bins". CM contains 399 context models with each model being 7-bits wide. Out of the 7-bits, 6-bits represent the probability associated with the bin and the remaining 1-bit indicates the most probable symbol (MPS) of the context bin. The probabilities are updated in the arithmetic coding stage.

Because the coding efficiency of binarized symbols is determined by a Context Model, selecting a model that accurately captures the statistical dependencies of the bins and keeping it up to date during the encoding process is essential [37]. Probability models assigned to selected bins of the binarized symbols are used in the subsequent arithmetic coding stage to drive the output bit stream. Although, the modeling process starts by passing each bin through a coding mode decision, not every bin is assigned a context model. Modeling is skipped for less frequently observed bins and bins thought to have an even probability distribution. However, depending upon the symbol type, the bins that are more frequently observed can choose among four different types of context models. As shown in Figure 3.7, the first type of context model involves assigning probability models to a syntax element depending upon the context of the two neighbors in the past of the current syntax element.

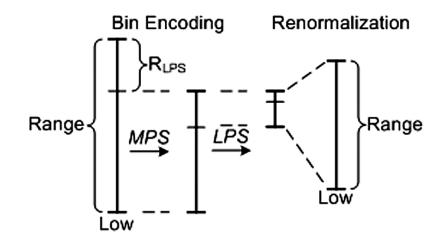

Figure 3.8: Bin encoding flow, along with the re-normalization step for when the Range of the encoding interval falls below a certain threshold.

The second type, which is only available for syntax elements belonging to macroblock types, takes into account the values of the previously coded bins  $(b_0, b_1, b_2 b_{i-1})$ to decide the context model. In contrast, the third and the fourth types, which are available for residual data, depend upon the position or level of the bin in the scanning path[39]. All of the 399 context models available in CABAC are divided into these four categories.

### **Binary Arithmetic Coding**

Binary arithmetic coding (BAC) stage employs a recursive interval sub-division technique to produce the output bit stream. As explained in [37] BAC works by repeatedly sub-dividing the encoding interval based upon *Least Probable Symbol* (LPS) or the *Most Probable Symbol* (MPS) obtained from the context modeling stage. To illustrate this further let's consider Figure 3.8. In the figure the binary encoding interval is represented by "Low" as its lower bound and "Range" as its width. Assuming that  $p_{LPS}$ represents the probability of LPS, BAC works by sub-dividing the encoding interval into two sub-ranges:  $R_{LPS} = R * p_{LPS}$  representing the Range associated with *LPS* and  $R - R_{LPS}$  representing the Range associated with MPS. The observed binary decision of the bin, LPS or MPS, identifies which sub-interval,  $R_{LPS}$  or  $R_{MPS}$ , is used for further processing. Because "Range" and "Low" are represented by a finite number of bits, to ensure that the precision of "Range" is representable in hardware, a renormalization step is undertaken when the "Range" falls below a certain limit. Because by design renormalization takes a variable number of iterations, it presents a serious challenge for any hardware implementation.

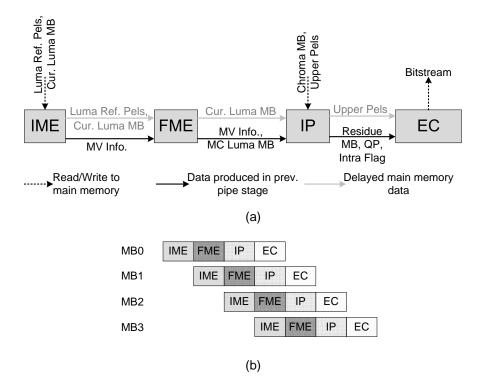

## **3.2** Experimental Methodology

Figure 3.9: Four stage macroblock partition of H.264. (a) Data-flow between stages. (b) How the pipeline works on different macroblocks. IP stands for Intra-Prediction. EC is CABAC [40].

To understand what is needed to gain ASIC level efficiency, we use existing H.264 partitioning techniques adopted by ASIC implementations [5], and modify the H.264 encoder reference code JM 8.6 [30] to remove dependencies in IME motion vector

prediction with minimal loss in quality and allow mapping of the three major algorithmic blocks to the four-stage macro-block (MB) pipeline shown in Figure 3.9. This mapping exploits task level parallelism at the macro-block level and significantly reduces the inter-processor communication bandwidth requirements by sharing data between pipeline stages.

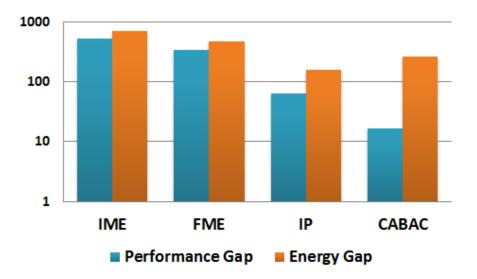

Figure 3.10: The performance and energy gap for base CMP implementation when compared to an equivalent ASIC [40].

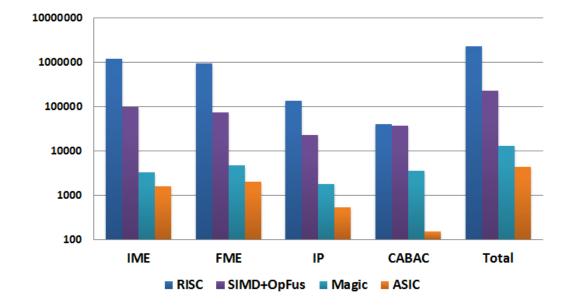

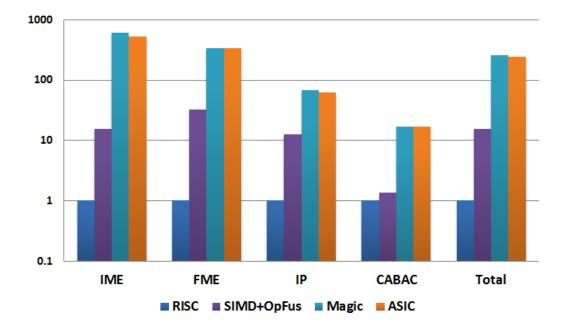

In the base system, we map this four-stage macro-block partition to a fourprocessor Tensilica CMP system where each processor has 16KB 2-way set associative instruction and data caches. Figure 3.10 highlights the large efficiency gap between our base CMP and the reference ASIC for individual 720p HD H.264 sub-algorithms. The energy required for each RISC instruction is similar and as a result, the energy required for each task (shown in Figure 3.11) is related to the cycles spent on that task. The RISC implementation of IME, which is the major contributor to performance and energy consumption, has a performance gap of 525x and an energy gap of over 700x compared to the ASIC. IME and FME dominate the overall energy and thus need to be aggressively optimized. However, we also note that while IP and CABAC are much smaller parts of the total energy delay, even they need about 100x energy improvement to reach ASIC levels.

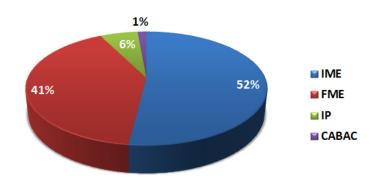

Figure 3.11: Processor energy breakdown for base implementation, over the different H.264 sub-algorithms. In the chart, IME takes 52% of the total energy followed by FME that accounts for 41% of the total. IP consumes 6% of the total while CABAC takes just 1% of the total [40].

Although, Figure 3.10 presents performance comparison for each processor independently, when functioning in a macro-block level pipeline, IME becomes the bottleneck restricting system performance to only 0.06 FPS. Allocation of more computing resources to IME and FME computationally balances the pipeline, but it has a negligible impact on energy efficiency and the improvement in performance remains below 2x. Needless to say, this imbalance has an insignificant effect on the two to three orders of magnitude performance and energy gap between the base CMP system and the ASIC that we are looking to close.

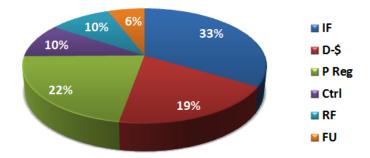

At approximately 8.6B instructions to process 1 frame, our base system consumes about 140 pJ per instruction; a reasonable value for a simple 90nm RISC processor running at 1.1V. To further analyze the energy efficiency of this base CMP implementation we break the processor's energy into different functional units as shown in Figure 3.12. This data makes it clear how far we need to go to approach ASIC efficiency. The energy spent in instruction fetch (IF) is an overhead due to the programmable nature of the processors and is absent in a custom hardware state machine, but eliminating all this overhead only increases the energy efficiency by less than one third. Even if we eliminate everything but the functional unit energy, we still end up with energy savings of only 20x — not nearly enough to reach ASIC levels.

Figure 3.12: Processor energy breakdown for base implementation. IF (33%) is instruction fetch/decode. D-\$ (19%) is data cache. P Reg (22%) includes the pipeline registers, buses, and clocking. Ctrl (10%) is miscellaneous control. RF (10%) is register file. FU (6%) is the functional units [40].

Inspired by GPUs and Intel's SSE instructions, we first apply datapath extensions that are relatively general-purpose data-parallel optimizations and consist of single instruction, multiple data (SIMD) and multiple instruction issue per cycle (we use long instruction word, or VLIW), with a limited degree of algorithm-specific customization coming in the form of operation fusion — the creation of new instructions that combine frequently occurring sequences of instructions. This step represents the datapaths in current state–of–the–art optimized CPUs or simple extensions to them. In the next step, we replace these generic datapaths by custom units, and allow unrestricted tailoring of the datapath by introducing new compute operations as well as new register file structures.

The results of these customizations are shown in Figures 3.13 through 3.15. The next three sections describe these results in detail and evaluate the effectiveness of these three customization strategies. Collectively, these results describe how efficiencies improve by 170x over the baseline CMP.

Figure 3.13: Each set of bar graphs represents energy consumption ( $\mu$ J) at each stage of optimization for IME, FME, IP and CABAC respectively. The first bar in each set represents base RISC energy; followed by RISC augmented with SIMD and operation fusion; and then RISC augmented with "magic" instructions. The last bar in each group indicates energy consumption by the ASIC [40].

|     | VLIW<br>Slots | Register File Size            | SIMD<br>Width | Load/Store<br>Width |

|-----|---------------|-------------------------------|---------------|---------------------|

| IME | 2             | 16 rows x 16 cols x 8-bit     | 16            | 128-bit             |

| FME | 2             | 32  rows x  18  cols x  9-bit | 18            | 128-bit             |

| IP  | 2             | 16  rows x  8  cols x  8-bit  | 8             | 64-bit              |

Table 3.1: Description of VLIW and SIMD resources employed for each sub-algorithm.

# **3.3** SIMD and Operation Fusion

Using Tensilica's TIE extensions we add VLIW instructions and SIMD execution units with vector register files of custom depths and widths as described in Table 3.1. A single SIMD instruction performs multiple operations (8 for IP, 16 for IME, and 18 for FME), reducing the number of instructions and consequently reducing IF energy. VLIW instructions execute 2 operations per cycle, further reducing cycle count. As expected, DLP algorithms using SIMD units show a large decrease in processor

Figure 3.14: Speedup at each stage of optimization for IME, FME, IP and CABAC [40].

energy; speedup increases as the number of instructions executed decreases. IME and FME use 16 and 18-way SIMD datapaths and achieve speedups of 10x and 14x. Intra/DCT/Quant using an 8-way SIMD datapath achieves a speedup of 6x. The SIMD units use custom-width functional units instead of standard 32-bit versions to enable more efficient computation, and generally run between 8 and 16 bits. Moreover, SIMD operations perform wider register file and data cache accesses which are more energy efficient compared to narrower accesses. Therefore all components of instruction energy depicted in Figure 3.12 get a reduction through the use of these enhancements. Unfortunately, even performing sixteen concurrent operations barely increases the percentage energy used by the functional units, which still comprise around 10% of the total.

We further augment these enhancements with operation fusion, in which we fuse together frequently occurring complex instruction sub-graphs for both RISC and SIMD instructions. To prevent the register file ports from increasing, the fused instructions are restricted to use up to two input operands and can produce only one

Figure 3.15: Processor energy breakdown for H.264. IF is instruction fetch/decode. D-\$ is data cache. Pip is the pipeline registers, buses, and clocking. Ctl is random control. RF is the register file. FU is the functional elements. Only the top bar or two (FU, RF) contribute useful work in the processor. For this application it is hard to achieve much more than 10% of the power in the FU without adding custom hardware units [40].

output. One example of operation fusion is the sum-of-absolute-difference operator used in IME in which we fuse together difference, absolute and sum operations to create a highly optimized two input, one output SAD instruction. Operation fusion improves energy efficiency by reducing the number of instructions and also by reducing the number of register file accesses by internally consuming short-lived intermediate data. Additionally, fusion gives us the ability to create more energy-efficient hardware implementations of the fused operations such as multiplication implemented using shifts and adds. The reductions due to operation fusion are less than 2x in energy and less than 2.5x in performance.

With SIMD, VLIW and Op Fusion support, IME, FME and IP processors achieve speedups of around 15x, 30x and 10x, respectively. CABAC is not data parallel and benefits only from VLIW and op fusion with a speedup of merely 1.1x and almost no change in energy per operation. Overall, the application gets an energy efficiency gain of almost 10x, but still uses greater than 50x more energy than an ASIC. To reach ASIC levels of efficiency, we need a different approach.

# 3.4 Custom Instructions for Compute Bound Applications