### BLOCK PARALLEL PROGRAMMING FOR REAL-TIME APPLICATIONS ON MULTI-CORE PROCESSORS

### A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

David Black-Schaffer March 2008

© Copyright by David Black-Schaffer 2008 All Rights Reserved I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

(William J. Dally) Principal Adviser

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

(Mark Horowitz)

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

> (Anwar Ghuloum (Intel Inc.))

Approved for the University Committee on Graduate Studies.

# Preface ? Abstract or isthet offerent.

This thesis presents a streaming block-parallel programming language for describing applications with hard real-time constraints and several transformations for parallelizing and mapping such applications to many-core architectures. The language parameterizes the data movement within the application in such a manner as to enable simple application analysis and rapid software development. Key enhancements for both programmer productivity and application analyzability include the use of native two-dimensional data streams to simplify image processing algorithms, flexible control distribution for intuitive and analyzable synchronous and asynchronous control, explicit data dependency edges for specifying limited parallelism, and multiple computation methods per kernel. The benefits of this application description are shown through the intuitive analyses and manipulations required to parallelize, buffer, and map such applications to a many-core architecture while insuring that they meet their real-time computation requirements.

To evaluate this programming approach, a program analysis and manipulation framework and a cycle-accurate simulation environment were constructed. These were used to automatically analyze, parallelize, buffer, and execute a variety of test programs to insure that they met their specified real-time constraints. The results suggest that this block-parallel programming approach is both easier to use and analyze than previous streaming programming models.

### Acknowledgements

First and foremost I must thank my wife Annica. Without her support, encouragement, and belief in my ability to complete this work, it would never have happened.

Secondly, I am grateful to my advisor Bill. Not only has he supported and guided me through this processes, but he is one of those rare people with enough experience and knowledge to almost always be right, but enough self-confidence and grace to admit it when he is not. Interacting with him has always been academically challenging, but his push to keep the big picture in mind and hone in on the essence of the problem has been invaluable.

Thirdly, my committee members Mark and Anwar have provided me with different points of view which have helped me to focus on the value of my work and its presentation.

I must also thank my family, in particular my parents, for their unending support and encouragement during my long tenure at Stanford. Even their gentle insinuations that graduating would be appreciated have been helpful.

And of course I thank my friends and colleagues here at Stanford. In the CVA group I am grateful to James Balfour, Mattan Erez, Paul Hartke, Abhishek Das, JungHo Ahn, Tim Knight, Vishal Parikh, JongSoo Park, James Chen, and Curt Harting, and in the SOE Charlie Orgish and Keith Gaul. My special thanks go to my friends Kristof Richmond, Greg and Cami Kuhnen, Oren and Dorit Kerem, Tibor Fabian and Rika Yonemura, and Sarah Seestone and Darsi Rueda. And, of course, thanks to the members of the *Seleccion Natural* soccer team for all of the fun (and injuries) I've had over the past several years.

# Contents

| Pı       | refac          | e      |                                    | v         |

|----------|----------------|--------|------------------------------------|-----------|

| A        | ckno           | wledge | ments                              | vi        |

| 1        | Intr           | oducti | on                                 | 1         |

|          | 1.1            | Practi | cal Block-parallel Programming     | 1         |

|          |                | 1.1.1  | The 2D Streaming Model             | 3         |

|          |                | 1.1.2  | Block Programming Example          | 5         |

|          | 1.2            | Contri | butions                            | 11        |

|          | 1.3            | Thesis | Overview                           | 12        |

| <b>2</b> | Bac            | kgrour | nd                                 | 15        |

|          | 2.1            | Synch  | ronous Data Flow                   | 15        |

|          | 2.2            | Stream | ning architectures                 | 17        |

|          |                | 2.2.1  | MIT's Raw                          | 18        |

|          |                | 2.2.2  | Stanford's Imagine                 | 19        |

|          |                | 2.2.3  | Others Streaming Architectures     | 21        |

| 3        | $\mathbf{Rel}$ | ated W | Vork                               | <b>24</b> |

|          | 3.1            | Stream | ning Languages and Implementations | 24        |

|          |                | 3.1.1  | StreamIt                           | 24        |

|          |                | 3.1.2  | StreamC and KernelC                | 29        |

|          |                | 3.1.3  | Brook                              | 31        |

|          |                | 3.1.4  |                                    | 32        |

|          | 3.2 | Multi-dimensional Synchronous Data Flow .     |   | <br> | <br> |   | 33 |

|----------|-----|-----------------------------------------------|---|------|------|---|----|

|          | 3.3 | Summary                                       |   | <br> | <br> | • | 36 |

| 4        | App | olication Model                               |   |      |      |   | 38 |

|          | 4.1 | The Application Graph                         |   | <br> | <br> |   | 39 |

|          |     | 4.1.1 Simplified Application Graph $\ldots$ . |   | <br> | <br> |   | 40 |

|          |     | 4.1.2 Full Application Graph                  |   | <br> | <br> |   | 41 |

|          |     | 4.1.3 Building Applications                   |   | <br> | <br> |   | 43 |

|          | 4.2 | Data Model                                    |   | <br> | <br> |   | 45 |

|          |     | 4.2.1 Inputs and Outputs                      |   | <br> | <br> |   | 46 |

|          |     | 4.2.2 Tokens                                  |   | <br> | <br> |   | 47 |

|          |     | 4.2.3 Implementation                          |   | <br> | <br> |   | 50 |

|          | 4.3 | Computation Model                             |   | <br> | <br> |   | 51 |

|          | 4.4 | Kernel Examples                               |   | <br> | <br> |   | 53 |

|          |     | 4.4.1 Multiple Inputs                         |   | <br> | <br> |   | 53 |

|          |     | 4.4.2 Multiple Methods                        |   | <br> | <br> |   | 54 |

|          |     | 4.4.3 ControlTokens                           |   | <br> | <br> |   | 55 |

|          | 4.5 | Discussion                                    |   | <br> | <br> |   | 57 |

|          |     | 4.5.1 Application Model                       |   | <br> | <br> |   | 57 |

|          |     | 4.5.2 Data Model                              |   | <br> | <br> |   | 61 |

|          |     | 4.5.3 Computation Model                       |   | <br> | <br> |   | 62 |

|          |     | 4.5.4 Scheduling                              |   | <br> | <br> |   | 63 |

|          | 4.6 | Conclusions                                   |   |      |      |   | 64 |

| <b>5</b> | App | olication Analysis                            |   |      |      |   | 66 |

|          | 5.1 | Frame Sizes, Frame Rates, and Iteration Size  | s | <br> | <br> |   | 66 |

|          | 5.2 | Data Flow Analysis                            |   | <br> | <br> |   | 68 |

|          |     | 5.2.1 Feedback                                |   | <br> | <br> |   | 70 |

|          | 5.3 | Example                                       |   | <br> | <br> |   | 71 |

|          | 5.4 | Discussion                                    |   | <br> | <br> |   | 75 |

| 6 | Buf                  | fers and Insets                                                                                                | 77  |

|---|----------------------|----------------------------------------------------------------------------------------------------------------|-----|

|   | 6.1                  | Buffers                                                                                                        | 78  |

|   |                      | 6.1.1 Buffer Sizing                                                                                            | 78  |

|   |                      | 6.1.2 Implementation $\ldots$ | 83  |

|   | 6.2                  | Insets                                                                                                         | 83  |

|   |                      | 6.2.1 Data Flow Analysis for Insets                                                                            | 85  |

|   |                      | 6.2.2 Zero Padding                                                                                             | 91  |

|   | 6.3                  | Automatic Insertion of Buffers and Insets                                                                      | 92  |

|   | 6.4                  | Discussion                                                                                                     | 95  |

| 7 | Par                  | allelization                                                                                                   | 98  |

|   | 7.1                  | Split/Join Kernels                                                                                             | 99  |

|   | 7.2                  | Data Parallel Kernels                                                                                          | 100 |

|   | 7.3                  | Kernels with limited parallelism                                                                               | 103 |

|   | 7.4                  | BufferKernels                                                                                                  | 104 |

|   | 7.5                  | Results                                                                                                        | 108 |

|   | 7.6                  | Discussion                                                                                                     | 113 |

|   |                      | 7.6.1 BufferKernel Data Reuse                                                                                  | 113 |

|   |                      | 7.6.2 Split/Join Inefficiencies                                                                                | 118 |

|   |                      | 7.6.3 Analysis                                                                                                 | 120 |

| 8 | $\operatorname{Tin}$ | ne Multiplexing                                                                                                | 123 |

|   | 8.1                  | Naïve Mappings                                                                                                 | 124 |

|   | 8.2                  | Greedy Merge Algorithm                                                                                         | 127 |

|   | 8.3                  | Results                                                                                                        | 129 |

|   |                      | 8.3.1 Greedy Mapping Results                                                                                   | 129 |

|   |                      | 8.3.2 General Results                                                                                          | 129 |

|   | 8.4                  | Discussion                                                                                                     | 133 |

| 9 | Cor                  | nclusions                                                                                                      | 136 |

| Α  | Plac         | Placement 1                                                                                                       |     |  |  |  |

|----|--------------|-------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

|    | A.1          | Simulated Annealing                                                                                               | 141 |  |  |  |

|    | A.2          | Cost Function                                                                                                     | 142 |  |  |  |

|    | A.3          | Results                                                                                                           | 142 |  |  |  |

| В  | Sim          | ulator Implementation                                                                                             | 145 |  |  |  |

|    | B.1          | Functional Simulation via Threads                                                                                 | 145 |  |  |  |

|    | B.2          | "Cycle-accurate" Simulation $\ldots \ldots \ldots$ | 146 |  |  |  |

|    | B.3          | Enabling Time-multiplexing                                                                                        | 147 |  |  |  |

|    | B.4          | Parameters                                                                                                        | 147 |  |  |  |

|    | B.5          | Application Correctness                                                                                           | 148 |  |  |  |

|    | B.6          | Simulation Traces                                                                                                 | 149 |  |  |  |

| С  | Futu         | ıre Work                                                                                                          | 151 |  |  |  |

|    | C.1          | Variable Rates and Sizes                                                                                          | 151 |  |  |  |

|    | C.2          | Phased Computation                                                                                                | 152 |  |  |  |

|    | C.3          | Dynamic Data Fetch                                                                                                | 153 |  |  |  |

|    | C.4          | Merging Buffers and Kernels                                                                                       | 153 |  |  |  |

|    | C.5          | High-level Blocking                                                                                               | 154 |  |  |  |

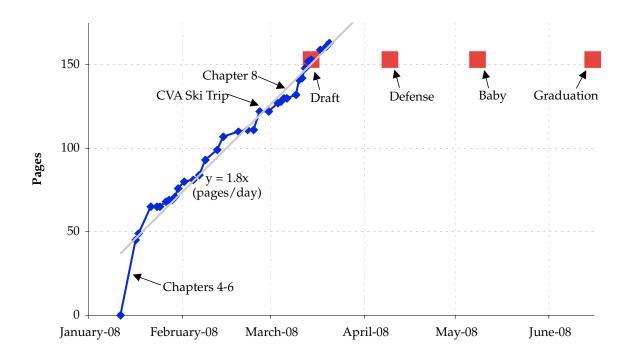

| D  | The          | sis Writing Progress                                                                                              | 156 |  |  |  |

| Bi | Bibliography |                                                                                                                   |     |  |  |  |

# List of Tables

| 5.1 | Default data analysis transfer functions                            | 68  |

|-----|---------------------------------------------------------------------|-----|

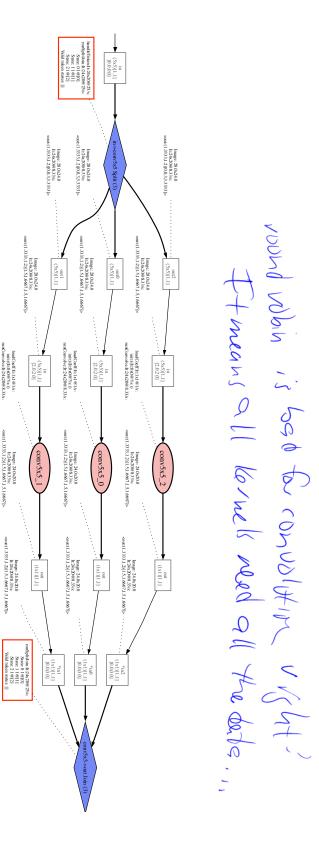

| 7.1 | Purely round-robin Split/Join FSM                                   | 100 |

| 7.2 | Split and Join kernel FSMs for a (5 $\times$ 5) Output BufferKernel | 106 |

| 7.3 | Automatic parallelization examples                                  | 110 |

# List of Figures

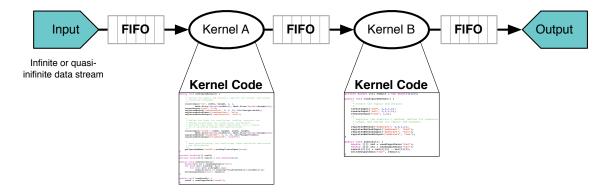

| 1.1 | Basic stream program example                                                            | 3  |

|-----|-----------------------------------------------------------------------------------------|----|

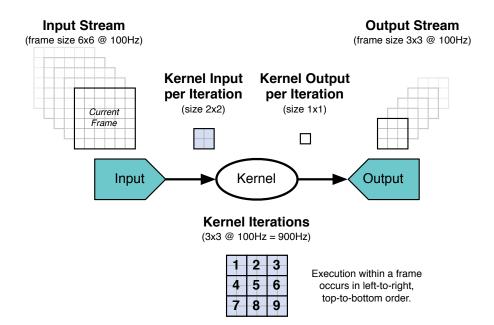

| 1.2 | 2D streaming application model example                                                  | 5  |

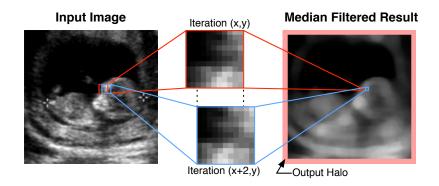

| 1.3 | Example median filter                                                                   | 6  |

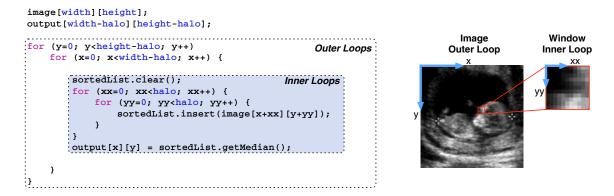

| 1.4 | Imperative (standard) median filter implementation $\ldots \ldots \ldots \ldots$        | 7  |

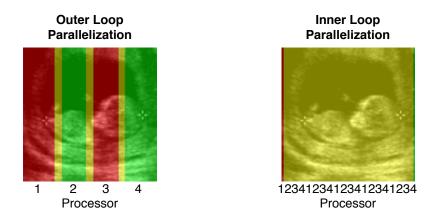

| 1.5 | Data distribution for inner- and outer-loop parallelization                             | 8  |

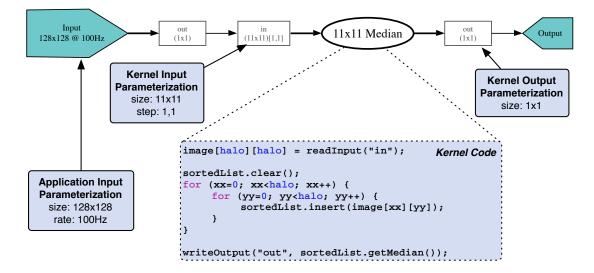

| 1.6 | Block-parallel median filter implementation                                             | 9  |

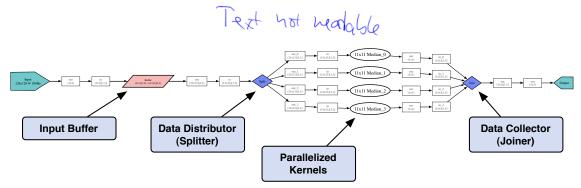

| 1.7 | Automatically parallelized block-parallel median filter implementation                  | 10 |

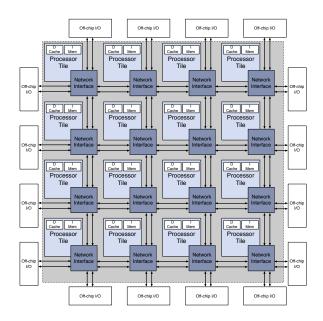

| 2.1 | Raw architecture                                                                        | 19 |

| 2.2 | Imagine architecture                                                                    | 20 |

| 3.1 | StreamIt supported hierarchical structures                                              | 25 |

| 3.2 | StreamIt FIR filter example                                                             | 27 |

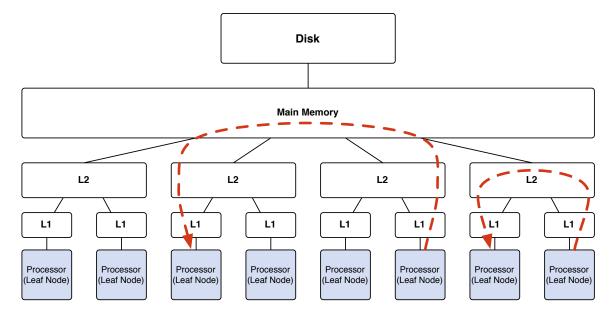

| 3.3 | Sequoia hierarchical memory model                                                       | 33 |

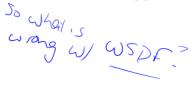

| 3.4 | Pavings in Array-OL                                                                     | 36 |

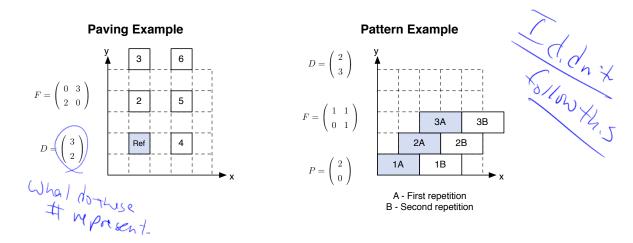

| 3.5 | Comparison of Related Work                                                              | 37 |

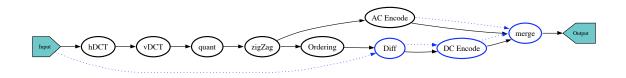

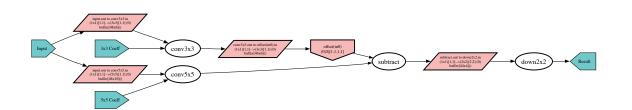

| 4.1 | Simplified application graph for JPEG compression                                       | 38 |

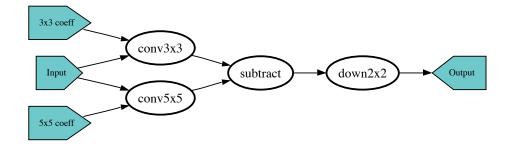

| 4.2 | Simplified application graph for a convolution program $\ldots \ldots \ldots$           | 41 |

| 4.3 | Simplified application graph for a differencing program $\ldots \ldots \ldots$          | 42 |

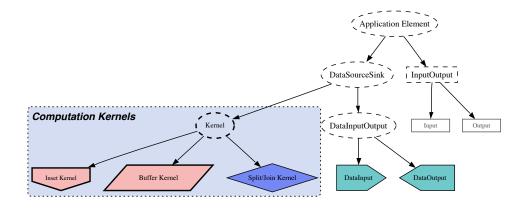

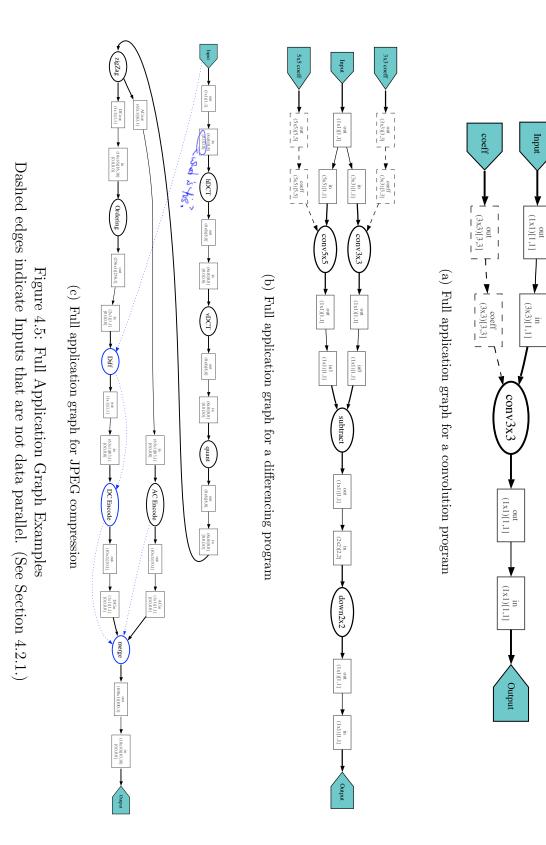

| 4.4 | Application element hierarchy                                                           | 43 |

| 4.5 | Full Application Graph Examples                                                         | 44 |

| 4.6 | Application graph code for a convolution program $\ldots \ldots \ldots \ldots$          | 45 |

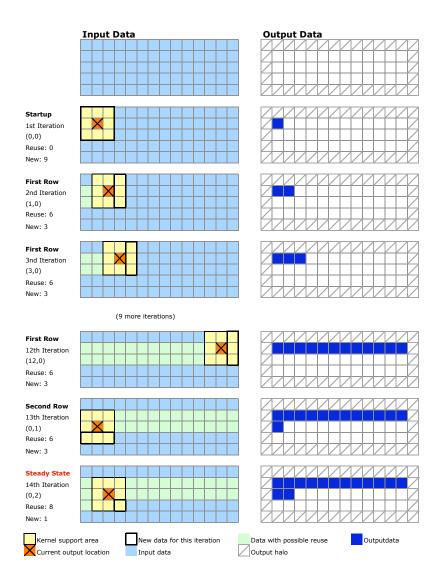

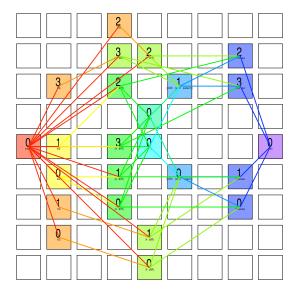

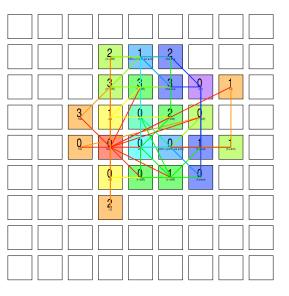

| 4.7 | Input data usage and reuse for a $3 \times 3$ convolution kernel $\ldots \ldots \ldots$ | 48 |

|     |                                                                                         |    |

| 4.8  | Comparison of native 2D stream access with 1D                                              | 9 |

|------|--------------------------------------------------------------------------------------------|---|

| 4.9  | Code for a simple subtraction kernel                                                       | 4 |

| 4.10 | Code for a convolution kernel                                                              | 6 |

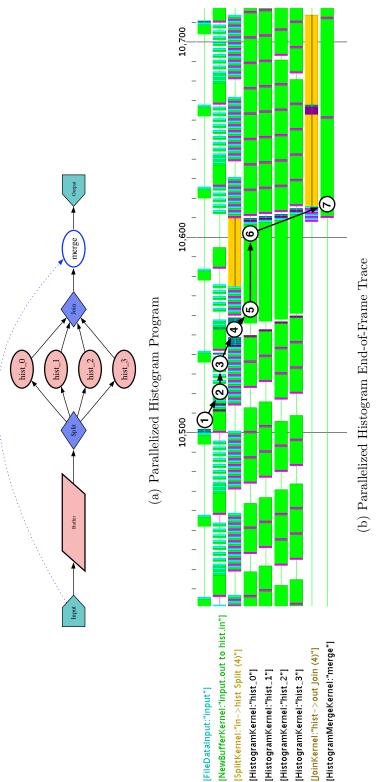

| 4.11 | Histogram application graph                                                                | 7 |

| 4.12 | Code for a histogram kernel                                                                | 8 |

| 4.13 | Parallelized Histogram Token Behavior                                                      | 9 |

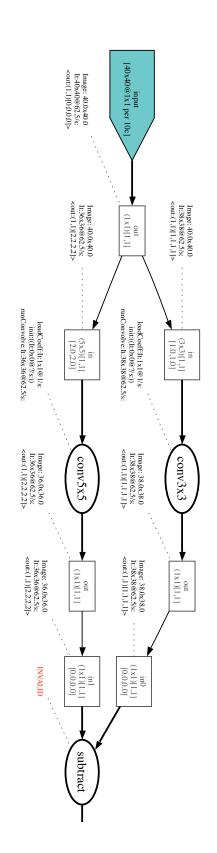

| 5.1  | Data flow analysis for the first half of the difference program 7                          | 2 |

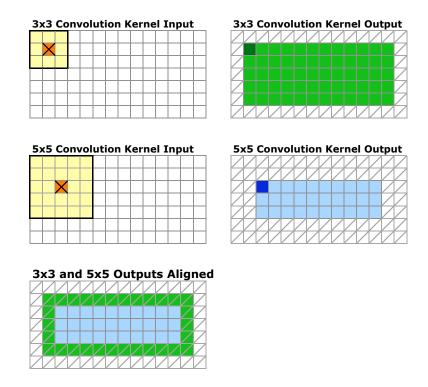

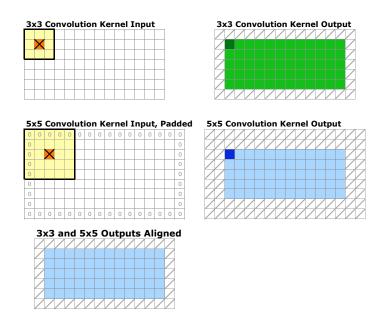

| 5.2  | Halo differences between 5x5 and 3x3 kernels                                               | 4 |

| 6.1  | Automatically buffered and corrected differencing program 7                                | 7 |

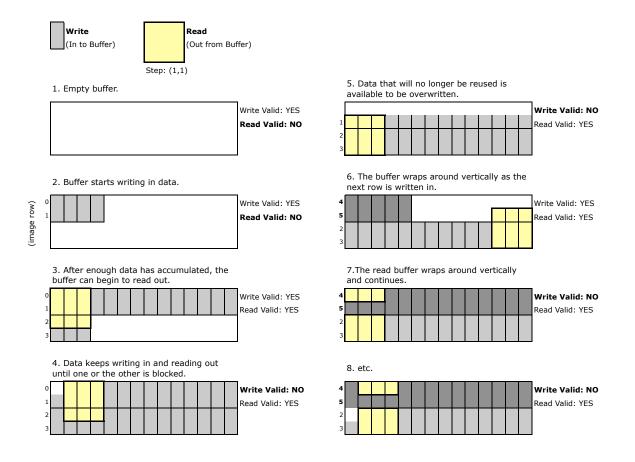

| 6.2  | Two-dimensional circular buffer operation                                                  | 9 |

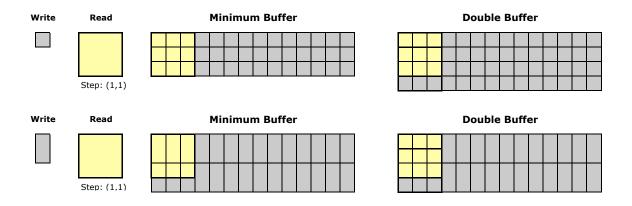

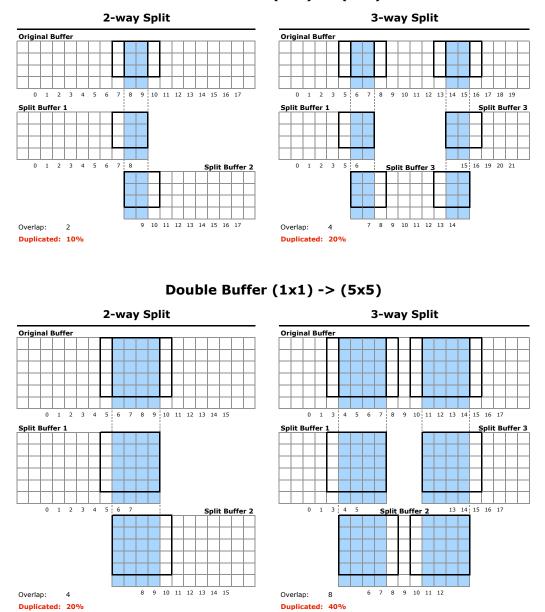

| 6.3  | Buffer sizes for double-buffering                                                          | 0 |

| 6.4  | Buffer sizes for double-buffering between frames                                           | 2 |

| 6.5  | Run loop for the BufferKernel    8                                                         | 4 |

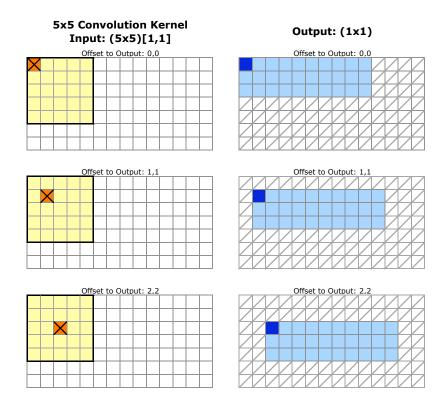

| 6.6  | Offset example for a $5 \times 5$ convolution kernel                                       | 7 |

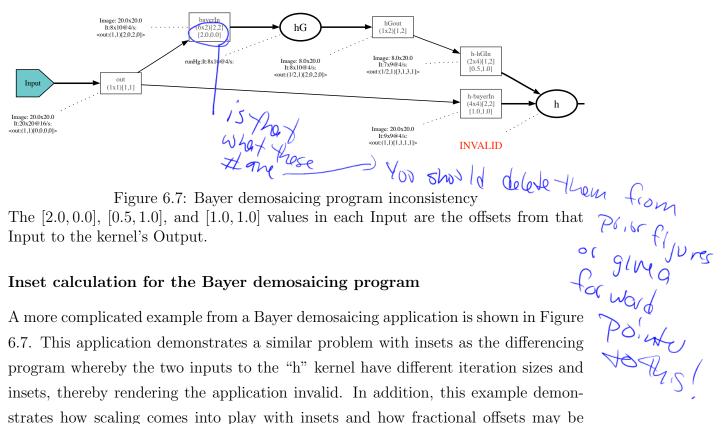

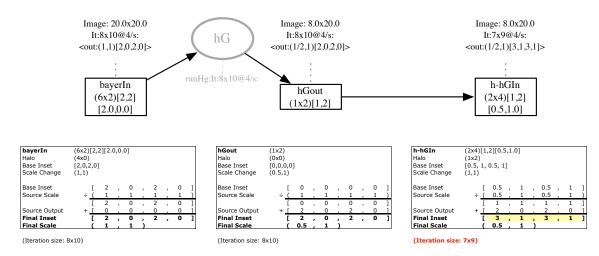

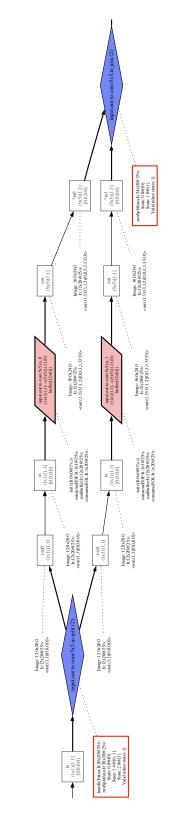

| 6.7  | Bayer demosaicing program inconsistency                                                    | 8 |

| 6.8  | Bayer "hG" kernel inset calculations $\ldots \ldots \ldots \ldots \ldots \ldots \ldots $ 8 | 9 |

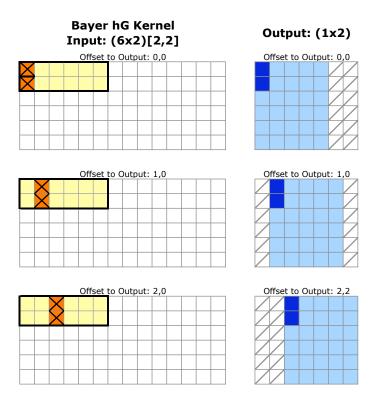

| 6.9  | Offset example for the Bayer hG kernel                                                     | 0 |

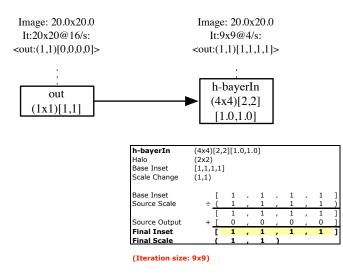

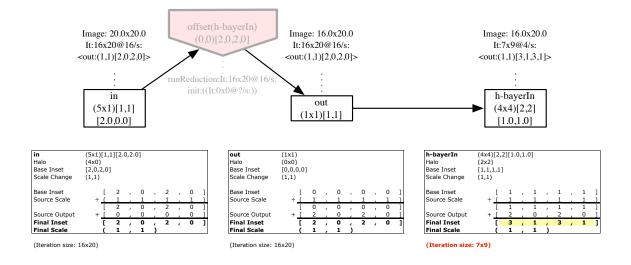

| 6.10 | Bayer "h-bayerIn" Input inset calculations                                                 | 1 |

| 6.11 | Bayer "h-bayerIn" Input inset calculations with appropriate InsetKernel 9                  | 2 |

| 6.12 | Adjusting insets by zero-padding inputs                                                    | 3 |

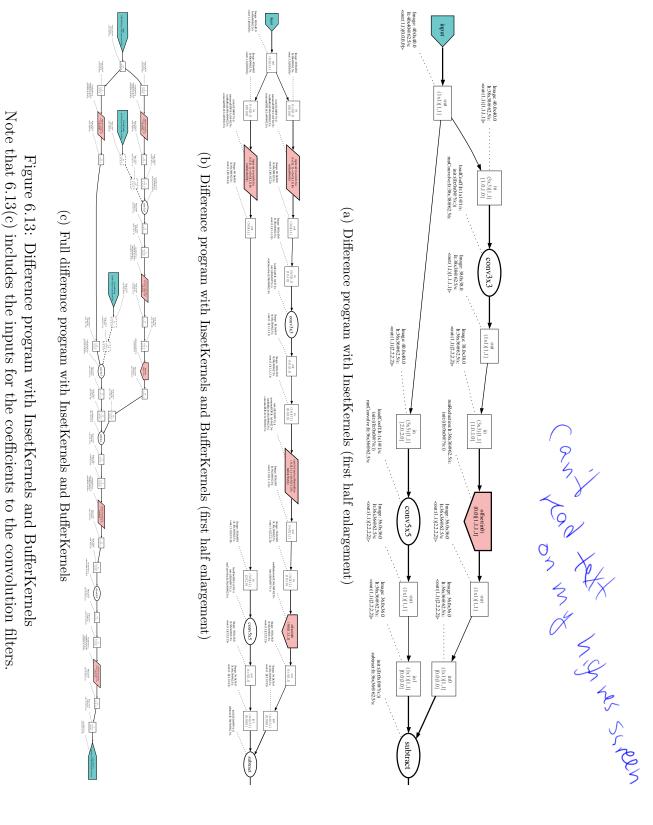

| 6.13 | Difference program with InsetKernels and BufferKernels 9                                   | 4 |

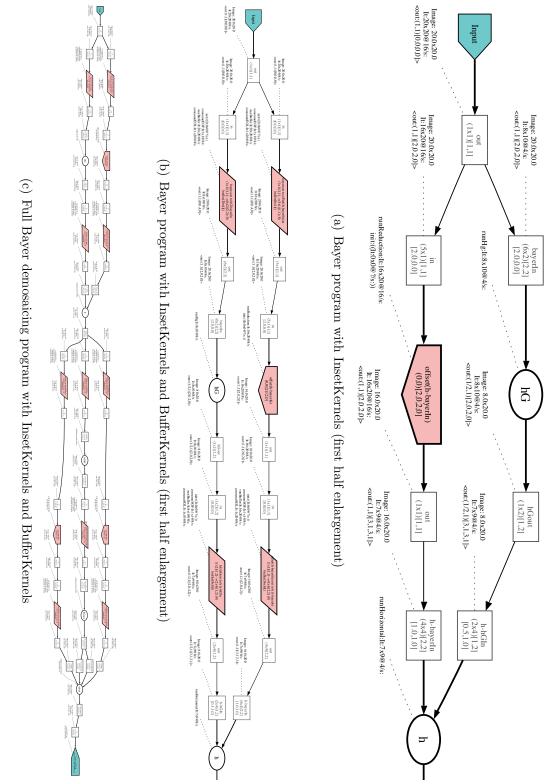

| 6.14 | Bayer program with InsetKernels and BufferKernels 9                                        | 6 |

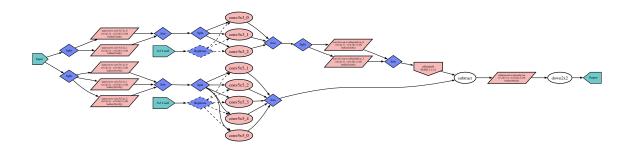

| 7.1  | Simplified application graph for a parallelized application 9                              | 8 |

| 7.2  | Round-robin parallelization of a convolution kernel 10                                     | 2 |

| 7.3  | Simplified parallelized histogram application with data dependency edge $\!10$             | 3 |

| 7.4  | Simplified parallelized JPEG application                                                   | 4 |

| 7.5  | Data replication for parallelization of BufferKernels                                      | 5 |

| 7.6  | Split/Join kernels for KernelBuffer parallelization                                        | 7 |

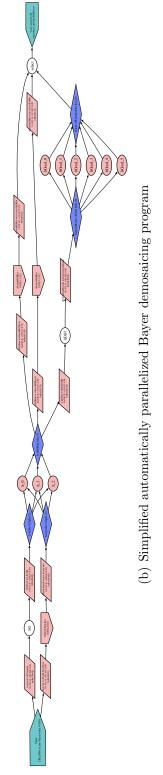

| 7.7  | Automatic parallelization examples                                                         | 9 |

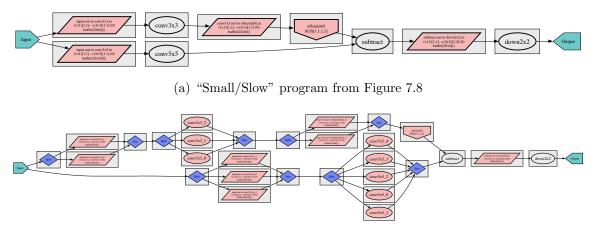

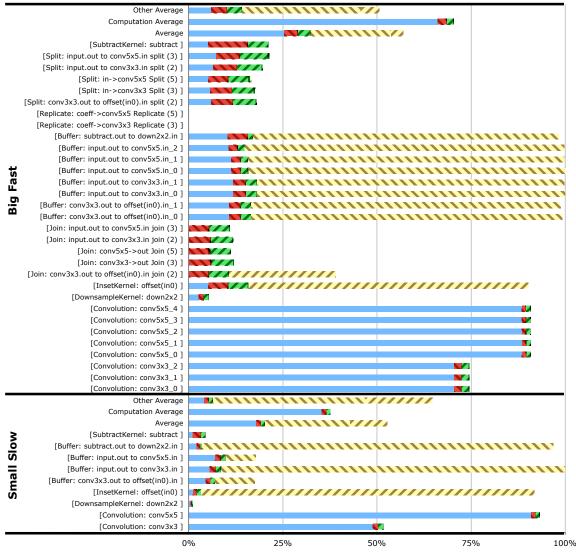

| 7.8  | Baseline differencing program ("Small/Slow")                                                         | 110  |

|------|------------------------------------------------------------------------------------------------------|------|

| 7.9  | Differencing program with increased input rate ("Small/Fast")                                        | 111  |

| 7.10 | Differencing program with increased input size ("Big/Slow") $\ldots$ .                               | 111  |

| 7.11 | Differencing program with increased input size and rate ("Big/Fast")                                 | 112  |

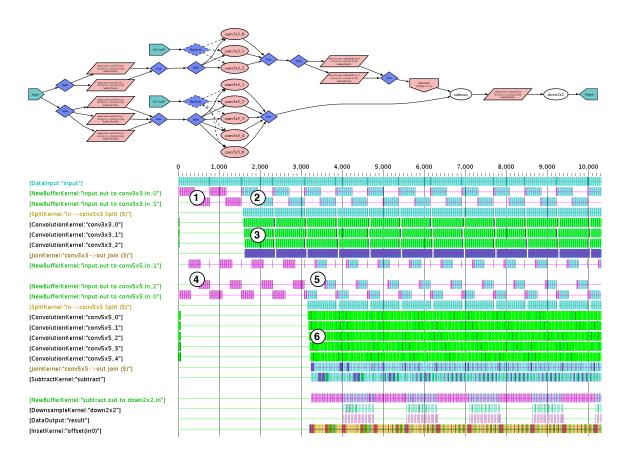

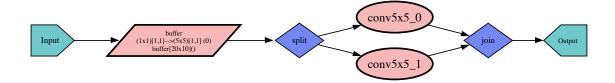

| 7.12 | Simple $5 \times 5$ convolution application graph $\ldots \ldots \ldots \ldots \ldots \ldots$        | 114  |

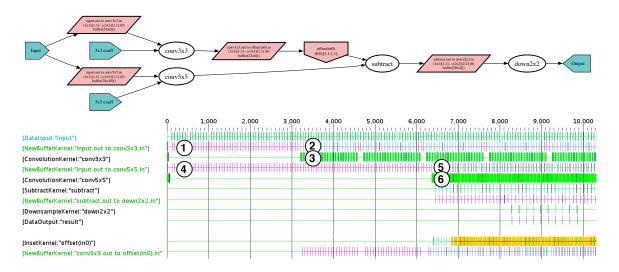

| 7.13 | Automatically buffered and parallelized simple $5 \times 5$ convolution program                      | n114 |

| 7.14 | Data reuse options for a $5 \times 5$ convolution $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 114  |

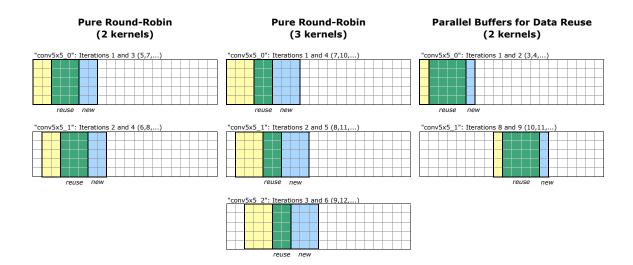

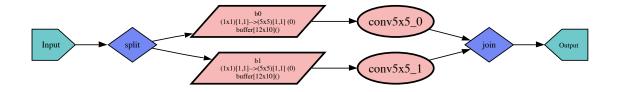

| 7.15 | Naïve buffer parallelization for reuse                                                               | 115  |

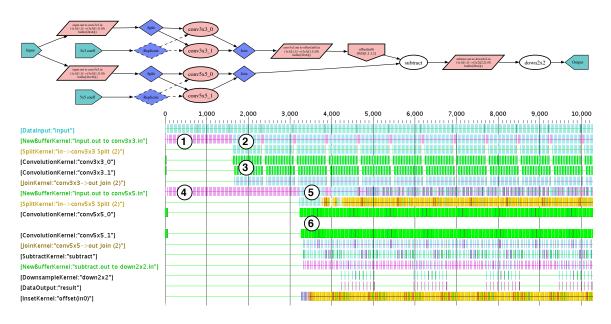

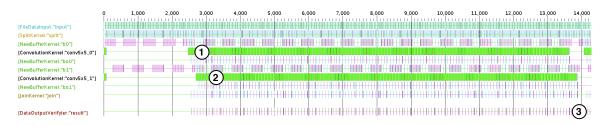

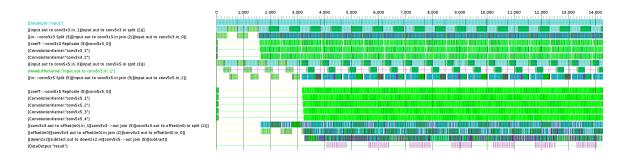

| 7.16 | Simulation trace of naïvely parallelized buffers                                                     | 115  |

| 7.17 | Correctly parallelized buffers for reuse                                                             | 117  |

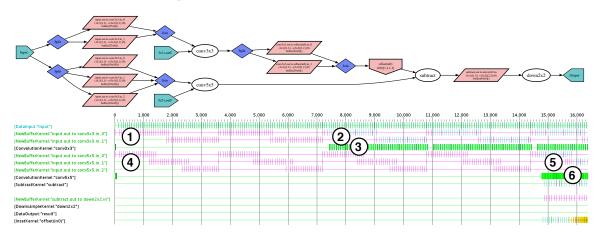

| 7.18 | Simulation trace of correctly parallelized buffers for reuse                                         | 117  |

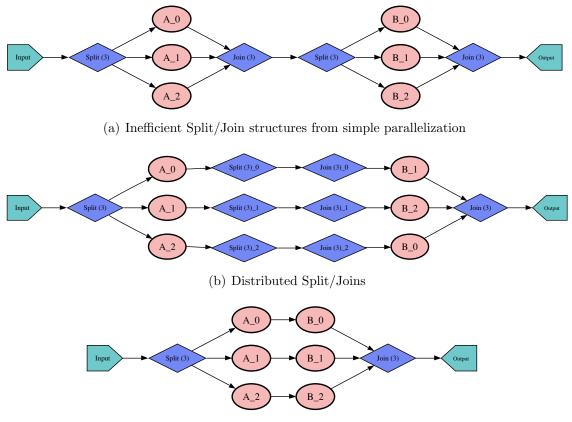

| 7.19 | Split/Join optimization examples                                                                     | 119  |

| 7.20 | Split/Join distribution and time-multiplexing                                                        | 120  |

| 8.1  | 1:1 kernel-to-processor mapping                                                                      | 124  |

| 8.2  | 1:1 mapping utilization                                                                              | 126  |

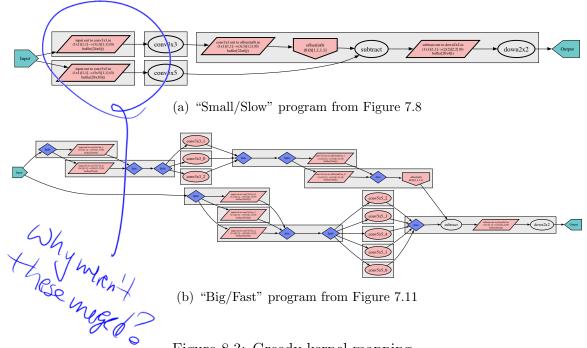

| 8.3  | Greedy kernel mapping                                                                                | 128  |

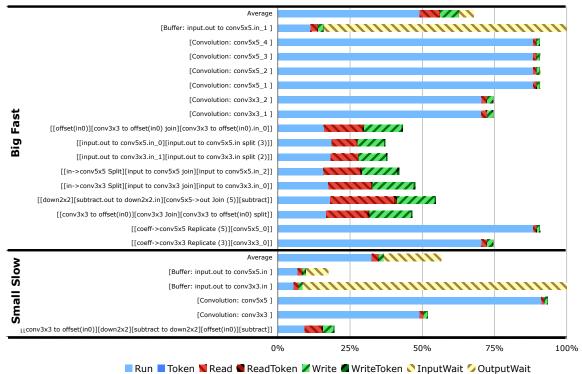

| 8.4  | Greedy mapping utilization                                                                           | 130  |

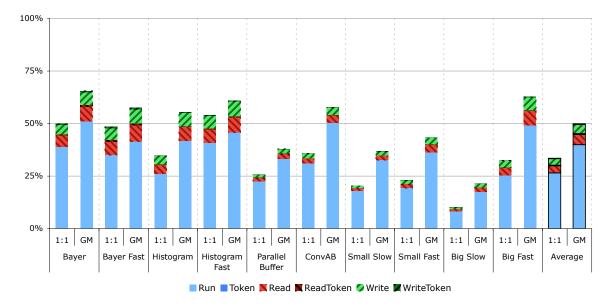

| 8.5  | Average utilization for naı̈ve (1:1) and greedy (GM) mappings $\ldots$                               | 131  |

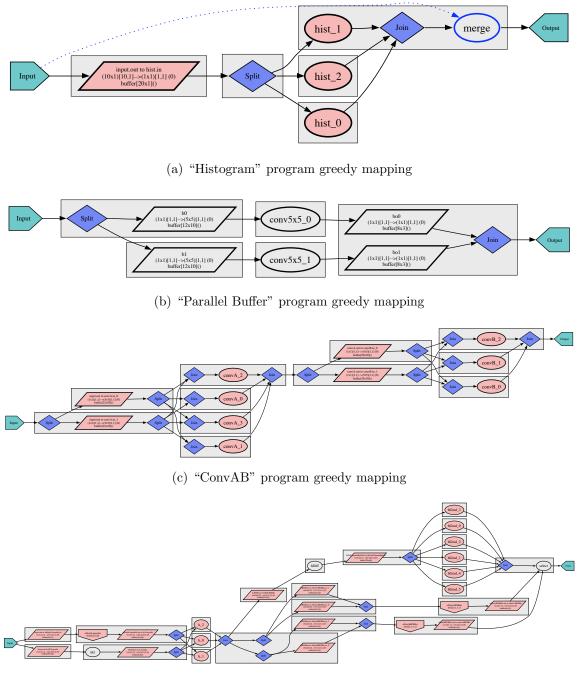

| 8.6  | More greedy kernel mappings                                                                          | 132  |

| 9.1  | Input: Simple program representation                                                                 | 137  |

| 9.2  | Input: Full parameterized program representation                                                     | 137  |

| 9.3  | Step 1: Partial data<br>flow analysis for inset/buffer insertion                                     | 138  |

| 9.4  | Step 2: Automatic insertion of buffers and insets for correctness $\ldots$ .                         | 138  |

| 9.5  | Step 3: Dataflow analysis for automatic parallelization                                              | 138  |

| 9.6  | Step 4: Automatic parallelization to meet real-time constraints                                      | 138  |

| 9.7  | Step 5: Automatic time-multiplexing to increase utilization                                          | 139  |

| 9.8  | Step 6: Simulated application execution                                                              | 139  |

| A.1  | Initial kernel placements for Bayer demosaicing before annealing                                     | 143  |

| A.2  | Final kernel placements for Bayer demosaicing after annealing                                        | 143  |

| A.3 | Initial JPEG kernel placements before annealing | 144 |

|-----|-------------------------------------------------|-----|

| A.4 | JPEG kernel placements after annealing          | 144 |

|     |                                                 |     |

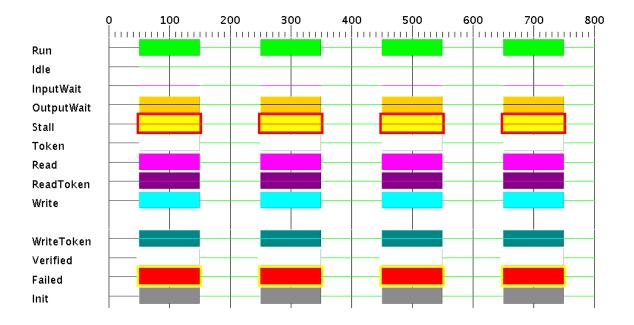

| B.1 | Bayer application with output verification      | 149 |

| B.2 | Simulation timeline viewer application          | 149 |

| B.3 | Simulation timeline key                         | 150 |

|     |                                                 |     |

| D.1 | Thesis writing progress                         | 156 |

## Chapter 1

### Introduction

### Peronally I don't like back to back headers. I think usually you should 1.1 Practical Block-parallel Programming have some

The goal of block-parallel programming is to provide a flexible structure for writing readily analyzable data-parallel applications that can be mapped to future processors with hundreds or thousands of computation cores. In addition to the traditional problem of identifying parallel computation within an application, to fully utilize these architectures the harder problem of mapping and scheduling data movement and staging across a distributed non-coherent memories needs to be addressed. The block-parallel programming approach presented here strives to provide a programming approach that exposes data movement and parallelism such that the compiler tool chain can easily manipulate the application and intelligently map it to the hardware. header.

Traditional imperative programming languages have proven very hard to analyze for automatic parallelization and data movement. The most successful automatically parallelizing compilers are only able to readily handle affine inner-loops with minimal control flow dependencies in (reasonably) well-typed languages. Attempts to analyze typical code in languages that allow arbitrary pointer access constructs, such as C, have proven enormously less successful.

However, despite many decades of research, even the most capable program analysis and manipulation frameworks run into the fundamental issue that even when they can analyze a program, it is not at all clear what manipulations should be applied

me

for optimal performance. The complexity of the code, combined with the number order of the possible non-commuting loop transformations leads to an extremely large search space. This search is made even more difficult by the discrete, and often nonmonotonic, performance results from varying the transformations, their parameters, and their orderings. The result is that most optimizing compilers are extremely conservative, optimizing only the innermost loop or two of purely affine programs or applying crude blocking to the outermost loops. For architectures with sufficiently low memory latencies or applications with sufficiently high arithmetic intensity this simplistic approach is acceptable. Unfortunately this approach has not been motivated by either of those artifacts per se, but rather by the difficulty of full-program analysis for complex architectures and applications. As architectures continue to become more distributed and less coherent due to scaling difficulties (e.g., they look less and less like a traditional von Neumann architectures), successful parallelization approaches will need to be based on more structured inputs to the compiler.

This difficulty of analyzing traditional imperative programming languages motivates the need to provide programming approaches that are easier to analyze. Streambased programming in general, and the block-parallel programming presented here, in particular, attempt to address this issue. These approaches take advantage of the way programmers tend to naturally think about decomposing algorithms, by structuring applications as graphs of computation kernels and data streams. This provides the compiler with a high-level view of the data movement and parallelism present in the application without the complex analysis required for imperative languages. However, for this approach to be successful, it must provide a simple enough interface for the programmer to make it productive. Previous stream-based programming systems have presented programmers with very awkward methods for dealing control between kernels and two-dimensional data streams.

The block-parallel application model presented here strives to allow programmers to intuitively specify applications as a graph of parameterized kernels connected by two-dimensional data and control streams. In this approach, the kernels and streams are parameterized to enable analysis by the compilation system for automatic parallelization, data movement, and placement on an array of processors.

Can q pogramy Ve alin?

what is this?

#### 1.1.1 The 2D Streaming Model

Stream programming systems, such as Brook [7], StreamIt [43], StreamC/KernelC [36], and a variety of Synchronous Data Flow (SDF) [33] approaches, treat their inputs as infinite or quasi-infinite streams of data. The computation kernels that act on these streams specify the number of stream elements they need to execute, and the number of iterations of execution is implicitly defined by the length of the stream divided by the number of unique elements required per execution. The computation kernels are connected together and to inputs and outputs by channels which act as FIFOs for the stream data. This programming model maps well to application domains where the input is generated and processed continuously, and where reuse of the data is largely local in both time and space. Applications such as media and signal processing are prime examples of this domain. Thies [43] describes such applications as having six salient characteristics: 1) large streams of data, 2) independent stream computation kernels, 3) a stable computation pattern, 4) only occasional modification of stream structure, 5) only occasional out-of-stream communication, and 6) high performance expectations.

Figure 1.1: Basic stream program example

The kernel code for each kernel is logically executed on the incoming data whenever enough data arrives. The kernel then produces output data which is sent downstream via the FIFOs between kernels.

The execution flow of a stream program is defined by connecting multiple kernels together in a directed graph that represents the desired flow of data through the computation kernels. To apply kernel "A" to an input stream, the stream would be connected to the input on kernel "A". To then apply kernel "B" to the result, the output of kernel "A" would then be connected to the input of kernel "B". Such a toy application is illustrated in Figure 1.1. This programming style closely matches signal and image processing problems where algorithms tend to be designed by applying reusable computation kernels to data streams.

Most streaming systems define their data streams as one-dimensional series of data, although there have been multiple proposals for multi-dimensional streaming [33, 27, 4] and blocking [15] languages. Despite this one-dimensional limitation, they can handle higher dimensional data by appropriately (and usually manually) indexing into the single-dimensional streams. This enables image and video processing within the same framework without explicit two-dimensional data support. However, this approach complicates the program analysis by hiding the underlying program structure, and requires that the programmer keep track of the particular data layout throughout the application. The approach taken in this work is to provide a native two-dimensional data stream to simplify writing and analyzing programs that manipulate two-dimensional data. (See Figure 1.2.) Like other streaming systems, the two-dimensional stream consists conceptually of an infinite number of elements, but unlike one-dimensional approaches, each element in the stream is a two-dimensional data frame. While the number of frames is assumed infinite (such as might be found in a video stream), each frame itself is of a fixed, and statically determined, size. The data within each input frame is further assumed to stream into the application, in a left-to-right, top-to-bottom manner. One-dimensional streaming applications can be readily written by simply defining the streams to be height one.

To take advantage of the two-dimensional input streams, the computation kernels that operate on them are also defined with two-dimensional inputs and outputs. This parameterization greatly simplifies the programming system's job of analyzing how the data is used and reused for applications that map nicely to one- or two-dimensional inputs. For one-dimensional streaming systems, this two-dimensional information must be inferred from the use of the streams within the kernels, and can only be utilized if the inferences can be proven to hold throughout the application. The

Figure 1.2: 2D streaming application model example

The input stream is depicted on the left. The stream consists of frames of size  $6 \times 6$  which are processed through the kernel shown in the middle. The kernel's input is  $2 \times 2$ , which tiles the input frame size  $3 \times 3$  times, producing an output of size  $3 \times 3$ , which defines the output stream.

manipulations enabled by explicit two-dimensional parameterization include reuse calculation, buffer sizing and partitioning, and application consistency analysis. With this enhanced knowledge of the data usage patterns of the application, it is readily possible to parallelize and map the application to an array of processors to meet a specified data rate without heroic compiler analysis.

#### **1.1.2 Block Programming Example**

To motivate this programming approach, consider applying a median filter (Figure 1.3) to an input image. The goal is to provide an automatic system for parallelizing this filter to meet the real-time constraint imposed by the input image's size and rate.

A median filter processes the input image in overlapping windows, sorting the pixel values in each window, and outputting the median value for the window at each pixel

Figure 1.3: Example median filter

The application of a median filter to an input image is shown. The input windows and output pixels for two iterations of the filter are shown in red and blue. The input windows overlap as can be seen from the alignment of the two filter input windows shown in the middle. The output image is surrounded by a halo of invalid data that must be either removed or generated by zero-padding the original input image.

location. The straight-line imperative code for the median filter, as shown in Figure 1.4, is quite straightforward. It consists of four sets of nested loops: two outer loops for walking over the image to choose the window, and two inner loops for walking over the window to calculate the median value. For a compiler to automatically analyze and parallelize this code to meet a given data rate, it needs to be able to analyze this loop nest. However, the code within the inner two loops has data-dependent behavior. That is, the sorting of the values to calculate the median can not be statically predicted, and therefore can not be statically analyzed. This limits the compiler analysis to examining the outer two loops.

The two outer loops in this code are very straightforward, and can be readily understood and parallelized with a basic affine analysis<sup>1</sup>. Unfortunately, examining just the outer two loops is insufficient in this case. The median filter processes data in windows that overlap between iterations, with the size of these windows and the overlap being defined by the data access patterns in the inner loops. This means that any parallelization needs to calculate this overlap by examining the range of

<sup>&</sup>lt;sup>1</sup>Note that while this analysis is "understood" in the academic sense, no common compiler is actually advanced enough to implement it.

Figure 1.4: Imperative (standard) median filter implementation

The imperative code for a median filter consists of two *outer loops* for walking over the input image and two *inner loops* for walking over the window at each location. The pixels in the window to be processed are sorted and the result is the median value of that sorted list.

data accessed in the inner two loops for each execution of the outer two loops, and duplicate this data accordingly.

This analysis leaves the compiler with the choice of parallelizing along either of the two outer loops, with the inner loop code being executed for each iteration. The choice of which to use is driven by an analysis of the data reuse enabled by each approach when loading the input image from off-chip memory. (See Figure 1.5.) If the parallelization splits along the outermost loop, the result will be poor data locality as each processor will be accessing data for a separate portion of the input image simultaneously. Without appropriate banking of the memory system and careful data layout this will result in poor performance. If the parallelization splits along the innermost loop, each processor will be reloading the same data its neighbor requested recently, which will significantly increase the total traffic in the absence of a higher-level cache. These problems are a result of the interplay of the parallelization and data access patterns of the underlying code, something which is poorly exposed through the code analysis, and which is even harder to reason about even if it is exposed. Unfortunately this is likely to be the performance dominating feature of the analysis, particularly for many-core architectures where on-chip data movement must be carefully coordinated due to a paucity of off-chip bandwidth.

Figure 1.5: Data distribution for inner- and outer-loop parallelization

The portion of the image filtered by each processor is shown alternatingly in red and green, with shared data is shown in yellow. Outer-loop parallelization divides up the image into vertical slices which are accessed at the same time by each processor, causing a stream of non-sequential external memory requests. Inner-loop parallelization causes each processor to process sequential blocks, which results in each processor generating memory accesses for the same data that the previous processor requested on the previous iteration.

To determine the degree of parallelization required, the compiler needs to know two things: the size and rate of the input image, and the amount of time each iteration of the filter takes. The processing time per iteration depends on how the compiler chooses to parallelize the code, but, if we assume for simplicity that the compiler treats the inner two loops as the unit of computation, the processing time can be reasonably approximated by a static analysis or with some help from the programmer. The input rate is specified no where in the code, and must be provided externally or through a custom pragma to the compiler.

The block-parallel programming approach presented here greatly simplifies this analysis by parameterizing the application in two ways. The first is that the computation is expressed as a graph of computation kernels with parameterized inputs and outputs. The second is to define an order of iterating over input data. Taken together, these eliminate the inner loop analysis (via kernel parameterization) and outer loop analysis (via an explicit data iteration order) required to manipulate the

Figure 1.6: Block-parallel median filter implementation

The block-parallel median filter implementation defines a median filter kernel which contains the code to execute on each iteration. The kernel also defines the input window size it requires and the output data size. The program image input size and rate are specified by the input "Input" on the left.

median filter presented above. The tradeoff is that the programmer must now provide the data derived by the above analysis, but as the programmer has intimate knowledge of both the domain and the filter being implemented, this is a relatively low-cost requirement.

Indeed, the information the programmer must provide actually simplifies the application development and encourages code reuse. For the median filter, shown in Figure 1.6, the programmer needs to specify that the input window size is (width  $\times$  height) and that this window steps through the input in (1,1) steps for each horizontal and vertical iteration, respectively. Taken together these define how much data the median filter needs for each iteration, and how much reuse and overlap is present in the computation. The output is similarly simply defined as being size (1 × 1). The kernel must finally specify the amount of computation required per iteration, which is just as easily calculated for the kernel implementation as for the straight-code imperative implementation. When the full block-parallel application is written, the input

Figure 1.7: Automatically parallelized block-parallel median filter implementation

size and rate are explicitly defined by the parameterization of the input connected to the kernel, and therefore no special pragmas are required to pass on this information.

With this information, the compiler can avoid all of the analysis described above. The addition of a fixed input data ordering (here left-to-right, scanline order), simplifies the compiler's decision as to how to parallelize the processing, as well. (See Figure 1.7.) By specifying the input data ordering, the compiler can determine the parallelization so as to maximize reuse within the input data, thereby minimizing access to off-chip memory. The result is that the parallelization analysis need merely determine how many kernels are required ( $\frac{inputRate \times inputSize}{timePerKernelIteration}$ ) and then send the data in a round-robin fashion to that many separate instances of the kernel on different processors. The compiler can insert a buffer to store the incoming data in the known input order to insure that the processors obtain maximum reuse and bandwidth to the off-chip memory.

The downside of this approach is that the compiler is left with less flexibility in determining the parallelization, and the programmer is forced to make the programs conform to the kernel/stream programming model. However, with the language features discussed in this thesis the difficulty of writing traditionally non-data-parallel applications in a streaming language can be significantly reduced, and the losses from a more constrained parallelization program are readily compensated for by the ability

The block-parallel median filter implementation enables the automatic buffer insertion and parallelization shown here. The median kernel has been replicated four times and appropriate data distribution and collection (Split/Join) kernels and an input buffer have been inserted.

to robustly and efficiently parallelize a general, and useful, class of programs.

### **1.2** Contributions

This thesis describes a block-parallel streaming programming approach and the associated analyses and application transformations required to automatically parallelize such applications to meet hard real-time constraints. The specific contributions of this work are as follows:

- A practical two-dimensional "block-parallel" streaming language whose programs are described as an application graph with data streams connecting computation kernels. Each kernel supports multiple inputs and outputs and multiple computation methods.

- A compiler system that can automatically parallelize the block-parallel application to meet real-time constraints. The constraints are defined by the size and rate of the application's inputs, which are propagated through the application graph by a dataflow analysis. This analysis enables the compiler to determine the required computation rates, and hence degree of parallelization, at each point in the application. The regular streaming structure of the program then enables automatic parallelization to meet these constraints.

- A cycle-accurate functional simulator for evaluating the performance of the parallelized applications that uses the same program code as the compiler, but avoids the need to implement a hardware simulator.

- Analyses to determine the need to inset or zero-pad data to fix inconsistencies in the intuitive description of two-dimensional streaming applications, thereby improving the reusability of code.

- A method for describing the distribution of control tokens which is both analyzable and flexible. By including the control tokens in the application analysis, the overhead of non-trivial control handling code can be accurately incorporated in the performance estimation.

- The use of multiple methods per kernel which can be independently triggered by incoming data or control to simplify application structure and data sharing. Combined with the flexibility of the control tokens, this allows powerful multiplexing of control and data over a single logical input to a kernel.

- The use of data dependency edges in the application graph to intuitively and flexibly limit the degree of parallelism allowed for certain computations.

- Automatic sizing and insertion of two-dimensional circular buffers between kernels.

### 1.3 Thesis Overview

This thesis describes a block-parallel programing and compilation system and provides examples of the transformations and analyses needed to map applications to many-core architectures. The thesis begins with an overview of relevant background material in Chapter 2. This includes an introduction to Synchronous Data Flow (SDF) application descriptions and current streaming hardware architectures. SDF is important as it has formed much of the basis for stream-kernel programming, and is the only approach that has produced a decent mathematical formulation for analyzing the application structure.

Next an overview of related work is presented in Chapter 3, with a focus on a variety of relevant streaming languages, including StreamIt (Section 3.1.1), StreamC/KernelC (Section 3.1.2), Brook (Section 3.1.3), Sequoia (Section 3.1.4), and multi-dimensional SDF (Section 3.2). Particular detail is paid to the StreamIt language as it is one of the most developed implementations.

With this background, the programming model for the block-parallel programming system is presented in Chapter 4. The *Application Graph* used to describe the overall application and data flow is introduced in Section 4.1. The details of the *Data Model*, including data streams, data transport, and control are described in Section 4.2. This is followed by a description of the *Computation Model* in Section 4.3, and several

examples in Section 4.4. The chapter concludes with a discussion comparing the model presented here with the other languages discussed in Chapter 3.

After having established the basic application description framework in Chapter 4, Chapter 5 describes the analysis required to determine the computation rates of the various kernels in the application. The salient values, *frame size*, *frame rate*, and *iteration size*, are introduced and defined in Section 5.1, and the data flow analysis required to calculate them is described in Section 5.2. The chapter concludes with a brief discussion of feedback (Section 5.2.1) and an example detailing the application of the described data flow analysis (Section 5.3). The example reveals two types of *application inconsistencies* in the sample application which are to be addressed in Chapter 6.

Chapter 6 starts where Chapter 5 ends by addressing the aforementioned application inconsistencies. Their causes are explained, and the need to insert buffers and insets to correct them is discussed. Section 6.1 describes the two-dimensional circular buffers required for buffering a two-dimensional streaming application, and derives the sizing needed for minimal and double-buffering, with particular care paid to buffering between input frames. The implementation of the buffers as *BufferKernels* is presented in Section 6.1.2. Insets, the extended data flow analysis required to calculate them, and their implementation as *InsetKernels* are presented in Section 6.2. Two detailed examples are also provided to demonstrate the analysis. An alternative to inset insertion, zero padding, is discussed in in Section 6.2.2. The chapter concludes with a description of the automated insertion of buffers and insets to create complete and consistent applications.

Chapter 7 takes the complete and consistent applications from the automatic analysis in Chatper 6 and adds automatic parallelization to meet the required data rates of the application's inputs. To implement the parallelization, Section 7.1 introduces *Split* and *Join* kernels to allow flexible data distribution to parallelized kernels. The remainder of the chapter discusses the issues involved with parallelizing purely dataparallel kernels (Section 7.2), kernels with limited parallelism (Section 7.3) and finally BufferKernels (Section 7.4), whose parallelism is defined by the order in which data must be written into them. Examples of parallelized applications showing the automatic analysis and adjustment for both application data input rates and processor capabilities are shown in Section 7.5, and the chapter concludes with discussions of data reuse from parallelized buffer kernels (Section 7.6.1), the inefficiencies of Split/Join kernels (Section 7.6.2), and a comparison to related work.

The automatic parallelization of Chapter 7 implies a naïve 1:1 mapping of kernels to processors, which results in a low overall utilization. Chapter 8 addresses this by first analyzing the utilization of the 1:1 mapping (Section 8.1) and then proposing a simple greedy merging algorithm for time-multiplexing the kernels to achieve better utilization (Section 8.2). The greedy merge algorithm is implemented and the final full analysis, buffering, parallelization, and time-multiplexing is evaluated across a range of programs (Section 8.3).

The thesis concludes in Chapter 9 by discussing the overall merits of the proposed block-parallel programming system and the analyses discussed herein. Three appendices briefly touch upon using simulated annealing for kernel placement on an array of processors (Appendix A), the simulator implementation developed for this analysis (Appendix B), and future directions of interest for this system (Appendix C).

## Chapter 2

### Background

This background section covers two topics: a formal framework for describing and analyzing kernel-based applications known as Synchronous Data Flow, and an overview of current streaming processor hardware implementations.

### 2.1 Synchronous Data Flow

The concept of data flow programming has been elegantly codified into the Synchronous Data Flow (SDF) application descriptions [34]. SDF originated from the desire to map signal processing algorithms to DSPs efficiently, and as such focuses on the static scheduling of computation kernels (actors) operating on streams of data (tokens). The SDF description builds an application from a graph of actors with statically determined token consumption and production rates. The actors are connected by a directed graph edges, or FIFOs, which can optionally specify delays. By insisting on static data rates, the application can be analyzed to determine the optimal schedule for firing (executing) the actors to minimize buffering and scheduling overhead, while avoiding deadlock. The application definition is quite general, allowing multiple inputs and outputs to actors and feedback loops within the application.

SDF applications can be analyzed by putting the static production and consumption rates of each actor on each edge into a *topology matrix*. The topology matrix can then be manipulated to determine a *static* Periodic Admissible Serial Schedule (PASS) for the application. Such a schedule defines a repeating firing pattern for all the actors in the graph that guarantees that the size of the buffers between each actor does not increase between iterations. The PASS thereby defines the maximum buffer sizes required along each edge within the graph. The derivation and proof of such a schedule reveal several nice properties of this description of the application including proof of the existence of such a schedule and the requirements for a consistent application description. The initial work on SDF also introduced a reasonable methodology for generating parallel schedules and acknowledged the possibility of trading off schedule length for buffer size. The limitations of the SDF model are in its static nature. By itself it can not handle state changes or data dependencies in the structure of the application.

To enable applications with state dependencies, SDF has been extended to encompass a Cyclo-static Dataflow (CSDF) approach [14]. This approach allows each actor in the graph to have a cyclical sequence of statically defined production and consumption rates. The application can then be analyzed much like a regular SDF application by expanding the topology matrix to contain vectors representing the possible firing states for each actor. The resulting static schedules are necessarily much longer than the regular SDF ones as they must encompass the correct number of internal cycles for each of the actors.

CSDF applications can also be translated into SDF form [39]. Such a translation has the advantage of allowing the use of methods for scheduling and analyzing the simpler SDF graphs, but has the potential cost of exponential schedule growth. If the CSDF model is explicit as to which actors have internal state, the transformation to SDF can expose additional parallelism that would not have been present in a purely CSDF representation. The overall increase in flexibility provided by allowing each actor to have an internal cyclical consumption/production pattern makes SDF significantly more general, but greatly (indeed, sometimes exponentially) increases the complexity of scheduling and analysis.

Subsequent work on generating schedules for SDF applications focused on minimizing the memory resident sizes of the resulting applications, as reviewed in [6].

Across a range of applications targeted at DSPs, the size of the code for the compiled SDF applications was found to dominate over the required buffering between the actors due to the need to inline the actor code to avoid the historic overhead of function calls. This led to several approaches to generate minimum sized schedules by focusing on obtaining Single Appearance Schedules (SASS) wherein each actor's code need only be inlined once. SAS schedules exist in general only when each strongly connected component of a SDF graph itself has a valid SAS schedule. This leads to algorithms which partition graphs into strongly connected (tightly interdependent) components, for which an SAS schedule can not necessarily be found, and "subindependent" components for which one can. To obtain decent schedules for the tightly interdependent components, the SDF graph must be ordered in such a way that each actor can be fired the correct number of times in a row without stalling, if possible. Two heuristics for finding such an ordering are Acyclical Pairwise Grouping of Adjacent Nodes (APGAN) and Recursive Partitioning by Minimum Cuts (RPMC). These two approaches complement each other in that they work well on different types of graphs, and generally construct SAS schedules for acyclic SDF graphs that minimize the buffer sizes required, and have been extended to cyclic graphs.

While SAS schedules produce the smallest inlined code for SDF applications, the justification such code-size reduction efforts has diminished over time. The drive for SAS schedules was based on the need to inline all actor code to avoid the overhead of function calls and dynamic dispatch. As caches have become larger and ubiquitous on even the smallest DSPs, and as many-core processors lead to communications being the dominant performance concern, dynamic scheduling and dispatch of actors is rapidly becoming a small, or even negligible, overhead [48]. As much of the work in SDF in general has focused on obtaining optimal *static* schedules for DSPs, it is not clear how valuable this model will be moving forward.

### 2.2 Streaming architectures

Streaming architectures have arisen in response to the growing disconnect between the amount of computational resources that can fit onto a chip and the amount of off-chip bandwidth available to feed them. At the same time, a push towards multi-core architectures has been seen due to the increasing power cost and decreasing performance benefits of trying to extract dynamic parallelism from a single instruction stream. Combined, these two trends lead to a range of architectures that feature multiple software-controlled processing units and explicit software-controlled data movement. The most relevant academic projects in this regard are MIT's Raw [45] and Stanford's Imagine [40] architectures. In industry, the IBM-Sony-Toshiba Cell processor [21], Stream Processor's Storm-1 [29], a broad range of graphics processors, and a healthy collection of special-purpose embedded architectures are making commercial stream processing a reality.

#### 2.2.1 MIT's Raw

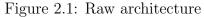

The Raw microprocessor architecture [45, 42] was designed to implement the minimum set of features in hardware to expose the hardware resources to the compiler. The driving motivation was that as devices become smaller wire delays become more expensive and the opportunities for parallelism and specialization increase. This led to a tiled architecture that exposed the logic (functional units in each tile), wires (on-chip networks), and I/O pins (via the chip edge network ports) at the ISA level to allow the compilation system to make best use of the resources. By exposing this level of architectural detail to the compiler, the Raw project aimed to enable a broad range of applications to execute efficiently and scale well.

The Raw implementation consists of an array of identical tiles, each containing a MIPS-like 8-stage, in-order, single-issue pipelined processor and a network interface. The network interface supports four networks: two static and two dynamic. To encourage the use of multiple tiles to exploit ILP, the networks are mapped directly into the register files in the processors. This enables a static route to communicate register values between functional units in adjacent processors in only 3 cycles. The dynamic networks are divided into a privileged network for cache, DMA, and I/O access, and a general purpose network. The processors contain simple floating point

units, 32kB of data cache, and 32kB of software-managed instruction memory,<sup>1</sup> while the network interfaces contains 64kB of instruction memory, thereby enabling great flexibility in the scheduling of the static networks.<sup>2</sup> To enable software control of the I/O resources, the on-chip networks are simply routed to the I/O pins, and can thereby be accessed with regular network commands.

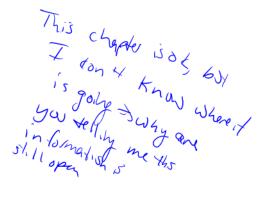

#### 2.2.2 Stanford's Imagine

The Imagine streaming architecture [40] was designed to execute media processing kernels with high arithmetic intensity efficiently [28]. The focus was on providing a good hardware match for both the instruction- and data-level parallelism present in

$<sup>^2 \</sup>mathrm{Unfortunately},$  this flexibility in the network router resulted in them being roughly as large as the processor itself.

The Raw architecture consists of an array of 16 tiles, each with a RISC processor and network interface. The processors have data caches and software-controlled instruction/scratchpad memories. The network interfaces terminate in I/Os at the edge of the chip.

$<sup>^{1}</sup>$ It appears that not including an instruction cache was a significant issue for development as almost all reported results are run on a simulator with an instruction cache.

media applications, while improving memory system efficiency by restricting access semantics to regularly indexed streams. For applications that map to this architecture, it was able to achieve very high utilization and efficiency.

Figure 2.2: Imagine architecture

The streaming register file (SRF) provides a data staging area and bandwidth multiplication between the off-chip memory and the VLIW processing lanes. Figure after from [40], Figure 3.

Imagine executes SIMD-style across 8 VLIW computation "lanes". Each VLIW lane is designed to take advantage of the ILP present in the kernel. Data-level parallelism is exploited by having 8 lanes operate together in a SIMD-manner. The architecture functions as a streaming co-procesor and relies on a host CPU to load stream memory instructions and kernels to a small hardware scoreboard. Imagine then issues the memory instructions and kernels when their scoreboard dependencies have been satisfied, executing up to two stream memory instructions and one kernel instruction at a time.

Streams are loaded from off-chip memory into an on-chip streaming register file (SRF) which provides high-bandwidth regular data access to the computation units. The computation kernels are executed by an on-board micro-controller that issues instructions across the 8 VLIW lanes in a SIMD fashion with each lane receiving the *n*-th data element from the data stream(s) and writing out the *n*-th result. The SRF is the only global memory structure accessible by the computation kernels, and it can only be accessed in either strided or indexed fashion. This access-pattern restriction enables the memory sub-system to efficiently use its bandwidth by pre-fetching data for the processing lanes. In addition to accessing the SRF, each lane can read and write scalar control variables to the micro-controller. Inter-lane communications is provided by an exchange instruction which allows the lanes to rotate data in an arbitrary, but static fashion. As Imagine only executes one kernel at a time, the only task-level parallelism that can be utilized is that of pre-loading streams to the SRF.

# 2.2.3 Others Streaming Architectures

## Mainstream and Server Processors

As the performance return for more aggressive single-core processor design has diminished at the cost of greatly increased power consumption, all major processor designers have shifted to placing multiple processor cores on a die to achieve higher performance and better market penetration. This trend is rapidly moving commodity computing to the point where CMP platforms dominate the desktop, starting at first with dual-core, and moving rapidly towards quad-core, and beyond.

In addition to mainstream architectures, server manufacturers are also moving towards many-cored processors. Sun's Niagara [32] is an 8-core hardware multithreaded UltraSparc processor optimized for transaction processing. It competes with Azlu's Vega 2 [13], a 48-core RISC-style processor designed for running virtual machines and transactional code. Even non-processor companies such as Cisco have moved in this direction. Their CRS-1 [47] contains 192 Tensilica Xtensa cores and is designed for network packet processing.

While none of these processors are designed for streaming per se, [19] has shown that they can benefit from the data pre-fetching enabled by streaming applications, and that it would only take a small amount of hardware to fully enable streaming processing within their architectures [18]. As the number of cores increase, dataparallel applications will require extensive analysis to ensure that the memory system can keep the cores busy, thereby making stream-enabling hardware enhancements all the more appealing.

# **Commercial Streaming Architectures**

Commercial streaming architectures first appeared with the Sony-IBM-Toshiba Cell processor [21]. This processor provided 8 streaming processors with SIMD execution and software-managed shared instruction and data memories, along with a single dual-threaded RISC control core. The individual stream processors, referred to as Synergistic Processing Units for obscure reasons, communicate over a ring network in a non-coherent fashion. ClearSpeed's CSX600 [20] is a 96 processor floating point accelerator with 1TB/s internal network bandwidth. The picoArray PC102 from PicoChip [12] contains a heterogeneous array of 322 processors. The PC102 includes 3-way VLIW Harvard architecture units, control processors, and memory tiles, all connected by a statically programmed network of 32-bit busses. The Tilera Tile64 [46] is a commercial realization of the MIT Raw [45] architecture. Its initial implementation contains 64 VLIW cores with 5-on chip networks supporting user and system static and dynamic access. The Tile64 provides coherent shared-memory and keeps Raw's register-mapped network support, but adds hardware support for network endpoint buffers and more industry-oriented I/O. Similarly, the Storm-1 from Streaming Processors Incorporated [29], is a commercial fixed-point implementation of Stanford's Imagine [40] streaming processor. The Storm-1 doubles Imagine's 8 VLIW processing lanes to 16, and adds extensive support for full system integration and industry-standard I/O.

Intel has also disclosed two prototype streaming processor designs. The first, the Teraflop Research Chip [22], is an 80-core floating point processor with a simple on-chip mesh network and no memory coherence. In addition to exploring the construction of on-chip networks, the chip serves to test techniques for 3D integration by stacking SRAM dies on top of the processor die. More interestingly, Intel's Larabee project [8] presents a 16-core x86 architecture designed to be performancecompetetive with the special-purpose hardware of contemporary graphics processors. The initial design calls for multiple hardware threads per core, high-performance short-vector units, a large coherent, but distributed, cache, and specialized hardware texture fetches.

# **Graphics Processors**

Graphics Processing Units (GPUs), such as NVIDIA's G80 and ATI/AMD's R600 architectures, are effectively stream processors. Historically, GPUs have been special-purpose processors with fixed-function hardware to implement the graphics processing pipeline required to render real-time 3D images. However, as the rendering requirements have evolved (e.g., with the addition of programmable shaders and geometry manipulation), the hardware architectures have evolved to be more and more generic. The G80 and R600 generations have both moved to a generic set of multi-threaded processing units on which the stages of the graphics pipeline are dynamically scheduled and executed. For example, the G80 contains 16 processors with 8 cores each, and each core being time multiplexed across several threads [23]. The cores support 16KB of local shared memory and the system has direct access to high-speed graphics memory, and much slower access to the system's main memory. The R600 contains 4 SIMD arrays of 16 stream processing units each. The processors are 5-way scalar VLIW processors with support for 32-bit floating point multiplication [10].

While the individual processing cores, instruction dispatch, and data memories are still optimized for graphics rendering, these architectures have been very successful  $\langle y \rangle \mathcal{I}_{\mathcal{L}} \rangle$ for streaming computations. Indeed, by exposing producer-consumer locality and data parallelism, streaming models map very nicely to the GPU processing model [7]. The manufacturers have recognized this and begun to supply generic programming environments for accessing these resources for non-graphics tasks [35].

# Chapter 3

# **Related Work**

The concept of computing on streams of data, or stream computing, has been around for quite a while. Stephens [41] traces it back to P J Landin and his work in the 1960s on ALGO 60, and follows it as an active research and development topic up through the late 1990s. More recent developments are sumarized in [17, 16]. This section focuses on several particularly relevant contemporary streaming languages for media processing (StreamIt, StreamC/KernelC, Brook, and Sequoia) and the generalization of Synchronous Data Flow to multiple dimensions. Particular emphasis is placed on the StreamIt language and its implementation for the Raw hardware back-end as it closely resembles the target hardware described in this thesis. For an in-depth review of previous work in streaming programming languages, please refer to the two aforementioned references.

# 3.1 Streaming Languages and Implementations

# 3.1 StreamIt

One of the most well-explored example of a streaming programming language is StreamIt. The authors summarize the distinctive features of the language as follows:

"StreamIt differs from other stream languages in the single-input, singleoutput hierarchical structure that it imposes on streams. This structure aims to help the programmer by defining clean, composable modules that admit a linear textual representation." [43, 24]

StreamIt has been targeted to many-core architectures [17], clusters [44], and portable streaming frameworks [48]. In addition, multiple generations of the compiler have explored a broad range of optimizations across many large benchmarks [24, 17, 16].

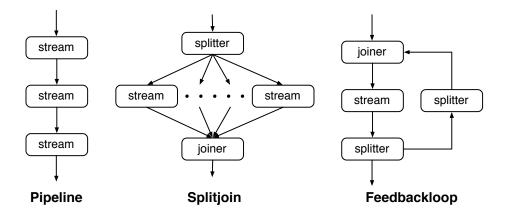

StreamIt represents applications as a hierarchical series of *filters* (e.g., computation kernels). The hierarchy comes from encapsulating multiple related filters in Pipeline, SplitJoin, and FeedbackLoop connecting filters. (See Figure 3.1 reproduced from [17], Figure 3.) Pipelines define a series of filters where the first sub-filter's output feeds the input of the next filter, and so on. SplitJoins are parameterized round-robin filters that duplicate or distribute the input data amongst multiple filters and collect the result. FeedbackLoops contain explicit "body" and "loop" filters and the description of what data is fed-back. The authors claim strongly [43, 17] that by enforcing this specific notion of hierarchy, instead of allowing the "flat and arbitrary network of filters" used by other streaming languages, applications written in StreamIt are both easier to write and easier to compile.

Figure 3.1: StreamIt supported hierarchical structures

Figure reproduced from [17], Figure 3. The "streams" can be other hierarchical structures or filters.

Filters are defined in terms of the number of input values they use and the number of output values they generate per iteration. As the StreamIt inputs and outputs are

fo 1100

Each filter in a StreamIt program contains three main methods: init(), prework(), and work() [43, 17] (see Figure 3.2). The init() method is called when the application is built and configures the filter. For example, the Pipeline connecting filter's init() function instantiates the filters to be included in the pipeline and connects them up as needed. The main execution of the filter occurs in work(), which is executed whenever the kernel is scheduled to be run. The prework() method is called before the first execution of work() to allow filters to generate sufficient outputs to fill the initial peek range required for downstream filters. Although undiscussed, it appears that the programmer must manually determine how many outputs to generate in the prework() method to satisfy downstream filters.

StreamIt provides a *portal*-based method for communicating control information out-of-band from the data streams. By separating this from the data-stream, the authors claim the application code is simplified as it keeps control and processing separate. The initial portal implementation allowed the programmer to manually define the latency range for the delivery of messages and send them via simple function calls. Later work on "teleport" messaging [44] enhanced this approach by applying analysis from the Cyclo-static Synchronous Data Flow (CSDF) domain [14] to improve the latency guarantees and reduce the overhead. Through these portals, StreamIt applications can accomplish one-to-many communications and provide multiple control outputs from a single filter. Except for enforcing the required delivery latency, the authors argue that these communications can be ignored in terms of their impact on the data processing schedule, although the language enforces no requirement that the

```

float->float filter FIRFilter (float sampleRate, int N) {

float[N] weights;

init {

weights = calcImpulseResponse(sampleRate, N);

3

prework push N-1 pop 0 peek N {

for (int i=1; i<N; i++) {</pre>

push(doFIR(i));

3

}

work push 1 pop 1 peek N {

push(doFIR(N));

pop();

}

float doFIR(int k) {

float val = 0;

for (int i=0; i<k; i++) {</pre>

val += weights[i] * peek(k-i-1);

3

return val;

}

}

```

Figure 3.2: StreamIt FIR filter example

Figure reproduced from [17], Figure 1. The init(), prework(), and work() functions are shown along with their definitions in terms of how many items the filter peeks, pops, and pushes.

message handlers execute quickly nor occur at a negligible rate.

In addition to fixed push, pop, and peek sizes for the filters, StreamIt applications have static rates that are known at compilation, with each filter's computation time being estimated by a static analysis of its code. This allows the compiler to treat the application as a quasi-Synchronous Data Flow problem [24], thereby allowing the use of a wide range of SDF scheduling techniques [6].<sup>1</sup> The initial motivation for generating static schedules for StreamIt applications appears to come from the need to statically schedule one of the two communications networks on the targeted Raw hardware [45, 17]. Historically, SDF applications have been statically scheduled to eliminate the overhead of dynamically determining the appropriate kernel to execute on a single DSP or processor, but this has become much less of an issue with many-core

<sup>&</sup>lt;sup>1</sup>Gordon [17] notes that the irregular round-robin nodes in StreamIt require that SDF-type analysis be applied in the context of the more general, but much more complex, CSDF framework.

processors [48]. As later compilers appear to have moved to entirely off-chip buffering for Raw [16], thereby reducing the dependency on the on-chip network, it is not clear why so much emphasis is put on obtaining a static schedule.

Mundia Ray The StreamIt compiler [17, 16] implements a variety of application transformations to try and achieve maximum performance across different benchmarks. The compiler tries explicitly to achieve the right balance of task-, data-, and pipeline-parallelism to maximize the utilization of the 16 processors in the Raw architecture while minimizing the overhead introduced due to synchronization and communications. The transformations are necessary, because although the StreamIt representation itself contains much parallelism, it may not map well or be well balanced. For example, the task parallelism exhibited by filters on different branches in the application requires significant synchronization if mapped directly to individual processors, and is unlikely to provide sufficient parallelism for the target architecture. If the data parallelism present in stateless filters is exploited for filters with low computation-to-communications ratios, the result will increase communications overhead and buffering. Similarly, pipeline parallelism from chains of producers and consumers may be plentiful, but is likely to exhibit poor load-balancing.