# MULTI-CARRIER SIGNALING FOR HIGH-SPEED ELECTRICAL LINKS

#### A DISSERTATION

SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING

AND THE COMMITTEE ON GRADUATE STUDIES

OF STANFORD UNIVERSITY

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

Amir Amirkhany

March 2008

© Copyright by Amir Amirkhany 2008

All Rights Reserved

| I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy. |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (Mark A. Horowitz) Principal Adviser                                                                                                                                      |

| I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy. |

| (John M. Cioffi)                                                                                                                                                          |

| I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy. |

| (Bruce A. Wooley)                                                                                                                                                         |

| Approved for the University Committee on Graduate Studies                                                                                                                 |

#### **Abstract**

The demand for ever higher performance at lower power is motivating system designers to re-think their design strategies not just in terms of performance, but in terms of power-performance efficiency. In this new design paradigm, the performance of a communication system is mainly limited by the "total system power" constraint rather than just the "transmit power". Therefore, the choice of the optimum data communication algorithm is a strong function of circuit level power-performance trade-offs. One area where such re-thinking is vital is electrical chip-to-chip communication, where total system power-performance efficiency in terms of mWatts per Gb/s is now the key metric. Multi Gb/s chip-to-chip links find applications in the data interfaces between microprocessors, memories, peripherals, and network processing components in high performance systems.

This thesis covers the design, analysis and implementation of a multi-carrier signaling method, called Analog Multi-Tone (AMT), specifically designed to take advantage of the characteristics of chip-to-chip link systems. In our design approach power-performance efficiency is achieved through a combination of various techniques including better utilization of transmit power, parallelization of the data stream in the frequency domain, channel engineering, in-system characterization of circuits with relevant performance metrics, and eventually, careful circuit design.

We start with a study of the performance and complexity of conventional multitone techniques. Based on the insight obtained from this analysis, we propose a novel multi-carrier signaling technique called Analog Multi-Tone, which is customized to the link characteristics. We develop a mathematical analysis of this system including a convex framework, and closed-form jitter modeling. This analysis also provides a method of comparing the performance of this approach with alternative baseband transmission methods.

The second half of this thesis focuses on circuit design issues involved in the design of a transmitter in a 90-nm CMOS technology supporting Analog Multi-Tone as well as a variety of baseband signaling modes including 4-PAM, 16-PAM and 64-PAM, all at 24-Gb/s. We further propose a Least-Squares based characterization and digital compensation techniques for improving system performance.

### **Acknowledgments**

Of all the parts in this dissertation, the acknowledgement is the part I have reviewed in my mind many times during my past six years at Stanford. Yet, now that I am starting to write, I find it difficult to summarize my gratitude for several years of help and support in only a few paragraphs. Either the Ph.D. program is just too long, or I have been very lucky to have had so many great people around me helping me out with different aspects of my life at Stanford.

I am indebted to my advisor, Professor Horowitz. Mark has a reputation for being a great advisor, and I can only be another testimony to this fact. Mark takes every aspect of his advising role seriously. On the technical side, he is always a great person for analyzing ideas and finding their faults. On non-technical issues, I always find him concerned and available for help. Mark is also a great teacher. What I really like about his approach is his way of training students to break down hard problems to simple fundamental concepts, and I am particularly grateful to him for that. I would only hope to live up to his standards as an advisor and a teacher through the rest of my career.

My associate advisor, Prof. Cioffi, has always been kind to me with any questions I have had and I have also benefited a lot from taking his courses. His approach to teaching communications is very unique in being very practical. A good part of my Ph.D. work relies on what I learned from his courses.

I would also like to thank Professor Wooley, for taking the time to read this manuscript and provide feedback, and Professor Pease, for making it possible for me to study together with my wife on this side of the Bay by offering me a one year fellowship after I was admitted to both Stanford and Berkeley.

I was fortunate to have Rambus support my Ph.D. project. I received a lot of help from many individuals in Rambus during the past four years. None of that would have been possible without Rambus' willingness to invest in my work, and create a team to move forward with implementation aspects of the project.

In the past few years, I have particularly benefited a lot from discussions with two individuals: Dr. Ali Abbasfar of Rambus and Prof. Vladimir Stojanovic of MIT. Ali is a great person for brain storming and discussing different ideas. He has a strong intuition and is a valuable colleague for any research work. Vladimir was the first person who helped me with my research at Stanford even before I got into Mark's group. I am grateful to him for many hours of fascinating discussions and collaborative work, and for both acting as a great mentor and a friend.

The rest of our team at Rambus who worked on the implementation of the transmitter, Bruno Garlepp, our manager, Dr. Jafar Savoj, who designed the digital to analog converter, and Metha Jeeradit, who helped me with the design of the equalizer, have all been great colleagues and friends. I have benefited and learned a lot from our collaboration.

I am also thankful to several other individuals in Rambus: Ravi Kollipara who was my main reference for signal integrity issues, Jared Zerbe who first advocated my project in Rambus, and Joe Louis Chandran and Kumar Gogenini for help with CAD issues.

Many of my colleagues in Mark's group helped me a lot by providing valuable feedback and spending the time to help me out within their areas of expertise. Especially, I would like to first thank my wife, Bita Nezamfar, for being available for technical discussions 24 hours a day, seven days a week! I would also like to especially thank Prof. Elad Alon and Dr. Dinesh Patil for many good suggestions and interesting ideas.

People who need to speak with Mark on a regular basis generally find it very difficult without the help of our kind group admin, Teresa Lynn. Her constant

readiness to make an extra effort to make things smooth and easy deserves a big thank you!

My years at Stanford wouldn't have been as fun without the large community of Persian friends and colleagues. I feel privileged to have so many close friends while being so far away from home.

I have been fortunate to have my wife, Bita, with me all along as a wonderful companion, colleague and friend. It has been really fun living together and studying together, and I can only wish her the best with her own endeavors. I am also very grateful to Bita's family for being extremely kind to me in the past 7 years, for always sharing our stress and happiness, and offering their kindest prayers and support.

It certainly wouldn't have been possible for me to get this far without the sacrifices of my parents, Abbas and Mehri. This dissertation is a result of their 30 years of infinite love and support, and for that, they own all my success. This dissertation is only dedicated to them as a token of thankfulness and gratitude. I am also very thankful to my brother Arash for his constant love, and for filling in for me at home while I have been away.

## **Table of Contents**

| ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| ACKNOWLEDGMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VI      |

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | X       |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | XV      |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | XVI     |

| CHAPTER 1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1       |

| 1.1 Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |

| 1.2 CONTEMPORARY BB LINKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |

| CHAPTER 2 DISCRETE MULTI-TONE REQUIREME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | NTS11   |

| 2.1 DISCRETE MULTI-TONE SYSTEM FORMULATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12      |

| 2.2 INCREMENTAL BIT-LOADING AND POWER ALLOCATION AN | ATION19 |

| 2.3 DMT System Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23      |

| 2.3.1 Effect of DMT Block Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24      |

| 2.3.2 Effect of ADC Quantization Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 30      |

| 2.3.3 System Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 30      |

| 2.4 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 32      |

| CHAPTER 3 ANALOG MULTI-TONE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33      |

| 3.1 Analog Multi-Tone Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 34      |

| 3.2 System Modeling and Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 38      |

| 3.2.1 Convex Formulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40      |

| 3.2.2 BER Constrained ZFE-DFE Solution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 41      |

| 3.2.3 Jitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 44      |

| 3.2.3.1 TX jitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44      |

| 3.2.3.2 RX jitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40      |

| 3.3 Performance Analysis and Simulation Resu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ULTS47  |

| 3.       | .3. <i>1</i> | Power Allocation Gain                               | 47  |

|----------|--------------|-----------------------------------------------------|-----|

| 3.       | .3.2         | Parallelization Gain                                | 48  |

| 3.4      | Sui          | MMARY                                               | 52  |

| CHAPTER  | 4            | AMT VARIATIONS                                      | 53  |

| 4.1      | DU           | OBINARY AMT WITH CHANNEL ENGINEERING                | 54  |

| 4.2      | SA           | MPLER-BASED AMT RECEIVER                            | 56  |

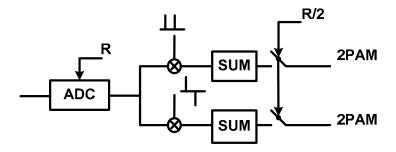

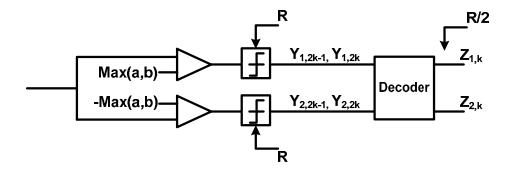

| 4.       | .2.1         | 2-Channel Sampler-Based AMT Receiver                | 57  |

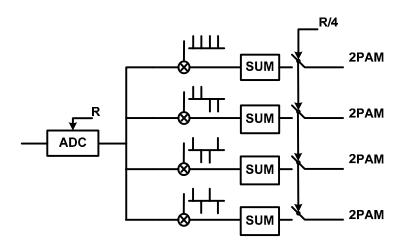

| 4.       | .2.2         | 4-Channel Sampler-Based AMT Receiver                | 59  |

| 4.3      | Sui          | MMARY                                               | 64  |

| CHAPTER  | 5            | EXPERIMENTAL SYSTEM                                 | 65  |

| 5.1      | Tr.          | ANSMITTER ARCHITECTURE                              | 66  |

| 5.2      | ME           | ASURED TRANSMITTER PERFORMANCE                      | 73  |

| 5.3      | От           | HER TRANSMITTER OPERATING MODES                     | 74  |

| 5.       | 3.1          | Multi-PAM Operation                                 | 75  |

| 5.       | 3.2          | Linear Cyclic Time-Variant Equalization             | 77  |

| 5.4      | Sui          | MMARY                                               | 78  |

| CHAPTER  | ,            | CHARACTERIZATION AND COMPENSATION OF WIDEBAND CI 79 |     |

| 6.1      |              | DEBAND CIRCUIT CHARACTERIZATION                     |     |

| -        | .1.1         | LSE-Based Characterization                          |     |

|          | .1.2         | CTV Characterization                                |     |

|          | .1.3         | Non-linearity Decomposition                         |     |

|          | .1.4         | Effect of Observation Length                        |     |

| 6.2      |              | AL-TIME CHARACTERIZATION OF THE 12-GS/S DAC         |     |

| 6.3      |              | ME VARIANT DIGITAL COMPENSATION                     |     |

| 6.4      |              | MMARY                                               |     |

| CHAPTER  | 7            | CONCLUSIONS                                         | 97  |

| APPENDIX | A            | CURRENT-MODE AMT TRANSMIT EQUALIZER                 | 101 |

| APPENDIX | В            | PILOT-BASED CLOCK AND DATA RECOVERY FOR AMT         | 109 |

| APPENDIX |              | SEMI-CUSTOM HIGH-SPEED DATAPATH DESIGN USING        |     |

| COMMERI  | CIAI         | L ASIC DESIGN TOOLS                                 | 113 |

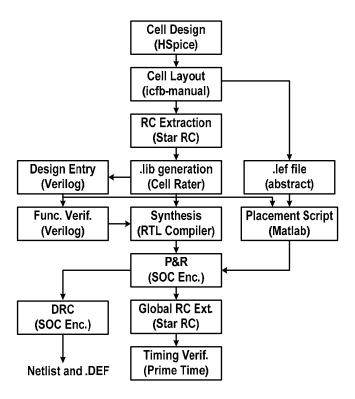

| C.1      | SEN          | MI-CUSTOM HIGH-SPEED DATAPATH DESIGN                | 114 |

| C.2      | Eo           | UALIZER DESIGN FLOW                                 | 117 |

| C.2.1       | Cell design                 | 118 |

|-------------|-----------------------------|-----|

| C.2.2       | Cell layout                 | 119 |

| C.2.3       | Hierarchical Verilog        | 119 |

| C.2.4       | Synthesis                   | 120 |

| C.2.5       | Hierarchical Placement      | 120 |

| C.2.6       | Routing                     | 124 |

| C.2.7       | Clock Distribution          | 124 |

| C.2.8       | Timing Verification         | 124 |

| C.3 AD      | OVANTAGES AND DISADVANTAGES | 125 |

| BIBLIOGRAPH | Y                           | 127 |

## **List of Tables**

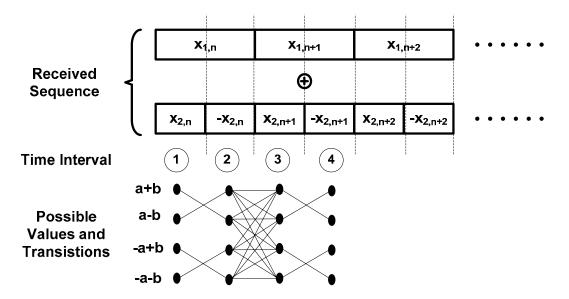

| TABLE 4.1: 2-CHANNEL AMT DECODER FUNCTIONALITY. "X" REPRESENTS A "DON'T CARE" VALUE 59    |

|-------------------------------------------------------------------------------------------|

| TABLE 4.2: SIGN OF DETECTED SIGNAL WITH A SAMPLER PLACED AT ZERO DURING THE FOUR QUARTER- |

| SYMBOL TIME SLOTS FOR CONSTELLATION POINTS THAT BELONG TO THE ODD GROUP62                 |

## **List of Figures**

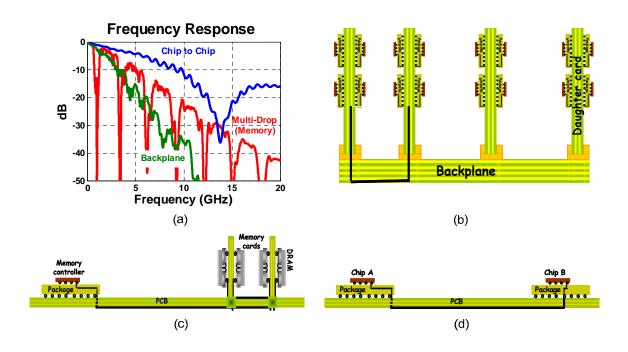

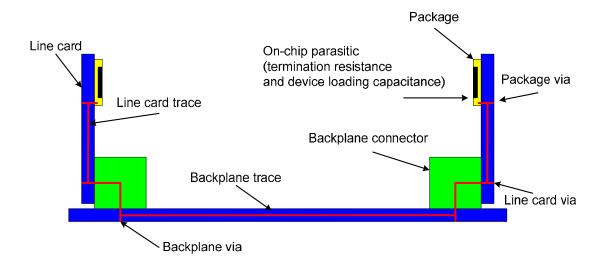

| FIGURE 1.1: (A) CHANNEL CHARACTERISTICS IN FREQUENCY DOMAIN. (B) AN ELECTRICAL LINK IN A                           |

|--------------------------------------------------------------------------------------------------------------------|

| NETWORK ROUTER (C) A MULTI-DROP MEMORY INTERFACE (D) A CPU-GPU LINK2                                               |

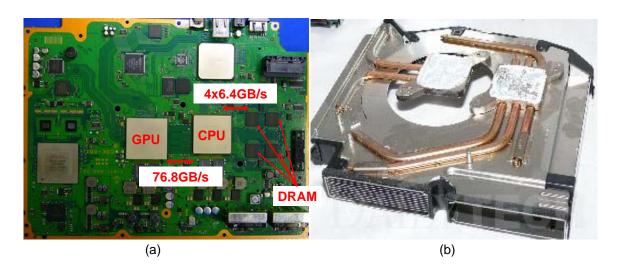

| FIGURE 1.2: (A) PLAYSTATION 3® MAIN-BOARD AND (B) HEAT-SINK.                                                       |

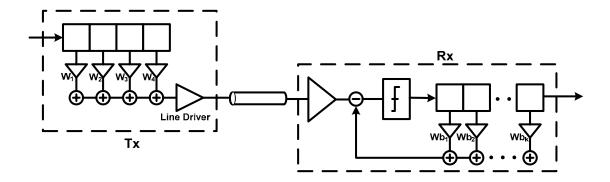

| Figure 1.3: A conventional state of the art 2-PAM BB system with a linear FF equalizer at                          |

| THE TRANSMITTER, AND A LINEAR PEAKING AMPLIFIER AND A DFE AT THE RECEIVER                                          |

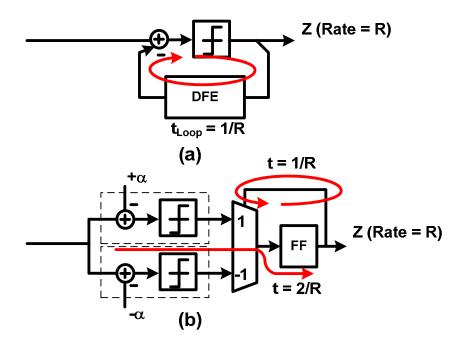

| FIGURE 1.4: (A) DFE LOOP TIMING CONSTRAINT FOR THE FIRST TAP (B) A LOOP-UNROLLED DFE9                              |

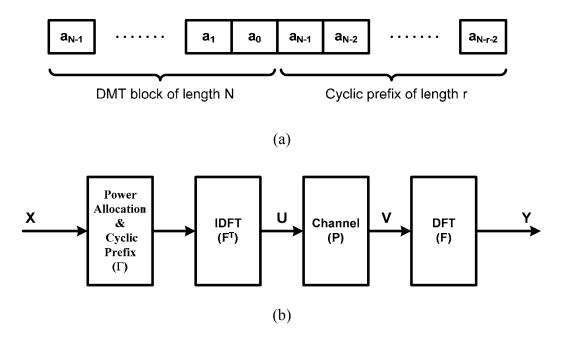

| eq:figure 2.1: (A) DMT frame consisting of A Data Block of Size N and Cyclic Prefix of Size R. (B)                 |

| BLOCK DIAGRAM OF A DMT SYSTEM                                                                                      |

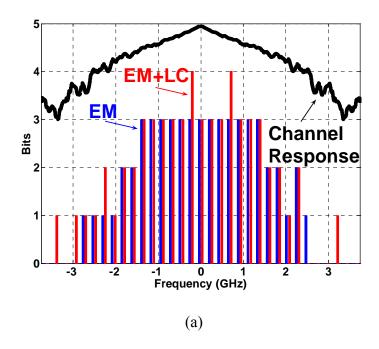

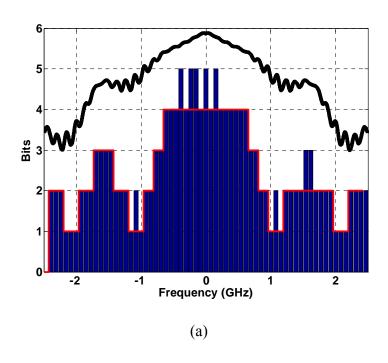

| FIGURE 2.2: (A) BIT-LOADING OVER A 20" BACKPLANE FR4 CHANNEL FOR EM AND EM+LC. (B) SNR AT                          |

| THE RECEIVER FOR EM+LC. BOTH FIGURES FOR A DMT SYSTEM WITH BLOCK SIZE OF 32, CYCLIC                                |

| PREFIX LENGTH OF $8$ , and sample rate of $7 \mathrm{GHz}$ . Peak to peak transmit voltage is $1.6 \mathrm{V}$ and |

| Noise Figure is set to 10dB.                                                                                       |

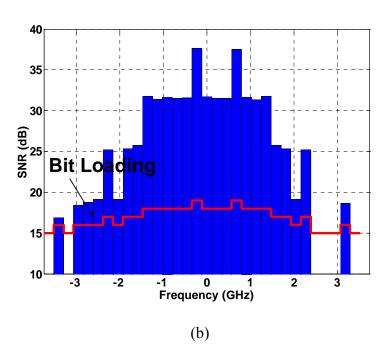

| FIGURE 2.3: FREQUENCY RESPONSE OF 20" FR4 AND NELCO BACKPLANE CHANNELS                                             |

| FIGURE 2.4: CROSS-SECTION OF A BACKPLANE SYSTEM WITH TWO LINE-CARDS.                                               |

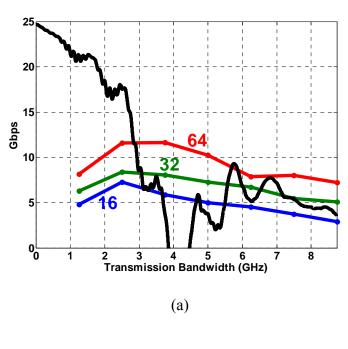

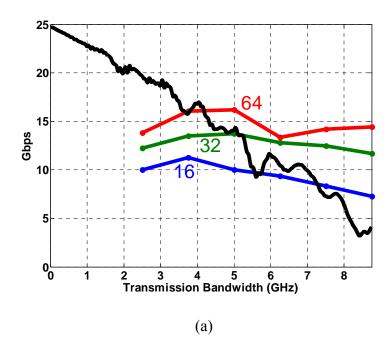

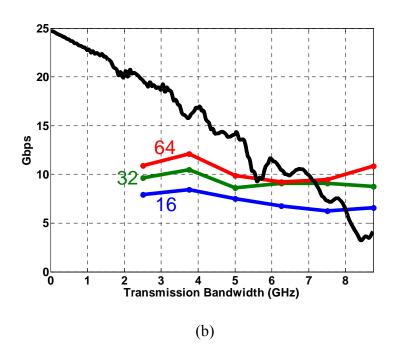

| FIGURE~2.5: MAXIMUM~ACHIEVABLE~DATA~RATE~(WITH~OPTIMUM~PREFIX~LENGTH)~OVER~20"~FR4~(LEFT)                          |

| AND 20" NELCO (RIGHT) CHANNELS FOR DMT BLOCK-SIZES OF 16, 32, 64 AND TRANSMISSION                                  |

| BANDWIDTHS (HALF THE FFT RATE) OF 1.25-GHZ TO 8.75GHZ. CHANNEL FREQUENCY RESPONSE                                  |

| (IN DB) SUPER-IMPOSED ON THE FIGURES WITH AN ARBITRARY SCALE. NOISE FIGURE IS ASSUMED                              |

| TO BE 10DB                                                                                                         |

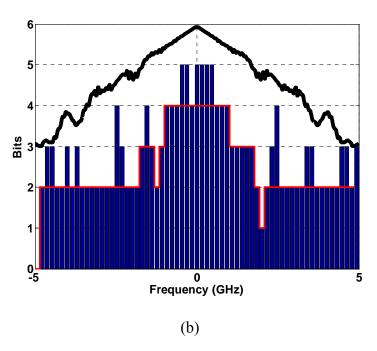

| FIGURE 2.6: OPTIMUM BIT-LOADING OBTAINED WITH THE EM METHOD TO ACHIEVE MAXIMUM                                     |

| THROUGHPUT OVER THE FR4 (LEFT) AND NELCO (RIGHT) CHANNELS. THE SOLID RED LINE IN                                   |

| BOTH FIGURES REPRESENTS AN ALTERNATIVE FEASIBLE BIT-LOADING, IN WHICH ADJACENT SUB-                                |

| CHANNELS WITH SIMILAR BIT ASSIGNMENT ARE GROUPED TOGETHER                                                          |

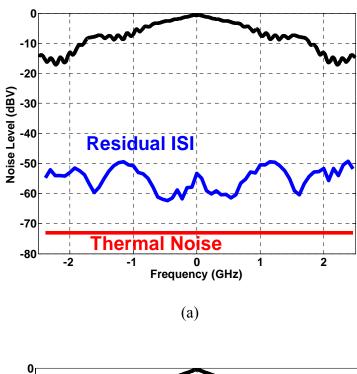

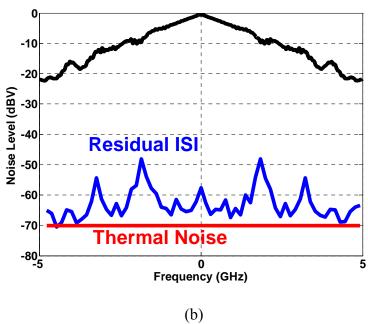

| Figure 2.7: Residual interference at the Receiver for the FR4 (a) and the NELCO (b)                                |

| Channels. Noise Figure of $10\text{dB}$ over system bandwidth is also shown in the figures 28                      |

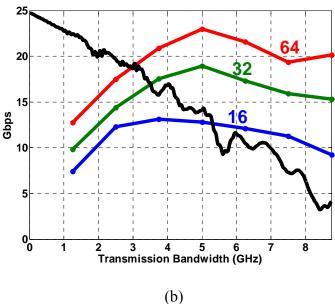

| FIGURE 2.8: MAXIMUM ACHIEVABLE DATA RATE (WITH OPTIMUM PREFIX LENGTH) OVER THE NELCO                               |

| CHANNEL FOR DMT BLOCK-SIZES OF 16, 32, 64 AND ADC RESOLUTION OF 7-BITS (A) AND 6-BITS                              |

| (B). OTHER SIMULATION SETTINGS ARE SIMILAR TO FIGURE 2.5.                                                          |

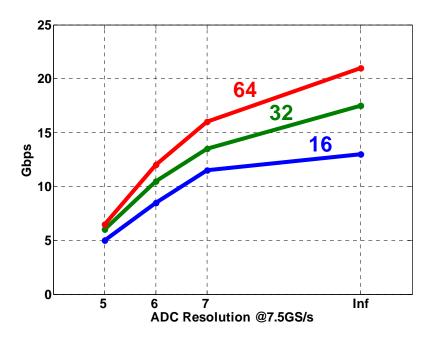

| FIGURE 2.9: MAXIMUM ACHIEVABLE DATA RATE (WITH OPTIMUM PREFIX LENGTH) OVER THE NELCO             |

|--------------------------------------------------------------------------------------------------|

| CHANNEL FOR DMT BLOCK-SIZES OF 16, 32, 64 AND ADC SAMPLING RATE OF 7.5-GHZ, AND                  |

| RESOLUTION OF 5, 6, 7, AND INFINITE BITS.                                                        |

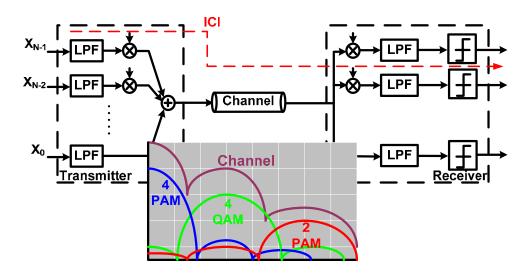

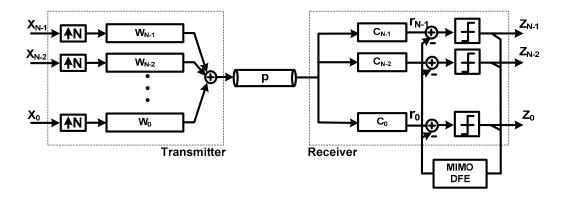

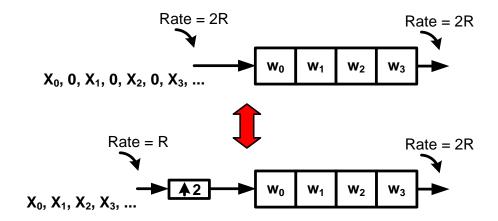

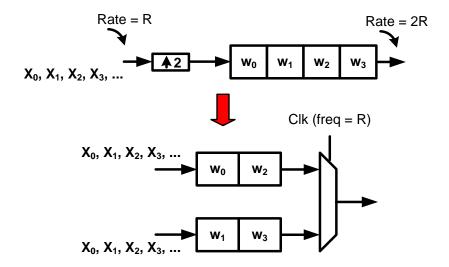

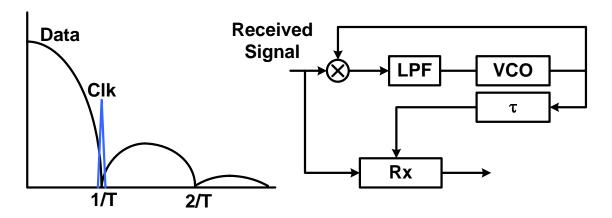

| FIGURE 3.1: A CONCEPTUAL MULTI-TONE SYSTEM. X <sub>0</sub> ,, X <sub>N</sub> ARE INPUT SEQUENCES |

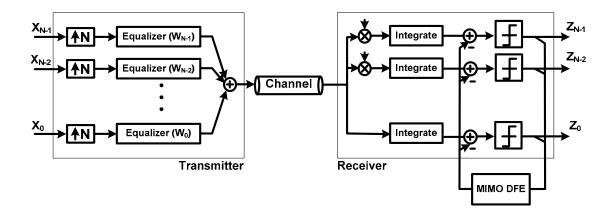

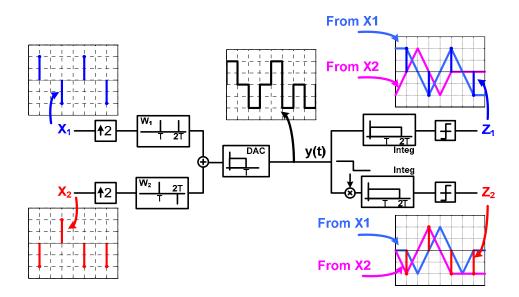

| FIGURE 3.2: ANALOG MULTI-TONE ARCHITECTURE 36                                                    |

| FIGURE 3.3: SIGNAL WAVEFORMS IN AN EXAMPLE 2-CHANNEL AMT SYSTEM. TWO-TAP EQUALIZERS PER          |

| SUB-CHANNEL AT THE TRANSMITTER, IDEAL CHANNEL, AND NO DFE AT THE RECEIVER.                       |

| CONTINUOUS-TIME ISI AND ICI PATTERNS ARE SHOWN AT THE SAMPLER INPUTS                             |

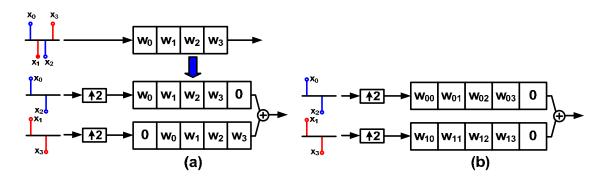

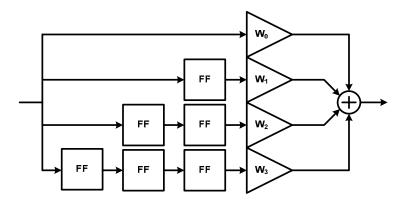

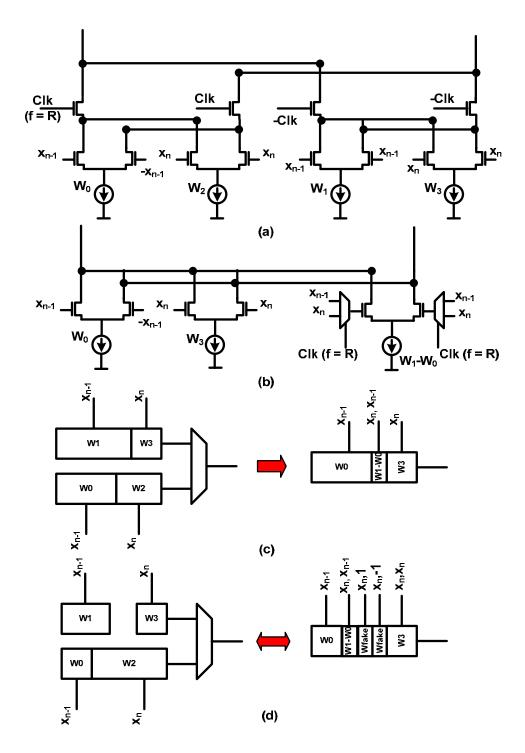

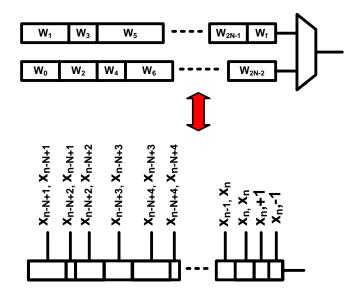

| FIGURE 3.4: (A) A 4-TAP LINEAR EQUALIZER REPRESENTED AS A 2-WAY PARALLELIZED FILTER (B) A 2-     |

| CHANNEL 4-TAP PER CHANNEL AMT EQUALIZER                                                          |

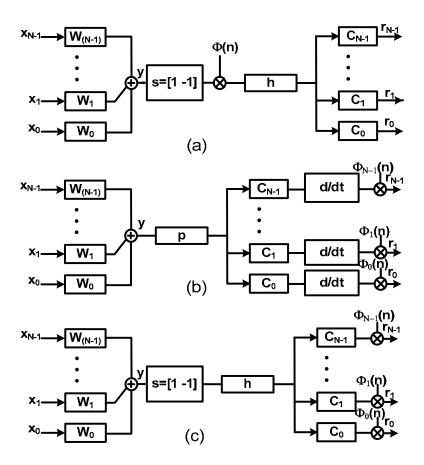

| FIGURE 3.5: AMT SYSTEM MODEL                                                                     |

| FIGURE 3.6: (A) TRANSMITTER JITTER MODEL. (B) RECEIVER JITTER MODEL (C) ALTERNATIVE RECEIVER     |

| JITTER MODEL. 45                                                                                 |

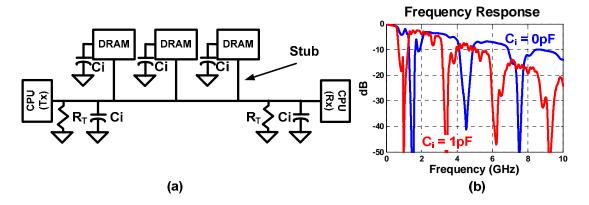

| FIGURE 3.7: (A) A GENERIC MULTI-DROP CONFIGURATION, WHERE THREE MEMORY MODULES ARE               |

| CONNECTED TO TWO CPUS. ONLY THE TWO CPUS HAVE TERMINATION RESISTORS (B)                          |

| CORRESPONDING CHANNEL FREQUENCY RESPONSES FOR OPF AND 1PF OF PARASITIC CAPACITANCE               |

| PER DEVICE. 48                                                                                   |

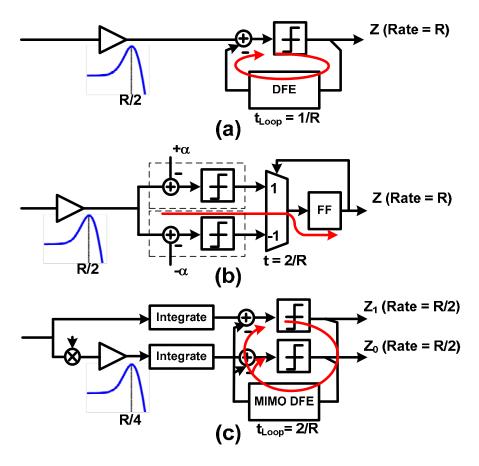

| FIGURE 3.8: (A) A BB 2PAM RECEIVER WITH A PEAKING LINEAR AMPLIFIER AND A DFE OPERATING AT        |

| RATE R (B) A LOOP-UNROLLED BB 2PAM RECEIVER. $\alpha$ represents the first DFE tap value.        |

| (C) A 2-CHANNEL (2PAM, 2PAM) AMT RECEIVER OPERATING AT RATE R                                    |

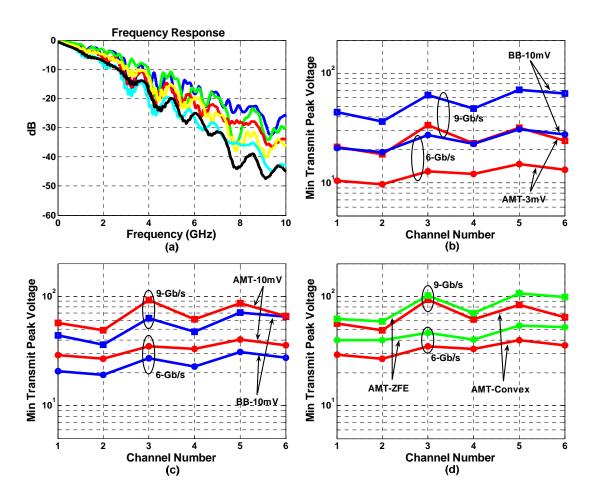

| FIGURE 3.9: (A) FREQUENCY RESPONSES OF 6 NELCO BACKPLANE CHANNELS: 3", 10" AND 20", ROUTED       |

| ON TOP OR BOTTOM LAYERS OF A PCB (B) MINIMUM REQUIRED TRANSMIT PEAK VOLTAGE TO                   |

| ACHIEVE BER OF 10 <sup>-15</sup> AT 6-GB/S AND 9-GB/S FOR 2PAM BB AND 2-CHANNEL AMT SYSTEMS,     |

| ASSUMING AMT SYSTEM HAS MORE SENSITIVE SAMPLERS. SIMILAR EQUALIZATION COMPLEXITY                 |

| FOR BOTH SYSTEMS (C) SAME AS (B), BUT ASSUMING SAMPLERS IN BOTH AMT AND BB HAVE SAME             |

| SENSITIVITY OF 10MV (D) COMPARISON OF BER-CONSTRAINED ZFE AND CONVEX SOLUTIONS FOR               |

| THE AMT SYSTEM UNDER SAME CONDITIONS AS (C)                                                      |

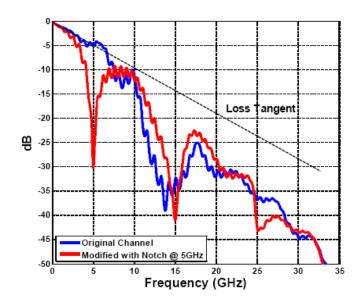

| FIGURE 4.1: A CHIP TO CHIP SYSTEM WITH A DOMINANT STUB ON THE PACKAGE OF CHIP B                  |

| FIGURE 4.2: FREQUENCY RESPONSE OF THE ORIGINAL CHIP-TO-CHIP CHANNEL, AND THE MODIFIED            |

| RESPONSE AFTER THE LENGTH OF THE PLATING STUB WAS INCREASED                                      |

| FIGURE 4.3: A DIGITAL IMPLEMENTATION OF A 2-CHANNEL AMT RECEIVER                                 |

| FIGURE 4.4: DECOMPOSITION OF THE RECEIVED SEQUENCE AT THE RECEIVER INPUT WITH NO DFE AT THE      |

| RECEIVER. IT IS ASSUMED A>B FOR THIS FIGURE. 58                                                  |

| FIGURE 4.5: SAMPLER-BASED 2-CHANNEL AMT RECEIVER                                                 |

| FIGURE 4.6: A DIGITAL IMPLEMENTATION OF A 4-CHANNEL AMT RECEIVER                                 |

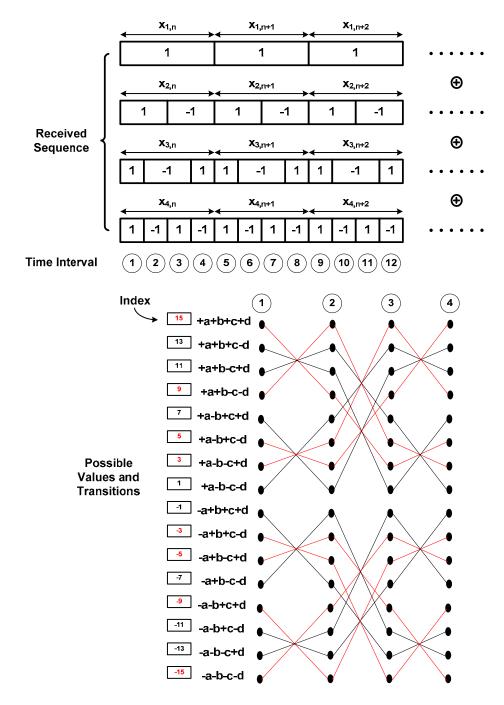

| FIGURE 4.7: RECEIVED SEQUENCE PATTERN FOR PERFECT RECOVERY DECOMPOSED TO DIFFERENT SUB-          |

| CHANNELS IT IS ASSUMED THAT THE 1ST SUB-CHANNEL HAS A SCALE OF "A" AND THE 2ND 3RD               |

| AND 4TH SUB-CHANNELS HAVE SCALES OF "B", "C", AND "D" RESPECTIVELY. ALSO ALL POSSIBLE          |

|------------------------------------------------------------------------------------------------|

| TRANSITIONS WITHIN ONE SUB-CHANNEL SYMBOL PERIOD ARE SHOWN. INPUT SEQUENCES WHICH              |

| MAKE A TRANSITION TO "+A+B+C+D" OR "-A-B-C-D" ARE SHOWN IN RED6                                |

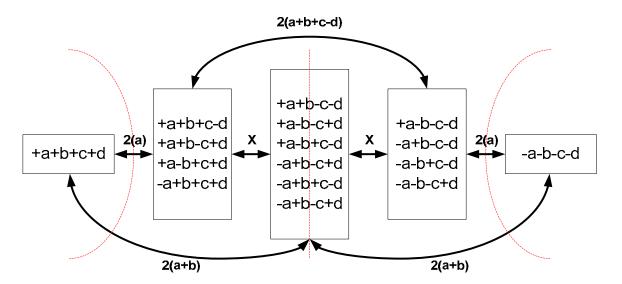

| FIGURE 4.8: 16 RECEIVED CONSTELLATION POINTS GROUPED INTO 5 SETS. MINIMUM DISTANCE BETWEEN     |

| THE POINTS ALSO SHOWN ASSUMING A≤B≤C≤D                                                         |

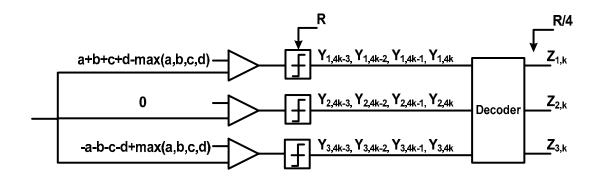

| FIGURE 4.9: SAMPLER-BASED 4-CHANNEL AMT RECEIVER. 6                                            |

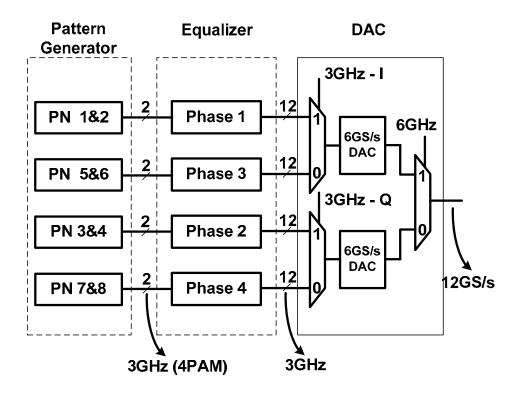

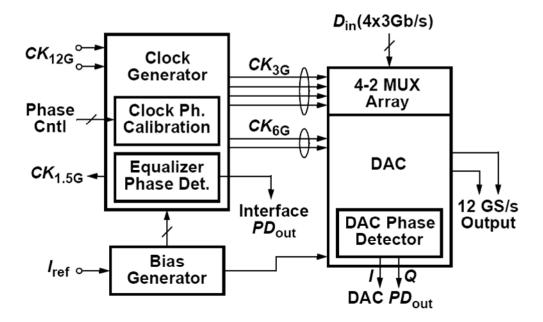

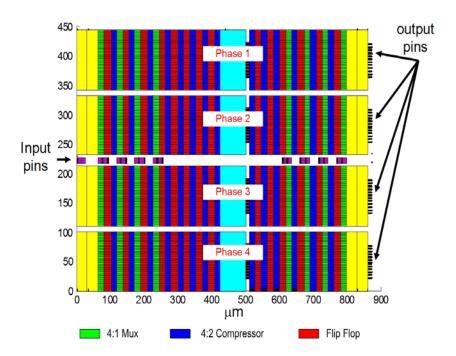

| FIGURE 5.1: TRANSMITTER BLOCK DIAGRAM. AN ON-CHIP CLOCK GENERATOR CIRCUIT (NOT SHOWN IN        |

| THE FIGURE) GENERATES THE 6-GHZ, 3-GHZ, AND 1.5-GHZ CLOCKS NECESSARY FOR THE SYSTEM            |

| 6                                                                                              |

| FIGURE 5.2: DAC ARCHITECTURE. 6                                                                |

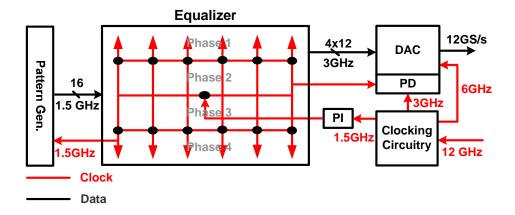

| FIGURE 5.3: TRANSMITTER CLOCK NETWORK. BLACK DOTS IN THE EQUALIZER INDICATE THE PLACEMENT      |

| OF THE CLOCK DRIVERS. A PHASE INTERPOLATOR (PI) SHIFTS THE PHASE OF THE INPUT CLOCK TO         |

| THE TRANSMITTER BASED ON INFORMATION FROM A PHASE DETECTOR (PD). THE PHASE DETECTOR            |

| SAMPLES A 1.5-GHZ CLOCK THAT BRANCHES OFF FROM A LEAF OF THE EQUALIZER'S CLOCK GRID            |

| WITH THE 3-GHZ INPUT CLOCK TO THE DAC.                                                         |

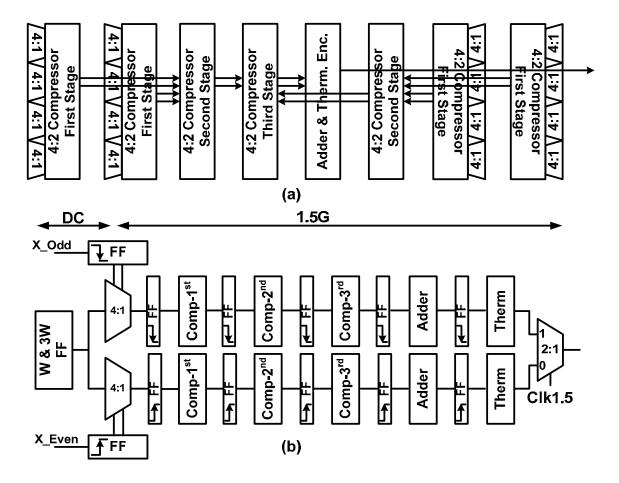

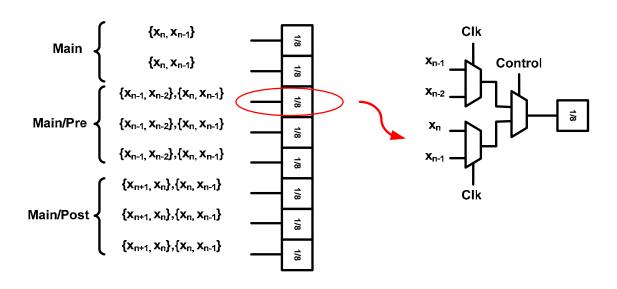

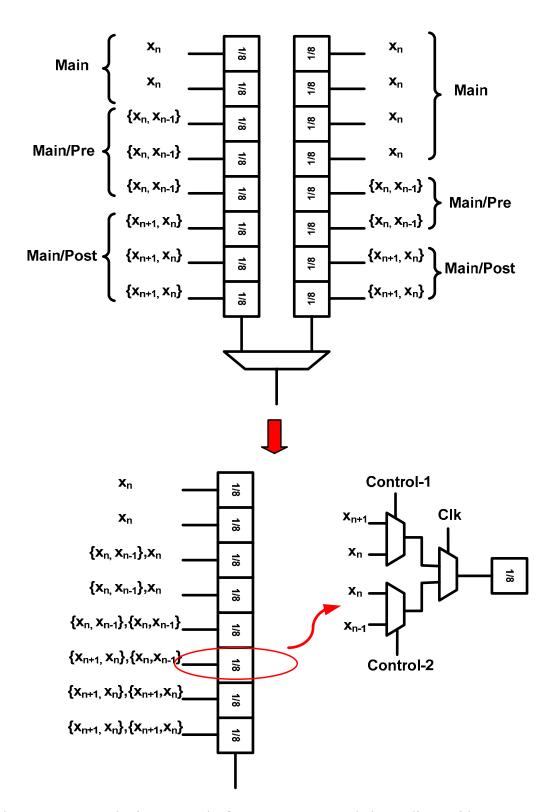

| FIGURE 5.4: (A) DIRECTIONS OF DATA FLOW IN THE DIGITAL EQUALIZER. (B) DATAPATH OF ONE PHASE OF |

| THE EQUALIZER CONSISTING OF THREE STAGES OF 4:2 COMPRESSION, A PSEUDO KOGGE-STONE              |

| ADDER AND A THERMOMETER ENCODER. EACH BLOCK IS 2-WAY PARALLELIZED AND A $2:1$                  |

| MULTIPLEXER (SERIALIZERS) IS INCLUDED IN THE THERMOMETER ENCODER6                              |

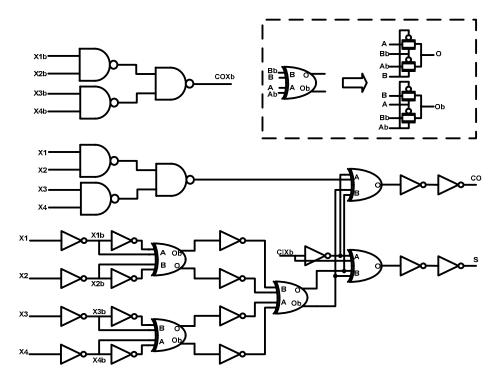

| FIGURE 5.5: 4:2 COMPRESSOR SCHEMATIC. THE CRITICAL PATH IS FROM X1 TO CO7                      |

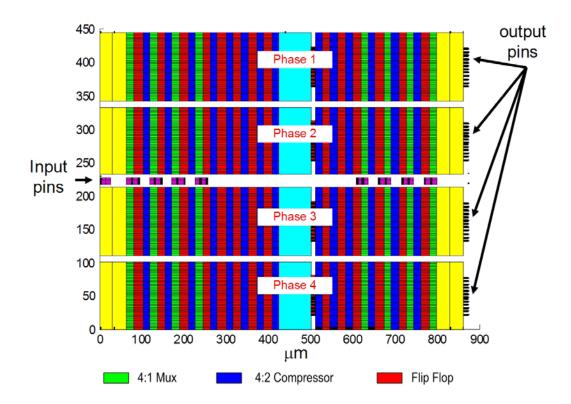

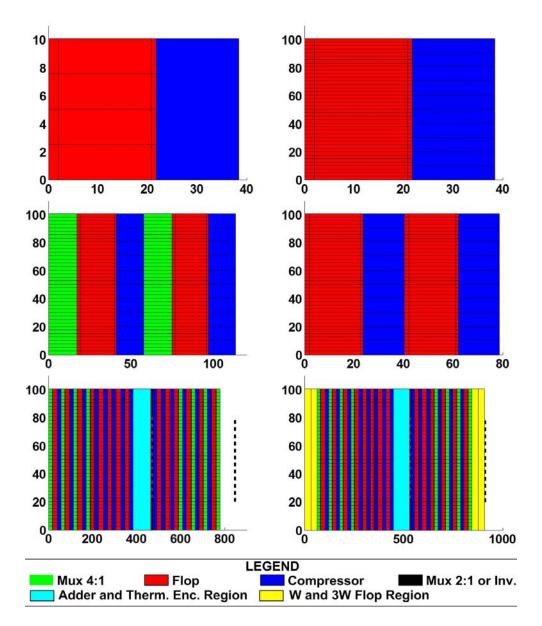

| FIGURE 5.6: EQUALIZER FLOORPLAN IN THE MATLAB PLACEMENT TOOL. YELLOW RECTANGLES ON THE         |

| SIDES ARE AREAS WHERE LOW-SPEED FLIP-FLOPS HOLDING EQUALIZER TAP COEFFICIENTS ARE              |

| PLACED BY THE P&R TOOL. THE CYAN RECTANGLES IN THE MIDDLE ARE AREAS WHERE THE ADDE             |

| AND THE THERMOMETER ENCODER ARE PLACED BY THE $P\&R$ TOOL. THE PINK RECTANGLES IN THE          |

| MIDDLE ROW ARE LATCHES, IMPLEMENTING THE SHIFT REGISTERS FOR THE INPUT DATA SEQUENCE           |

| X AND Y AXES SHOW ACTUAL SIZES IN MICRONS                                                      |

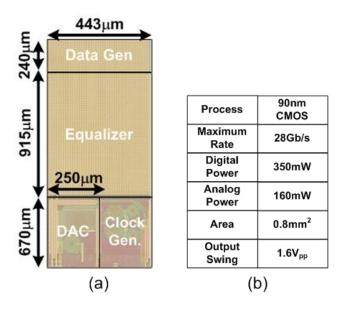

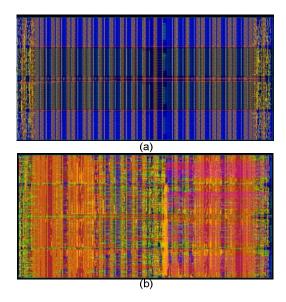

| FIGURE 5.7: (A) CHIP MICROGRAPH (B) PERFORMANCE SUMMARY                                        |

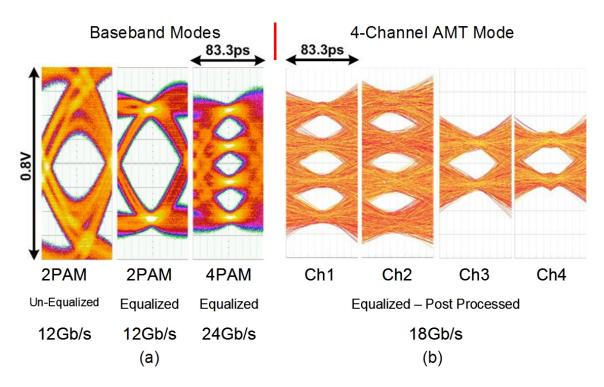

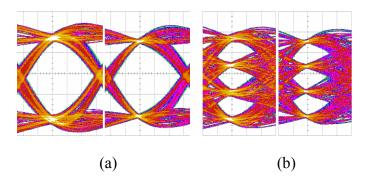

| FIGURE 5.8: (A) EYE DIAGRAMS MEASURED ON A SCOPE WHEN THE TRANSMITTER IS OPERATING IN BB       |

| MODE: UN-EQUALIZED 2-PAM AT 12-GB/S (LEFT), EQUALIZED 2-PAM AT 12-GB/S (MIDDLE) AND            |

| EQUALIZED 4-PAM AT 24-GB/S. (B) EYE DIAGRAMS MEASURED AT THE TRANSMITTER OUTPUT                |

| WITH A SCOPE AND POST-PROCESSED IN MATLAB (MIXING AND INTEGRATION PER CHANNEL – NO             |

| DFE) WHEN THE TRANSMITTER IS OPERATING IN 4-CHANNEL 18-GB/S AMT MODE7                          |

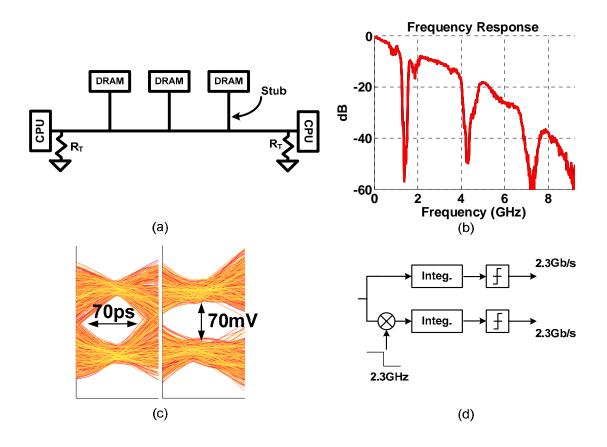

| FIGURE 5.9: (A) A MULTI-DROP CONFIGURATION (B) MEASURED FREQUENCY RESPONSE OF A THREE-DRO      |

| 16" FR4 trace (c) Eye diagrams based on measured data when only two 2PAM, 2.3-GS/s             |

| SUB-CHANNELS ARE USED. TOTAL THROUGHPUT IS $4.6$ -Gb/s (d) Block diagram of the receive        |

| SIMILITATED IN MATIAR TO CENEDATE THE EVES                                                     |

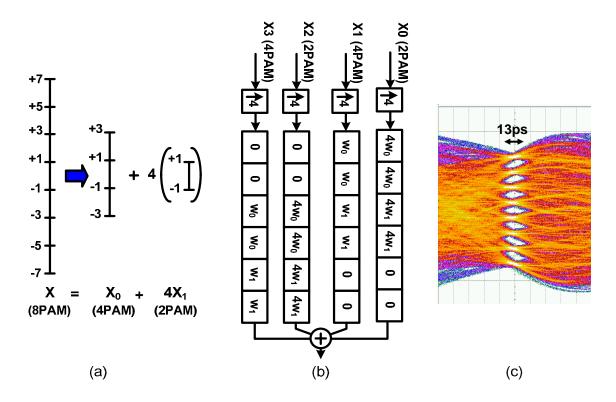

| FIGURE 5.10: (A) 8-PAM SYMBOL DECOMPOSITION TO A 4-PAM AND A 2-PAM SYMBOL. (B)                                   |

|------------------------------------------------------------------------------------------------------------------|

| Transmitter configured in 8-PAM mode (only 6 taps per phase shown) (c) Eye diagram                               |

| ON A SCOPE IN 8-PAM, 36-GB/S MODE                                                                                |

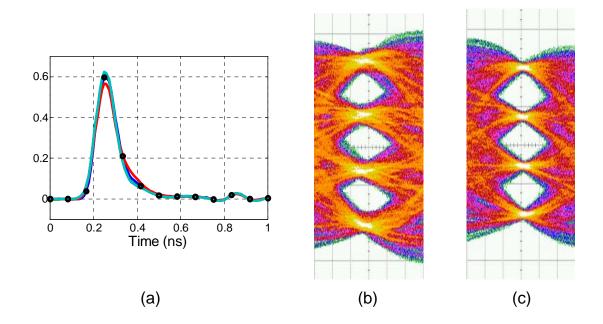

| FIGURE 5.11: (A) MEASURED PULSE RESPONSES OF THE 4 PHASES OF THE DAC. (B) LTI EQUALIZED BB                       |

| 4PAM 28GB/S EYES ON A SCOPE (B) CYCLICALLY TIME-VARIANT EQUALIZED BB 4PAM 28GB/S                                 |

| EYES ON A SCOPE                                                                                                  |

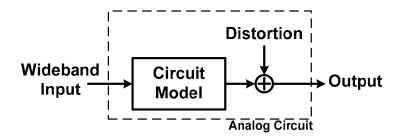

| FIGURE 6.1: SYSTEM MODEL FOR CHARACTERIZATION PURPOSES                                                           |

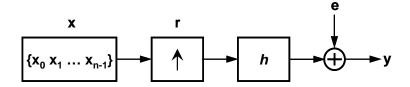

| FIGURE 6.2: WIDEBAND CHARACTERIZATION USING A RANDOM SEQUENCE                                                    |

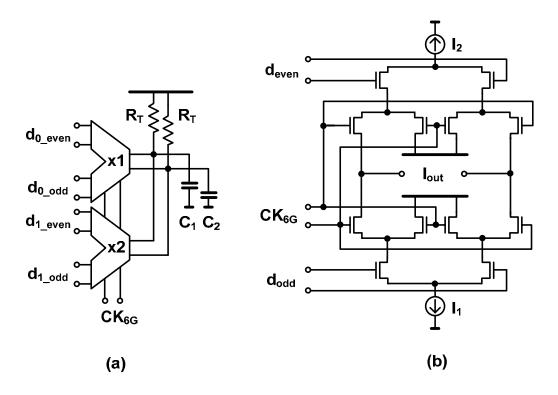

| FIGURE 6.3: (A) BLOCK DIAGRAM OF A 2-BIT DAC (B) 1-BIT OUTPUT-MULTIPLEXED DRIVER CELL 84                         |

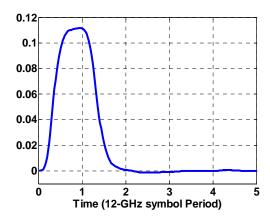

| FIGURE 6.4: 2-BIT DAC SINGLE BIT RESPONSE.                                                                       |

|                                                                                                                  |

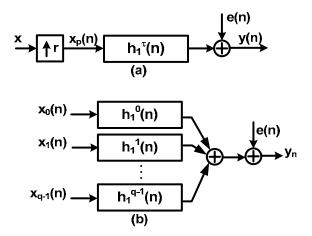

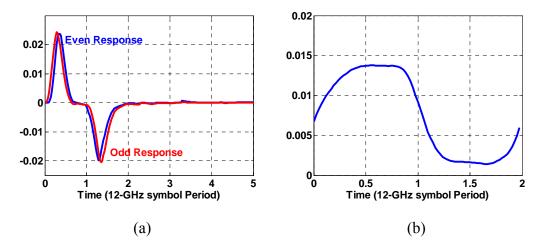

| FIGURE 6.5: (A) CTV SYSTEM MODEL FOR LINEAR TERM ESTIMATION $(H_1^{\tau}(N) = H_1^{\tau+Q}(N))$ , (B) EQUIVALENT |

| MODEL. $X_s(N)$ (0 $\leq$ s $<$ q $-1$ ) is a decimated version of the original sequence $X(N)$ , but every      |

| SUB-SEQUENCE IS DECIMATED AT A DIFFERENT OFFSET. 86                                                              |

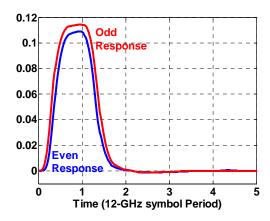

| FIGURE 6.6: 2-BIT DAC PULSE RESPONSES CORRESPONDING TO THE 2 INTERLEAVED PATHS,                                  |

| FIGURE 6.7: 2-BIT DAC (A) 3 <sup>RD</sup> ORDER NON-LINEARITY RESPONSES CORRESPONDING TO THE 2-PHASES (B)        |

| CYCLIC BIAS (DC-OFFSET AND CLOCK FEED-THROUGH)                                                                   |

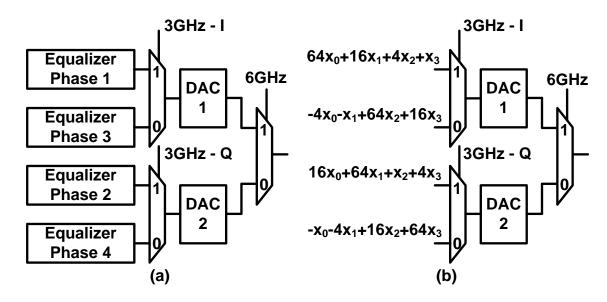

| FIGURE 6.8: (A) CONCEPTUAL TRANSMITTER ARCHITECTURE (B) EQUALIZER CONFIGURED TO CREATE A                         |

| WHITE INPUT FOR THE DAC THAT HITS EVERY DAC INPUT LEVEL                                                          |

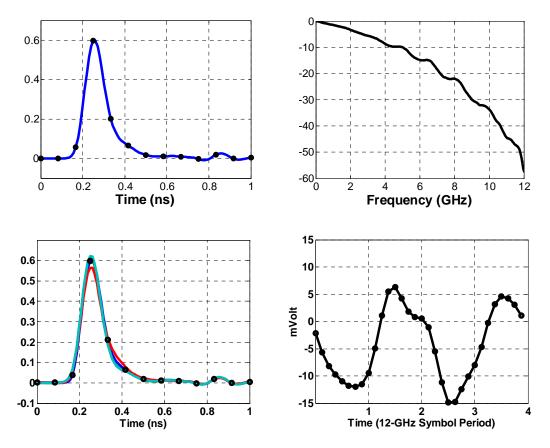

| FIGURE 6.9: DAC CHARACTERIZATION PLOTS BASED ON MEASURE DATA: (A) LTI PULSE RESPONSE, (B)                        |

| LTI Frequency response, (c) CTV pulse responses corresponding to the 4-phases of the                             |

| 4-WAY INTERLEAVED DAC, (D) CYCLO-STATIONARY CLOCK FEED-THROUGH AND NOISE PLUS DC                                 |

| OFFSET. 92                                                                                                       |

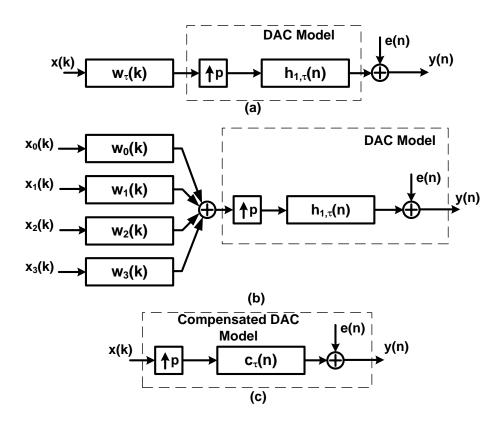

| FIGURE 6.10: (A) DAC PRECEDED BY A TIME-VARIANT EQUALIZER (B) EQUIVALENT MODEL WITH THE                          |

| TIME-VARIANT EQUALIZER EXPLICITLY SHOWN AS FOUR DISTINCT EQUALIZERS OPERATING ON                                 |