# AN ESTIMATION APPROACH TO CLOCK AND DATA RECOVERY

A DISSERTATION

#### SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING

#### AND THE COMMITTEE ON GRADUATE STUDIES

#### OF STANFORD UNIVERSITY

#### IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

#### FOR THE DEGREE OF

#### DOCTOR OF PHILOSOPHY

Hae-Chang Lee

November 2006

© Copyright by Hae-Chang Lee 2007 All Rights Reserved I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and quality, as dissertation for the degree of Doctor of Philosophy.

> Mark A. Horowitz (Principal Advisor)

I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and quality, as dissertation for the degree of Doctor of Philosophy.

Boris Murmann

I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and quality, as dissertation for the degree of Doctor of Philosophy.

Stefanos Sidiropoulos

Approved for the University Committee on Graduate Studies

iv

### Abstract

High speed I/O is used to increase the bandwidth between chips in a computer or network. The clock and data recovery (CDR) module is responsible for reconstructing the original transmitted bit-stream at the receiver. Until now, the CDR has been viewed as a feedback control system that adjusts its output clock according to the phase movement of the input data. However, there is another way to view the role of the clock recovery circuit. Viewing the CDR as an estimator of the phase position of the next bit rather than as a tracking loop allows one to rethink how a CDR should be designed. It gives one a physical intuition both of what order control loop is needed in conventional applications and of how to construct more complex non-linear control systems. The purpose of this research is to explore how the understanding of the CDR as a phase estimator can improve CDR performance in different applications.

To achieve this, a semi-digital dual loop CDR is modified to better estimate future phase for three applications. Matlab simulations and two test chips in 0.13µm and 0.25µm CMOS were implemented to quantify the improvement. By increasing the order of the loop filter to a second order, we have shown that the timing margin of the link is improved by more than 0.2 UI when a 200ppm frequency offset exists between the transmitter (TX) and receiver (RX). Using a second order CDR with very accurate frequency estimation, a burst mode receiver with zero lock time is made. This CDR can retain lock even when the packets are spaced apart by a million bits. Finally, a higher order estimator for systems using spread spectrum clocking can improve the timing margin by 0.05 UI in comparison to a second order CDR.

# Acknowledgments

I recall that my advisor, Mark Horowitz, read my final VLSI draft at 3am on the day of its submission (and in the same email asked me to call him in the next 30 minutes to discuss the changes). While impressive on its own merit, I found out after submission that he had been planning for his cancer surgery during the preceding days. I am fortunate to have had such a dedicated advisor.

I would also like to thank Prof. Boris Murmann for agreeing to be my associate advisor and serving on my reading committee. Dr. Stefanos Sidiropolous who gave much guidance during my work on spread spectrum systems has also graciously made time to read my thesis despite his duties running his company. I am also grateful to Prof. Saraswat who served as the chair for my oral defense on very short notice.

Former and current Horowitz group members have served as teachers as well as friends. Jaeha deserves special mention as he has been a great reference as I put together this thesis. Azita, Dean, Elad, Ken, Ron, Sam, and Vladimir have added tremendously to my engineering knowledge.

Rambus supported me during the last leg of my PhD. As I have now been a full-time employee for almost a year, I can honestly say that I am a lucky person who genuinely enjoys his work. Of course, work would not be enjoyable if it were not for great co-workers such as Jung Hoon, Brian, Yohan, Nhat, Bruno, Carl, and Jared.

I wish to thank MARCO for financial support of my research.

My parents and my brother have been a constant source of encouragement during the decade I have been at Stanford. I thank them for their tireless prayers on my behalf.

On account of my wife Rachel, I have matured socially as well as intellectually during my PhD. With the birth of our son, Isaac, I am even more indebted to her for the completion of this thesis.

This thesis, for all it is worth, is dedicated to my family.

# **Table of Contents**

| Abstract                                                                                                                     | v    |

|------------------------------------------------------------------------------------------------------------------------------|------|

| Acknowledgments                                                                                                              | vi   |

| Table of Contents                                                                                                            | viii |

| List of Figures                                                                                                              | X    |

| Chapter 1 Introduction                                                                                                       | 1    |

| <ul><li>1.1 CDR Overview</li><li>1.1.1 Deterministic Phase Offset Trajectory</li><li>1.1.2 Jitter</li></ul>                  |      |

| 1.2 Motivation                                                                                                               | 6    |

| 1.3 Organization                                                                                                             | 7    |

| Chapter 2 CDR Basics                                                                                                         | 9    |

| <ul> <li>2.1 Analog PLL based CDRs</li></ul>                                                                                 |      |

| 2.2 Semi-Digital Dual Loop CDR<br>2.2.1 Bang-Bang Phase Detector                                                             | 19   |

| 2.3 Summary                                                                                                                  |      |

| Chapter 3 Phase DAC Design                                                                                                   |      |

| 3.1 Link Overview                                                                                                            |      |

| <ul><li>3.2 Circuit Implementation</li></ul>                                                                                 |      |

| <ul> <li>3.2.3 Injection Locked VCO</li> <li>3.2.4 FSM and Lookup Table</li> <li>2.2.5 Phase Macaurement Circuits</li> </ul> |      |

| <ul><li>3.2.5 Phase Measurement Circuits.</li><li>3.2.6 High Speed Sampler</li></ul>                                         |      |

| 3.3 Measured Results                                                                                                         |      |

| 3.4 Summary                                                                                                                  |      |

| Chapter 4 Plesiochronous Systems                            |    |

|-------------------------------------------------------------|----|

| 4.1 Second Order Estimator                                  |    |

| 4.2 CDR Loop Dynamics                                       |    |

| 4.3 Performance Comparison using Jitter Tolerance           |    |

| 4.3.1 Test Chip                                             |    |

| 4.3.2 Jitter Tolerance                                      |    |

| 4.3.3 Measured Results                                      | 50 |

| 4.4 Summary                                                 | 56 |

| Chapter 5 Burst Mode Communications                         | 57 |

| 5.1 Background                                              | 57 |

| 5.1.1 TDM Optical Networks                                  |    |

| 5.1.2 Prior Art                                             | 59 |

| 5.2 Architecture                                            | 61 |

| 5.2.1 Quantization Noise                                    |    |

| 5.2.2 Jitter in TX and RX                                   |    |

| 5.2.3 Limit Cycles                                          |    |

| 5.2.4 Phase DAC Nonlinearity                                |    |

| 5.2.5 Acquisition Aid                                       |    |

| 5.3 Measurement Results                                     | 71 |

| 5.4 Summary                                                 | 75 |

| Chapter 6 Spread Spectrum Clocking                          | 76 |

| 6.1 Background                                              | 77 |

| 6.2 Performance of the Second Order CDR                     |    |

| 6.3 Estimator Design for SSC                                | 80 |

| 6.3.1 Third Order Estimator                                 |    |

| 6.3.2 Modulation Estimation using the Frequency Mean        | 81 |

| 6.3.3 Modulation Estimation using Frequency Differentiation |    |

| 6.3.4 Digital PLL for Modulation Estimation                 | 88 |

| 6.4 Measured Results                                        | 89 |

| 6.5 Summary                                                 |    |

| Chapter 7 Conclusions                                       |    |

| Bibliography                                                |    |

# **List of Figures**

| Figure 1.1: High speed link block diagram                                                                              |

|------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2: Example eye diagram from a sampling oscilloscope. Vertical axis is voltage                                 |

| and the horizontal axis is time                                                                                        |

| Figure 1.3: Systems with frequency offsets                                                                             |

| Figure 1.4: Phase offset trajectory of mesochronous and plesiochronous systems                                         |

| Figure 1.5: Time histogram on sampling scope demonstrating the two major categories of                                 |

| jitter – deterministic and random                                                                                      |

| Figure 2.1: Analog PLL based CDR                                                                                       |

| Figure 2.2: Linear Phase Detector (a) schematic and (b) transfer function                                              |

| Figure 2.3: Linear PLL model                                                                                           |

| Figure 2.4: Linear model for finding noise to phase estimation error transfer functions.                               |

| $\Phi_{n,in}$ is the jitter at the input. $V_{n,vco}$ is the device, supply, and substrate noise affecting             |

| the VCO frequency. The output of interest is the phase estimation error ( $\Phi_{ee}$ ) 16                             |

| Figure 2.5: Normalized transfer functions from $\Phi_{n,in}$ to $\Phi_{ee}$ and from $V_{n,vco}$ to $\Phi_{ee}$ . TD = |

| $0.5, K_{PD} = 1, K_P = 1, K_i = 0.005, Kvco = 1, and \zeta = 5$ in this example                                       |

| Figure 2.6: Normalized transfer function from $V_{n,vco}$ to $\Phi_{ee}$ for two different loop                        |

| bandwidths. Bandwidth is adjusted by changing $K_P = 1$ and $K_i = 0.005$ to $K_P = 4$ and                             |

| $K_i = 0.08$ . $\zeta = 5$ for both cases for fair comparison                                                          |

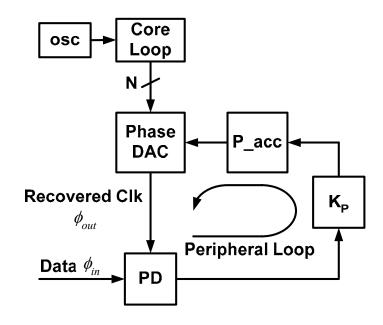

| Figure 2.7: Simplified block diagram of the semi-digital dual loop CDR 19                                              |

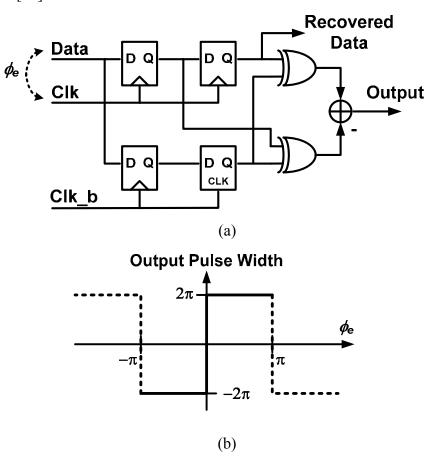

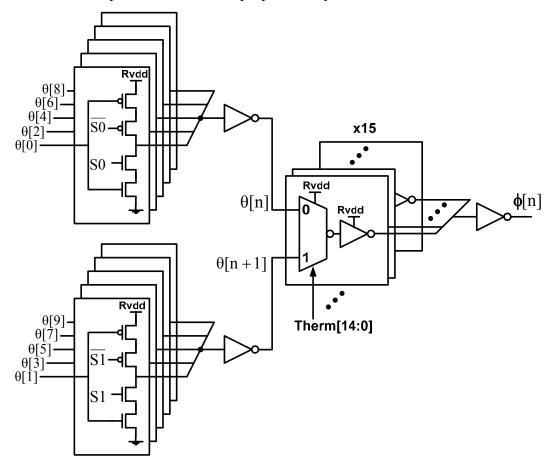

| Figure 2.8: Bang-bang phase detector (a) schematic and (b) transfer function                                           |

| Figure 2.9: Bang-bang phase detector operation                                                                         |

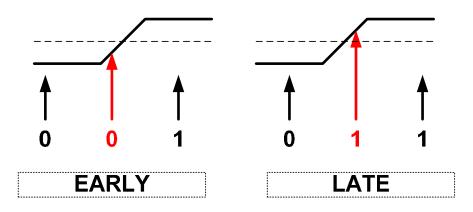

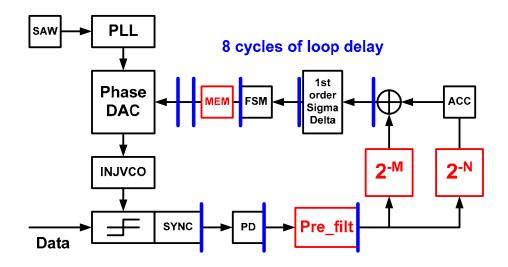

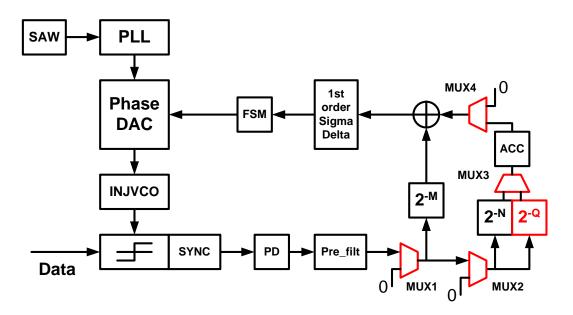

| Figure 3.1: Block diagram of the receiver for which this phase DAC is designed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

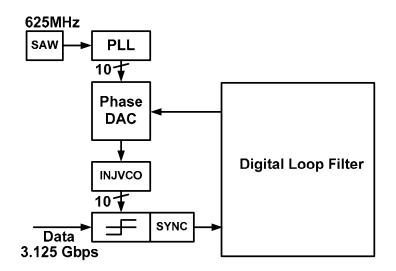

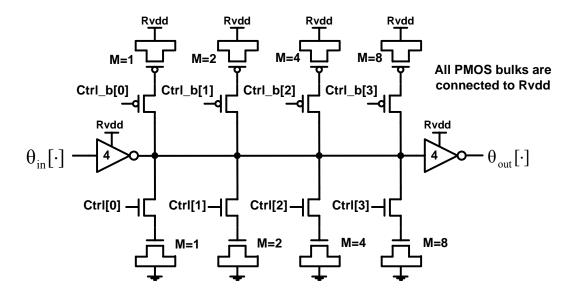

| Figure 3.2: Schematic of an adaptive bandwidth phase DAC using CMOS gates. Rvdd is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| the regulated supply that adjusts the component bandwidths to track the data rate. 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

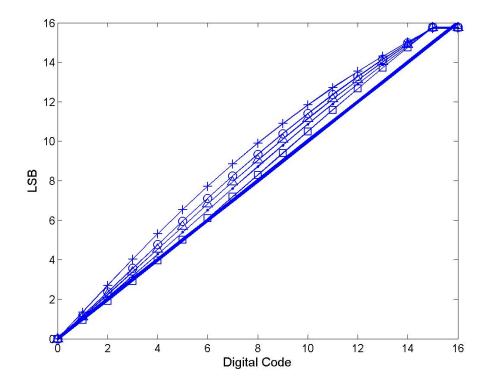

| Figure 3.3: Simulated phase DAC transfer function. The solid line is the ideal transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| function. Results are for five process corners (SS, SF, FS, FF, TT) and constant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| voltage (1.8V) and temperature (25°C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

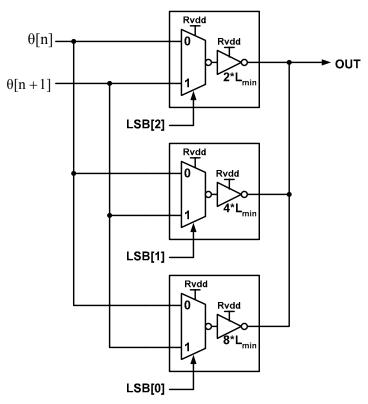

| Figure 3.4: Binary weighted interpolator legs to increase the resolution eight-fold 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

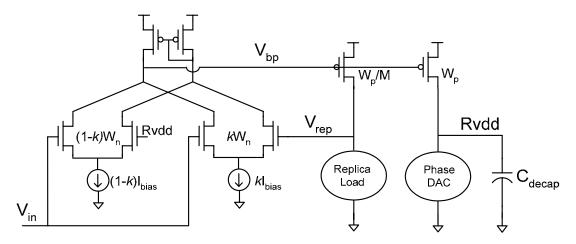

| Figure 3.5: Replica compensated linear regulator of [63]. $V_{in}$ is the control voltage of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PLL. M=32 and <i>k</i> =0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

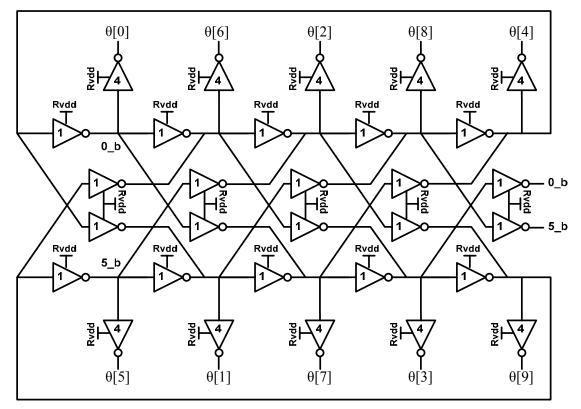

| Figure 3.6: Forward interpolating coupled ring oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 3.7: Circuit for correcting phase offsets of the VCO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

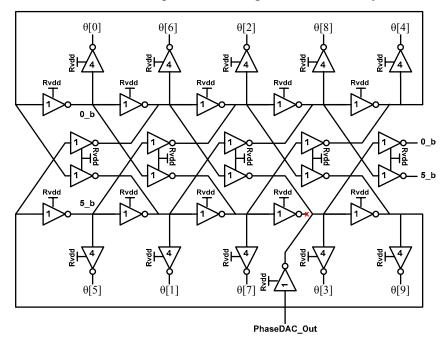

| Figure 3.8: Injection locked VCO for re-generating 10 phases from the single phase DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

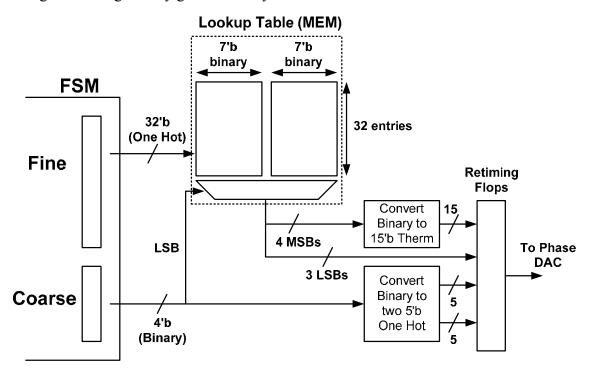

| Figure 3.9: Interface circuits between the FSM and the phase DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 3.10: On-chip phase measurement circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

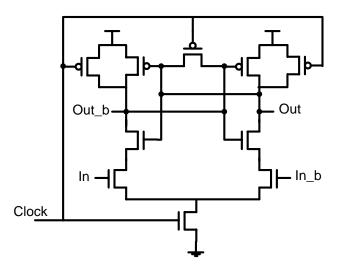

| Figure 3.11: High speed sampler used in RX front-end and on-chip measurement circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 3.11: High speed sampler used in RX front-end and on-chip measurement circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

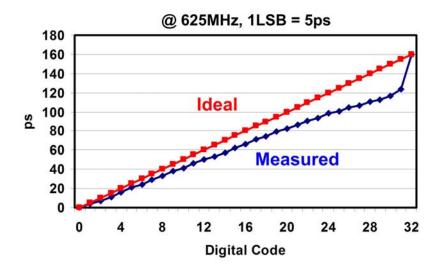

| Figure 3.12: Measured phase DAC transfer function. 32 steps span half of a UI. The other                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 36<br>Figure 3.12: Measured phase DAC transfer function. 32 steps span half of a UI. The other<br>half turned out to be almost symmetric and hence is not shown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 36<br>Figure 3.12: Measured phase DAC transfer function. 32 steps span half of a UI. The other<br>half turned out to be almost symmetric and hence is not shown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <ul> <li>36</li> <li>Figure 3.12: Measured phase DAC transfer function. 32 steps span half of a UI. The other half turned out to be almost symmetric and hence is not shown</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 36<br>Figure 3.12: Measured phase DAC transfer function. 32 steps span half of a UI. The other<br>half turned out to be almost symmetric and hence is not shown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <ul> <li>36</li> <li>Figure 3.12: Measured phase DAC transfer function. 32 steps span half of a UI. The other half turned out to be almost symmetric and hence is not shown</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <ul> <li>36</li> <li>Figure 3.12: Measured phase DAC transfer function. 32 steps span half of a UI. The other half turned out to be almost symmetric and hence is not shown</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

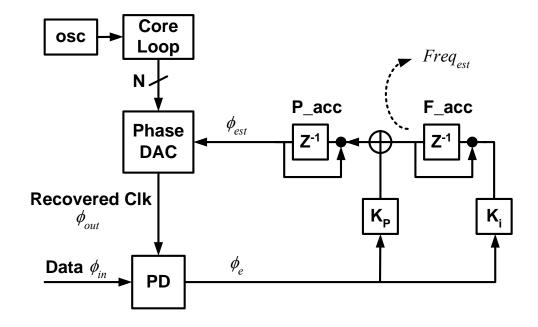

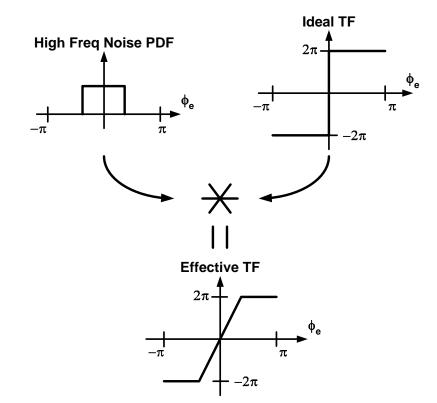

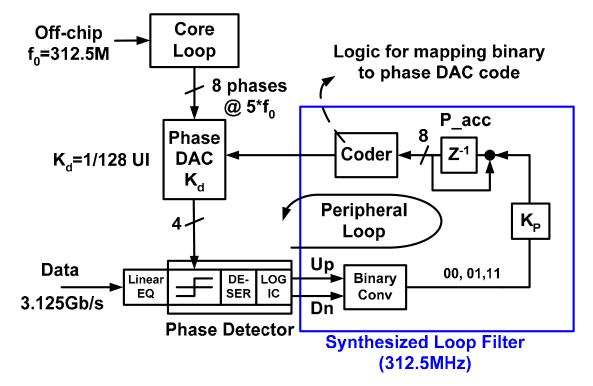

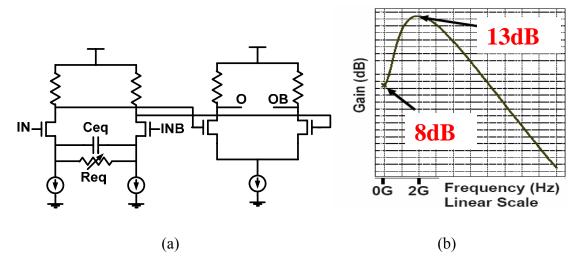

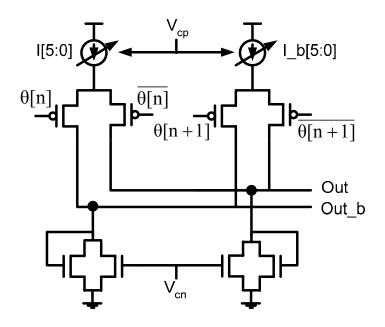

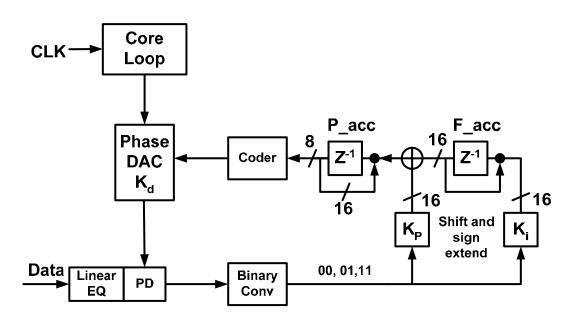

| 36         Figure 3.12: Measured phase DAC transfer function. 32 steps span half of a UI. The other half turned out to be almost symmetric and hence is not shown.       37         Figure 4.1: Simplified block diagram of the second order dual loop CDR.       41         Figure 4.2: Effective transfer function of the bang-bang PD in the presence of high frequency jitter. This example uses a noise PDF that is uniform.       43         Figure 4.3: RX with a first order CDR that was fabricated.       45         Figure 4.4: Circuit schematic of linear equalizer and its simulated transfer function.       46         Figure 4.5: Circuit schematic of phase DAC.       47                                                                                                                        |

| 36         Figure 3.12: Measured phase DAC transfer function. 32 steps span half of a UI. The other half turned out to be almost symmetric and hence is not shown.       37         Figure 4.1: Simplified block diagram of the second order dual loop CDR.       41         Figure 4.2: Effective transfer function of the bang-bang PD in the presence of high frequency jitter. This example uses a noise PDF that is uniform.       43         Figure 4.3: RX with a first order CDR that was fabricated.       45         Figure 4.4: Circuit schematic of linear equalizer and its simulated transfer function.       46         Figure 4.5: Circuit schematic of phase DAC.       47         Figure 4.6: RX with a second order CDR that was fabricated.       48                                           |

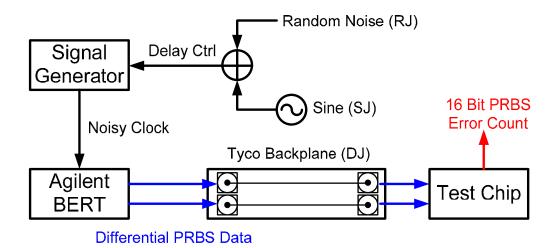

| 36         Figure 3.12: Measured phase DAC transfer function. 32 steps span half of a UI. The other half turned out to be almost symmetric and hence is not shown.       37         Figure 4.1: Simplified block diagram of the second order dual loop CDR.       41         Figure 4.2: Effective transfer function of the bang-bang PD in the presence of high frequency jitter. This example uses a noise PDF that is uniform.       43         Figure 4.3: RX with a first order CDR that was fabricated.       45         Figure 4.4: Circuit schematic of linear equalizer and its simulated transfer function.       46         Figure 4.6: RX with a second order CDR that was fabricated.       48         Figure 4.7: Test setup for JTOL measurement. Random and sinusoidal jitter is added by       48 |

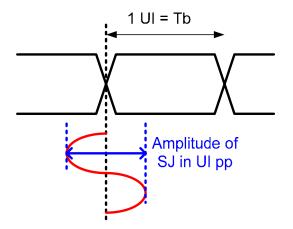

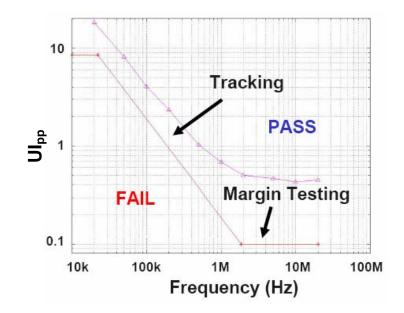

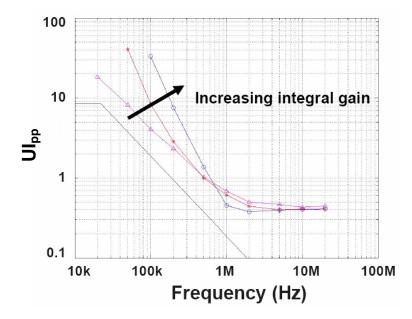

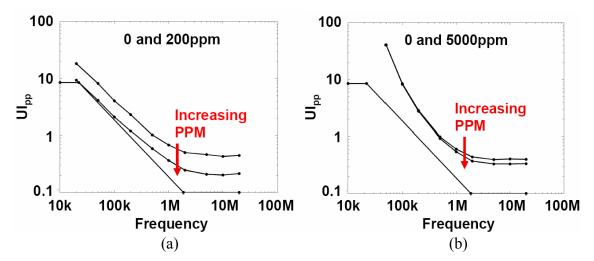

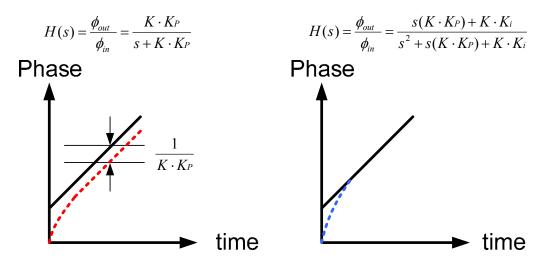

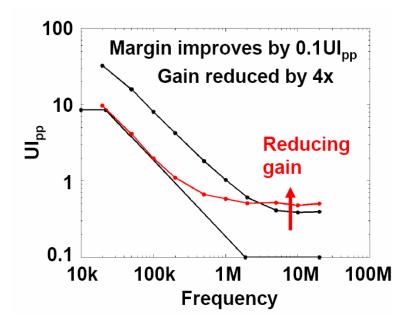

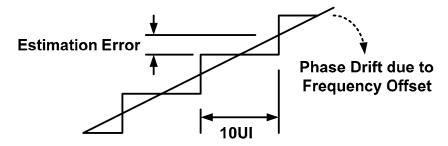

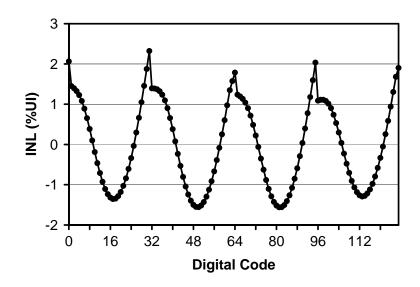

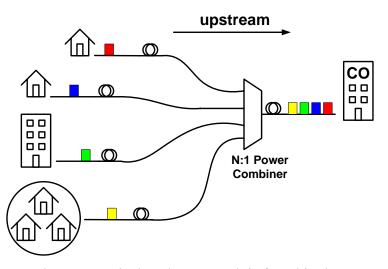

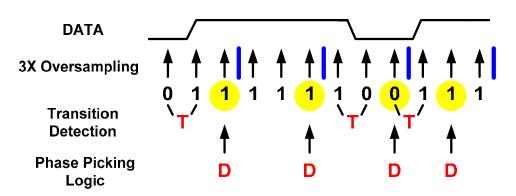

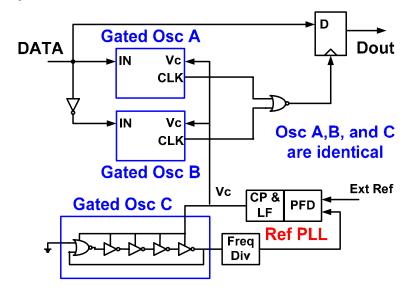

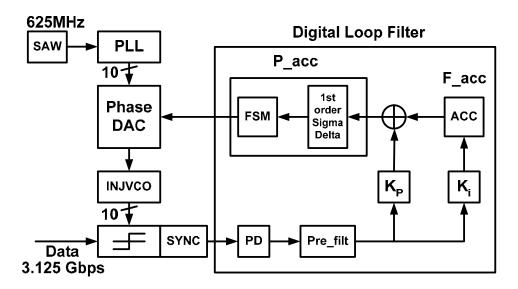

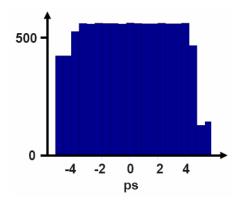

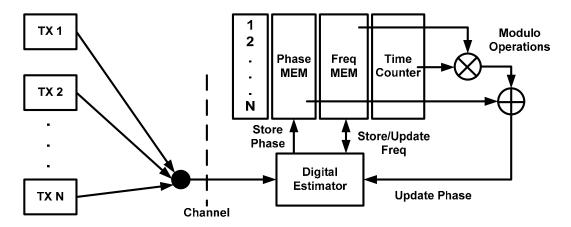

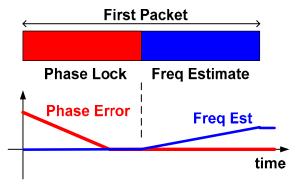

Figure 4.9: Example JTOL plot shown is for the first order CDR. JTOL has two regions that test the timing margin of the link and the CDR's tracking performance. The xaxis is the SJ frequency in Hz. The y-axis is the peak-to-peak SJ amplitude in  $UI_{pp}$ . Figure 4.10: JTOL with varying integral gain. The three curves are for  $K_i = (0, 1/512, 1/512)$ Figure 4.11: Measured JTOL with different frequency offsets for (a) first order CDR and (b) second order CDR.  $K_P = 0.5$  for both CDRs.  $K_i = 1/256$  for the second order Figure 4.12: Steady state phase estimation error in the first order and second order CDRs when a frequency offset exists. Here,  $K = K_D \cdot K_{PD} \cdot TD$  in the expressions for the equivalent linear transfer functions. The first order CDR has a steady state error that is inversely proportional to its bandwidth. The second order CDR has no steady state Figure 4.13: JTOL with varying  $K_P$  (1 and 0.25) in the first order CDR. The timing margin improves with the reduction in loop gain / bandwidth due to the increased Figure 5.1: An example TDM optical packet network is found in the upstream of FTTH. Figure 5.2: Conceptual view of the oversampling receiver. This example is for 3x Figure 5.4: The second order dual loop CDR core of the burst mode packet receiver..... 62 Figure 5.5: The 8 cycles of delay in the CDR feedback loop. Each delay is marked with a blue bar. Two delays are incurred by the offset correction memory and its decoder. Figure 5.6: Jitter histogram from simulation showing the limit cycle of the second order CDR with  $K_P=1$ ,  $K_i=2^{-20}$ , D=8,  $K_D=1/64$ , and  $T_S=3.2$ ns. Pre filt gain is set to 1/8.

| Figure 5.7: Complete burst mode receiver leveraging a high accuracy digital phase and   |

|-----------------------------------------------------------------------------------------|

| frequency estimator                                                                     |

| Figure 5.8: Sub-division of first packet to enhance the lock range. The first half is   |

| allocated for the RX to obtain phase lock while the second half is used to obtain a     |

| fast but coarse frequency offset estimate                                               |

| Figure 5.9: Modifications to the CDR to enhance the lock range in packet mode           |

| operation                                                                               |

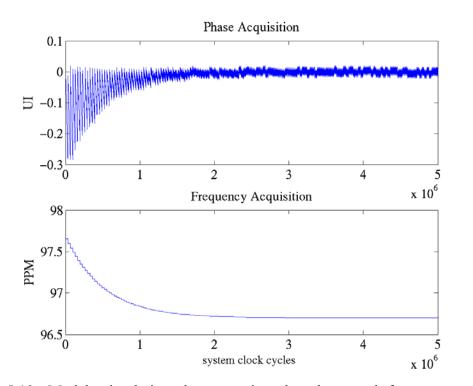

| Figure 5.10: Matlab simulation demonstrating the phase and frequency acquisition        |

| behavior of the second order CDR in the presence of packets. The packets were 10k       |

| bits long with 320k bit spacing in between. The time axis is in digital clock cycles    |

| whose frequency is one tenth the data rate                                              |

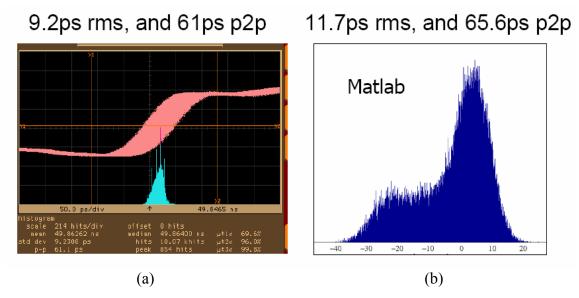

| Figure 5.11: (a) Measured and (b) simulated phase estimation error in the presence of   |

| PRBS data (2 <sup>10</sup> -1)                                                          |

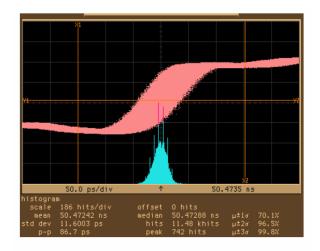

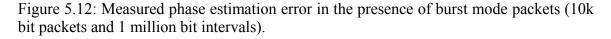

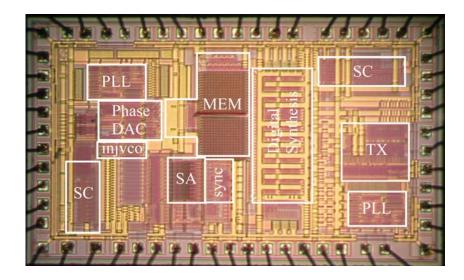

| Figure 5.12: Measured phase estimation error in the presence of burst mode packets (10k |

| bit packets and 1 million bit intervals)                                                |

| Figure 5.13: (a) Measurement setup for oscillator stability and (b) the measured        |

| frequency stability of a commercial SAW oscillator (Epson EG2102) at 7.6 sec            |

| intervals74                                                                             |

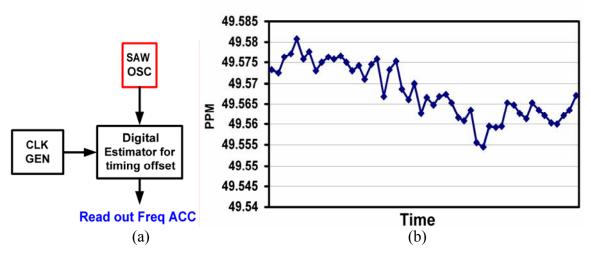

| Figure 5.14: Die photo of test chip                                                     |

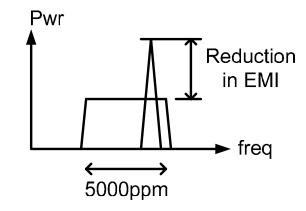

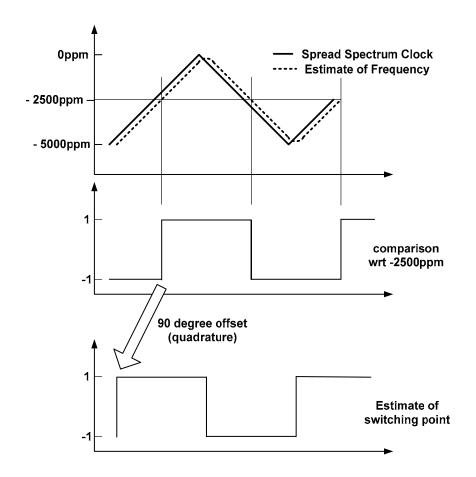

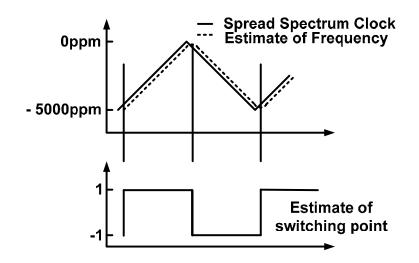

| Figure 6.1: Frequency domain view of SSC                                                |

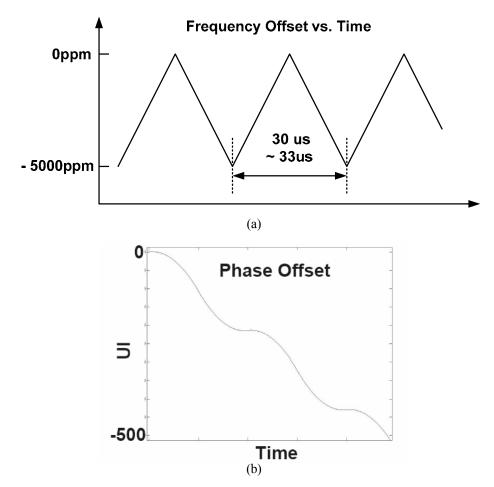

| Figure 6.2: Time domain view of an example SSC. (a) Frequency offset and (b) phase      |

| offset between the TX and RX vs. time                                                   |

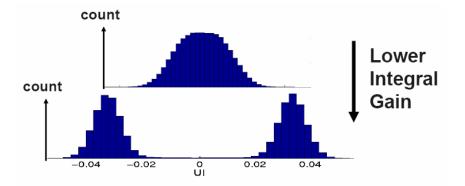

| Figure 6.3: Histogram of the phase estimation error for the second order CDR tracking   |

| data from a TX using SSC. Results are from Matlab simulations. The integral gain is     |

| reduced by four times                                                                   |

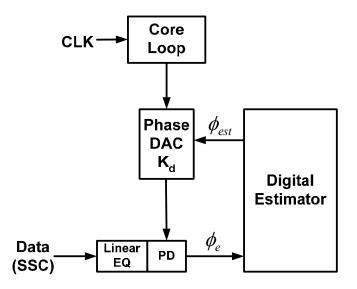

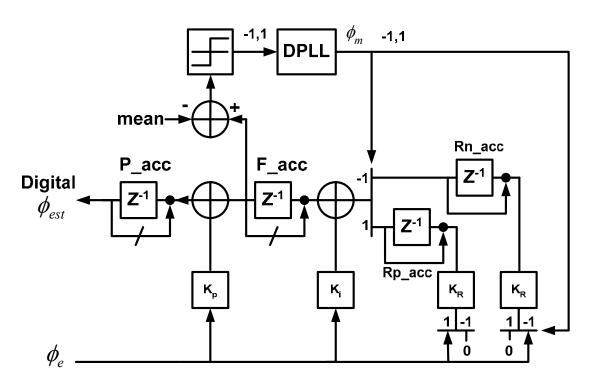

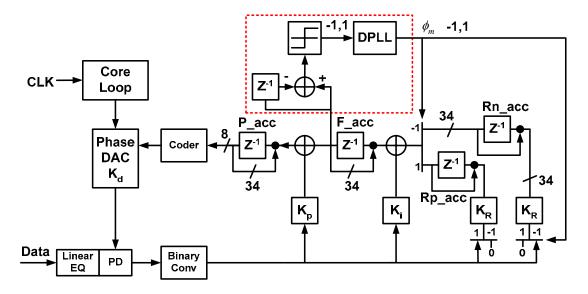

| Figure 6.4: Semi-digital dual loop architecture used in this chapter                    |

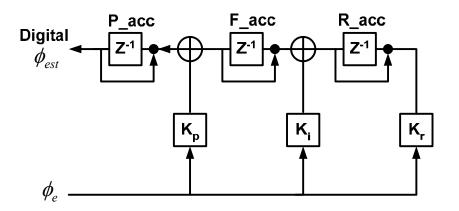

| Figure 6.5: Third order estimator which acquires the phase, frequency, and frequency    |

| ramp rate of the TX data with respect to the RX clock                                   |

| Figure 6.6: Graphical view of modulation estimation by comparing the frequency          |

| estimate with its mean                                                                  |

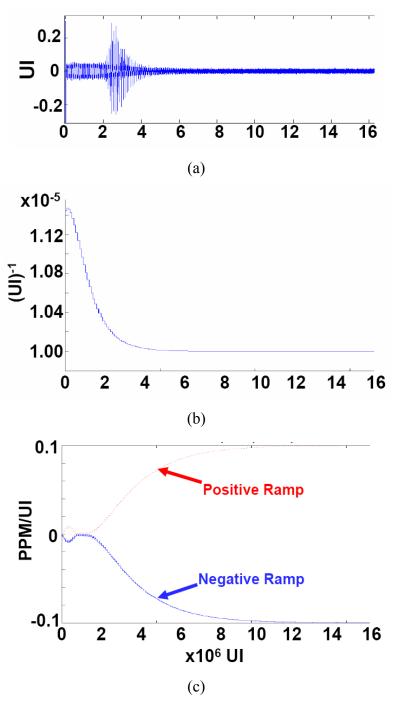

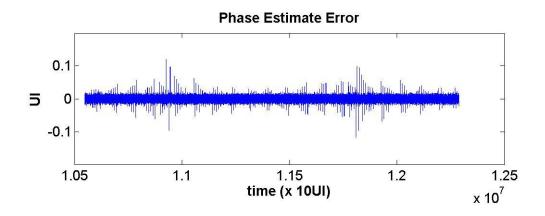

| <ul> <li>information</li></ul>                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (a) phase estimate error, (b) estimated modulation frequency, and (c) estimated<br>frequency ramp rate vs. time. The gains used are $K_P=1/2^3$ , $K_i=1/2^9$ , $K_R=1/2^{29}$ ,<br>$K_{MP}=1/2^{15}$ , and $K_{MI}=1/2^{32}$ . Phase DAC has 128 steps per UI                      |

| frequency ramp rate vs. time. The gains used are $K_P=1/2^3$ , $K_i=1/2^9$ , $K_R=1/2^{29}$ , $K_{MP}=1/2^{15}$ , and $K_{MI}=1/2^{32}$ . Phase DAC has 128 steps per UI                                                                                                            |

| $K_{MP}=1/2^{15}$ , and $K_{MI}=1/2^{32}$ . Phase DAC has 128 steps per UI                                                                                                                                                                                                          |

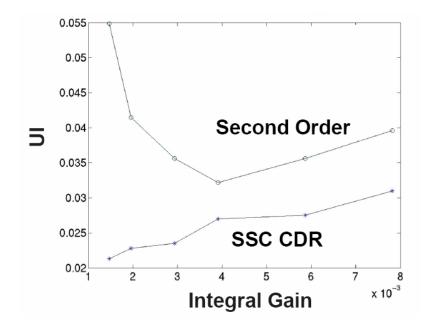

| Figure 6.9: Comparison of the peak phase estimation error (UI) for the second order and SSC estimators when tracking data from a TX using SSC. Results are from Matlab simulations. $K_P=1/2^3$ for both estimators. $K_R=1/2^{29}$ , $K_{MP}=1/2^{15}$ , and $K_{MI}=1/2^{32}$ for |

| SSC estimators when tracking data from a TX using SSC. Results are from Matlab simulations. $K_P=1/2^3$ for both estimators. $K_R=1/2^{29}$ , $K_{MP}=1/2^{15}$ , and $K_{MI}=1/2^{32}$ for                                                                                         |

| simulations. $K_P=1/2^3$ for both estimators. $K_R=1/2^{29}$ , $K_{MP}=1/2^{15}$ , and $K_{MI}=1/2^{32}$ for                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                     |

| the SSC estimator. Phase DAC has 128 steps per UI. Random jitter $\sigma$ is 0.0214 UI.                                                                                                                                                                                             |

| The peak error is that observed in 16e6 bits                                                                                                                                                                                                                                        |

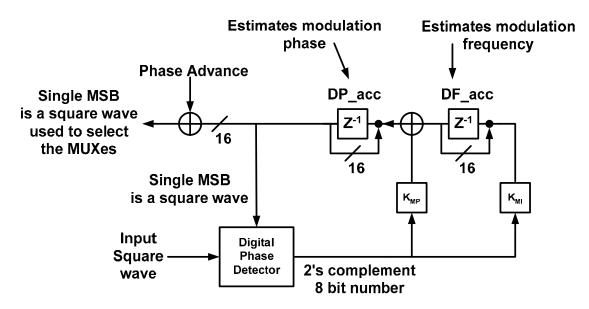

| Figure 6.10: Graphical view of modulation estimation by differentiating the frequency                                                                                                                                                                                               |

| estimate                                                                                                                                                                                                                                                                            |

| Figure 6.11: SSC estimator using the derivative of the frequency estimate to perform the                                                                                                                                                                                            |

| modulation estimation. Each of the gains can be programmed over a range of 16x.87                                                                                                                                                                                                   |

| Figure 6.12: Phase estimate error beating due to the interaction of the quantization error                                                                                                                                                                                          |

| of multiple loops. Results are from Matlab simulations. $K_P=1/2^3$ , $K_i=1/2^9$ , $K_R=1/2^{29}$ ,                                                                                                                                                                                |

| $K_{MP}=1/2^8$ , and $K_{MI}=1/2^{16}$ . Phase DAC has 128 steps per UI. Random jitter $\sigma$ is                                                                                                                                                                                  |

| 0.0214 UI. The peak error is about 0.12 UI                                                                                                                                                                                                                                          |

| Figure 6.13: DPLL used in the modulation estimation. $K_{MP}$ is its proportional gain and                                                                                                                                                                                          |

| K <sub>MI</sub> is its integral gain                                                                                                                                                                                                                                                |

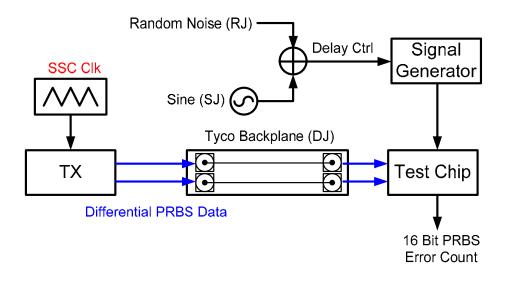

| Figure 6.14: Test setup for measuring the timing margin of the SSC and second order                                                                                                                                                                                                 |

| estimators                                                                                                                                                                                                                                                                          |

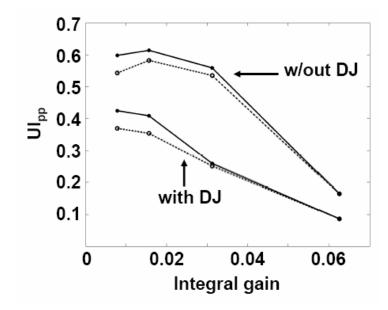

| Figure 6.15: Timing margin vs. integral gain. TX is using a SSC clock. Second order                                                                                                                                                                                                 |

| CDR (dotted, °) and SSC estimator (solid, *). The timing margin is measured at a                                                                                                                                                                                                    |

| BER of $10^{-11}$ . K <sub>P</sub> =1, K <sub>R</sub> = $1/2^{26}$ , K <sub>MP</sub> = $1/2^8$ , and K <sub>MI</sub> = $1/2^{16}$ . Phase DAC has 128 steps                                                                                                                         |

| per UI                                                                                                                                                                                                                                                                              |

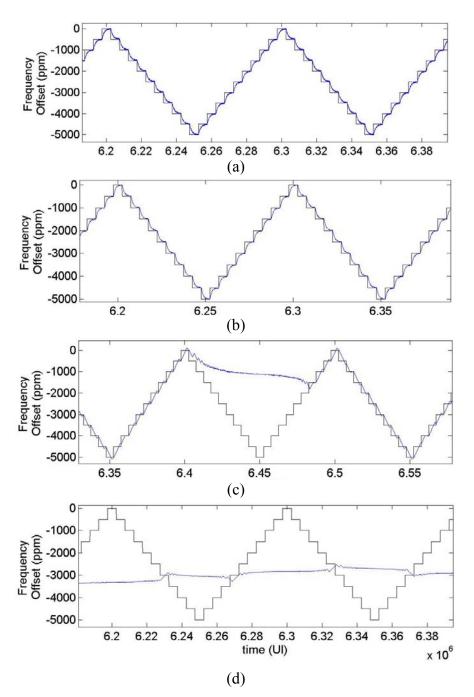

| Figure 6.16: Time domain tracking behavior of the second order CDR in the presence of                                                                                                                                                                                               |

| a staircase SSC that would result from a fractional-N PLL. The frequency step size                                                                                                                                                                                                  |

| is 500ppm. Random jitter $\sigma$ is 0.0214 UI. Phase DAC has 128 steps per UI. K <sub>P</sub> =1                                                                                                                                                                                   |

| and $K_i = 1/2^7$ for (a). Both gains are decreased by a factor of two for each successive | ve |

|--------------------------------------------------------------------------------------------|----|

| plot. The CDR operates only at $K_P = 1$ and $1/2$ .                                       | 92 |

# **Chapter 1**

## Introduction

Technology scaling has dramatically increased the amount of computation that can be integrated onto a small piece of silicon. This increased computation has highlighted the need for chip I/O that can supply the needed information fast enough to keep the compute engine fed. As a result, the design of chip I/O has become increasingly sophisticated, with multi-Gb/s bandwidths now prevalent in high performance computer systems and networks.

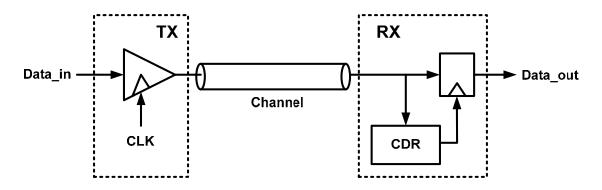

These high speed links are composed of a transmitter (TX) and a receiver (RX) communicating over a channel, as shown in Figure 1.1. The blocks must first generate and receive a high bandwidth signal. Then the RX must reconstruct the original transmitted bitstream from the received waveform. The first task spans a wide area of disciplines including channel design [1, 2], package design [9-11], signaling methods (e.g. PAM [3-5]), and equalization [6-8]. The second task is clock and data recovery (CDR), which is the subject of this thesis.

Figure 1.1: High speed link block diagram.

### **1.1 CDR Overview**

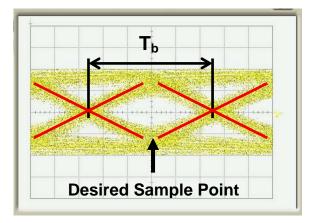

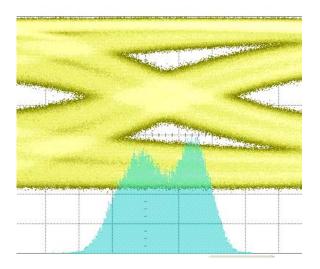

An eye diagram, which is created by overlaying consecutive bits onto a single bit time  $(T_b)$ , is useful in explaining the function of a CDR (Figure 1.2). The 'eye' shape is created by the four possible transitions which are marked with straight lines in Figure 1.2. The first is when the previous bit is high and the current bit is low. The second transition is when the previous bit is low and the current bit is high. The third is when the current bit is low. The second transition due to the next bit is low. The last transition occurs when the current bit is low and the next bit is high. The first two transitions form the left half of the eye. The latter two transitions form the right half. The actual transitions have uncertainty caused by timing and voltage noise in the system. This causes the transitions to appear thick and blurry in the eye diagram.

Figure 1.2: Example eye diagram from a sampling oscilloscope. Vertical axis is voltage and the horizontal axis is time.

The objective of the CDR is to recover the data with as few errors as possible. In other words, the goal of the CDR is to minimize the bit error rate (BER) through the channel. To achieve minimum BER, the CDR needs to sample the data where the eye opening is largest. This point ("Desired Sample Point") has the highest signal to noise ratio (SNR) which is in turn the point with the lowest BER. Equation (1.1) governs this relationship for binary signals with additive white Gaussian voltage noise, where erfc(.) denotes the complementary error function [12]. The BER decreases rapidly as the SNR is increased.

$$BER = \frac{1}{2} \operatorname{erfc}(\frac{SNR}{2\sqrt{2}}) \tag{1.1}$$

As seen in Figure 1.2, there is a high correlation between the maximum eye opening and the midpoint between the transition crossings. Hence, CDRs are often designed to sample the data half a bit time away from its estimate of where the data transitions are occurring. In the rare case that the data eye is asymmetric, this will not be the best solution, but in most cases it is an efficient way of getting very close to it. Due to this approximation, the CDR needs to recover the clock that is embedded in the data transitions to use it as its reference in sampling the data.

What complicates CDR design is that the data transitions are not stationary with respect to a timing reference. There are two reasons for this movement. The first is due to any deterministic phase offset trajectory that is a result of frequency offsets between the TX and RX reference clocks. The second is due to timing uncertainty or noise that is referred to as jitter. These will be explained next.

#### **1.1.1 Deterministic Phase Offset Trajectory**

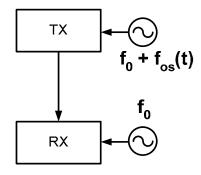

Frequency offsets exist between the TX and RX when each side of the link has its own independent clock source, such as a crystal or SAW oscillator, that are nominally but not exactly identical in frequency (Figure 1.3). This frequency offset does not have to be a constant but can be a periodic function in time. This causes the phase offset between the

data transitions from the TX and the edges of the clock to the RX to change in a deterministic and predictable manner.

Figure 1.3: Systems with frequency offsets.

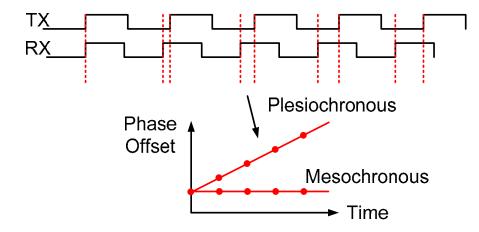

The degenerate case is when the average offset in frequency is zero. Such systems are called mesochronous and occur when a global frequency source is shared between all the parties involved. In this situation, the phase offset between the TX and RX is a constant over time (Figure 1.4). A more interesting case is when the frequency offset is a constant. These systems are called plesiochronous. The edges of the clock to the TX (and hence the timing of the data transitions) diverge in a linear fashion with respect to the edges of the clock to the RX (Figure 1.4). The phase offset trajectory is found by plotting the phase difference between the data transitions and the reference clock to the RX versus time. For plesiochronous systems, the phase offset trajectory is a linear ramp with the ramp rate set by the magnitude of the frequency offset.

Figure 1.4: Phase offset trajectory of mesochronous and plesiochronous systems.

We have introduced two common clocking systems and their phase offset trajectories. As we will see later, more sophisticated clock schemes have arisen due to electromagnetic interference (EMI) concerns in recent years [13]. The result is a more complex, but still very much deterministic and predictable, phase offset trajectory. For the purposes of CDR design, such deterministic phase offset trajectories must be tracked as accurately as possible.

#### **1.1.2 Jitter**

Jitter refers to the uncertainty in the phase of clock (and hence data) edges. There are two categories of jitter – deterministic jitter (DJ) and random jitter (RJ). DJ has bounded statistics while RJ has unbounded Gaussian statistics.<sup>1</sup> These two categories of jitter are demonstrated in Figure 1.5 where the unbounded tail at either side of the time domain histogram results from RJ while the two distinct peaks are due to DJ.

Figure 1.5: Time histogram on sampling scope demonstrating the two major categories of jitter – deterministic and random.

There are three common types of DJ found in real systems: data dependent jitter (a.k.a intersymbol interference or ISI), duty cycle distortion (DCD), and uncorrelated (to the data) bounded jitter such as supply noise induced jitter. In a well designed system, the dominant source of DJ is from ISI. RJ is most commonly caused by fundamental noise

<sup>&</sup>lt;sup>1</sup> Deterministic jitter (DJ) should not be confused with the deterministic phase offset trajectory. DJ and RJ are timing noise super-imposed onto the deterministic phase offset trajectory.

sources of both active and passive devices (such as thermal noise). Most of these jitter components including ISI and RJ show little correlation over time.

The job of the CDR designer is to filter and not attempt to track these uncorrelated jitter sources since their past behavior sheds little light on the position of future transitions.

### **1.2 Motivation**

In general, the CDR has been viewed as a feedback control system that adjusts its output clock phase in response to phase movements of the data. While the deterministic phase offset trajectory and jitter have very different properties, they are often lumped together as timing disturbances. CDR design is complicated as its bandwidth must be optimized between tracking the phase trajectory and filtering uncorrelated jitter such as ISI.

I will show in this thesis that viewing the CDR as an estimator of the phase position of the next data transition rather than as a tracking loop allows us to directly address the different design requirements resulting from the phase offset trajectory and jitter. In answering the question "What should my CDR look like in order for it to predict the behavior of the TX in the future?" we can obtain insight into the optimal structure of the CDR for a given application that will provide independent means for tracking the phase offset trajectory while optimizing the bandwidth for jitter.

How this understanding of the CDR as a phase estimator can be applied beneficially to different application will be demonstrated using the following three applications: systems with a fixed frequency offset between the TX and RX (plesiochronous systems), burst mode communication where the frequency offset is compounded by an extremely low transition density, and systems with complex patterns in the frequency offset such as spread spectrum clocking.

### **1.3 Organization**

This chapter provided an introduction on the objective of CDR design and the various design considerations that must be addressed. We have identified the deterministic phase offset trajectory along with jitter as the primary design consideration for a CDR.

Chapter 2 will first review analog phase-locked loops (PLL) which are the most commonly used CDR architecture. This chapter will then discuss critical component and system properties like transfer function and stability that are of interest to the designer. Finally, we will motivate the architecture chosen to demonstrate phase estimator design - the semi-digital dual loop CDR – by analyzing the noise performance of the analog PLL CDR.

For the semi-digital dual loop CDR, estimator performance is dependent on the linearity of the phase domain digital-to-analog converter (Phase DAC). Chapter 3 will detail the circuits of a high precision phase DAC as well as measured results.

Chapter 4 demonstrates the advantages of building a phase estimator for systems with a fixed frequency offset between the transmitter and receiver. We will show how a second order CDR can improve performance over a first order CDR in the presence of a frequency offset using jitter tolerance as a metric. It will be shown that the reason the second order CDR performs better is because it has the capacity to predict the movement of the data transitions (the deterministic phase offset trajectory) caused by the frequency offset.

Chapter 5 uses burst mode communication to show how an estimation perspective can change the design of the CDR. Burst mode systems arise when multiple transmitters and receivers share a common channel – typically optical fiber – via time division multiplexing (TDM). In these systems, the duration of time between two packets arriving from the same transmitter to a receiver can be very long. Since CDRs were viewed as tracking loops, past efforts to address this absence of timing information focused on building systems that tried to reacquire phase lock as quickly as possible. However, taking an estimation approach leads us to build a CDR that predicts the phase of future packets by obtaining very accurate phase and frequency estimates of each TX. Such a

system can retain lock even if packets are separated by hundreds of thousands of bits and thus achieve zero lock time.

The idea of creating a CDR that predicts future phase position is extended in Chapter 6 for links that use spread spectrum clocking. Spread spectrum clocking is used in wireline communication in order to reduce electro-magnetic interference (EMI). One common implementation of spread spectrum modulates the frequency of the TX with a triangular waveform. In order to make predictions on the timing of future bits, this system estimates all relevant parameters of the spread spectrum clock - i.e. phase, frequency, frequency ramp rate, modulation phase, and modulation frequency. Such a higher order estimator can decouple opposing constraints on the bandwidth of the CDR – namely the need for a large bandwidth to track the deterministic non-constant phase trajectory and the need for a low bandwidth to improve jitter filtering. The implementation of a lower bandwidth without compromising the ability of the CDR to correct the phase movement due to the spread spectrum clock improves the timing margin of this CDR over conventional designs.

## Chapter 2

## **CDR Basics**

This chapter will review the fundamentals of CDR design. The objectives of this chapter are two-fold. The first is to provide insight into what factors influence the dynamic behavior of the CDR. This will provide the foundation for understanding the material in later chapters. The second is to motivate the CDR architecture that was chosen to demonstrate phase estimator design in this thesis. Section 2.1 will first review analog phase locked loop (PLL) based CDRs which are the most prevalent in industry. This section will discuss critical component and system properties like transfer function and stability that are of interest to the designer. An analysis of the noise performance of the analog PLL CDR will provide motivation for the semi-digital dual loop architecture. Section 2.2 will then describe this architecture.

### 2.1 Analog PLL based CDRs

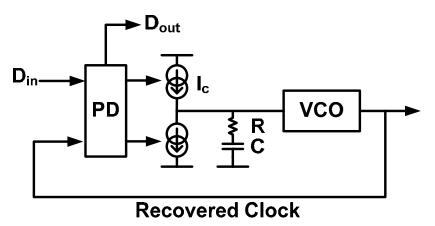

Due to the ever changing phase relationship between the data transitions and the RX clock, the RX needs to constantly adjust the time at which it samples the data. To do this, the CDR needs three major components. The phase detector (PD) is used to determine the phase relationship between the data transitions and its own clock domain. Second, a loop filter removes the noise in the phase detector output and sets the bandwidth of the PLL.

Finally, the voltage controlled oscillator (VCO) provides a method of adjusting the phase of a clock in order to optimally move it to the maximum eye opening of the data. Figure 2.1 is a CDR using a charge pump PLL [23].

Figure 2.1: Analog PLL based CDR.

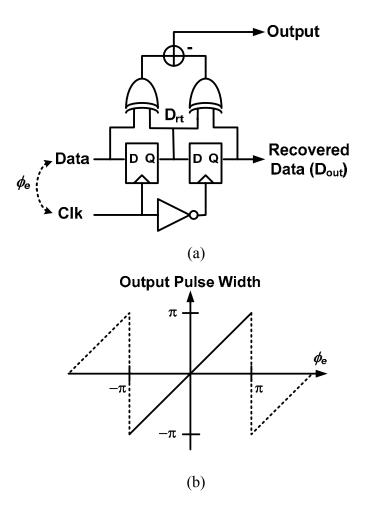

#### 2.1.1 Linear Phase Detector

The phase difference between clock domains is determined using a phase detector (PD). The most widely used linear PD was first published by Hogge [17]. Its schematic and transfer function are shown in Figure 2.2. The PD subtracts two pulses, each originating from an XOR gate. The subtraction is done indirectly by the charge pump. The XOR gate on the right generates a reference pulse that is exactly half a bit time in width. The XOR gate on the left generates a pulse whose width depends on the phase error between the edges of Data and the edges of D<sub>rt</sub>. When the phase difference between Data and D<sub>rt</sub> (and hence Clk) is half a bit, the two pulses cancel each other thus generating no change in the PD output. The linearity results from the net pulse width at the output being linearly proportional to the phase difference between the center of Data and the edges of Clk (Figure 2.2 (b)). The saw-tooth shape of the transfer function is due to phase being a modulo- $2\pi$  quantity. Phase detector gain (K<sub>PD</sub>) is defined as the slope of the transfer function where the phase error is close to zero. The phase detector gain is typically 1 and is unitless.<sup>2</sup>

<sup>&</sup>lt;sup>2</sup> The definition of the PD gain depends on the definition of the VCO gain. In this thesis, VCO gain has units of  $Hz \cdot V^{-1}$ . Alternately, it is common to define VCO gain in  $rad \cdot (sec \cdot V)^{-1}$ . In this case, the PD gain is  $(2\pi)^{-1}$  and has units of  $rad^{-1}$ .

Figure 2.2: Linear Phase Detector (a) schematic and (b) transfer function.

Linear PDs allow the designer to use linear systems theory in analyzing the inputoutput behavior of the PLL, such as 3-dB bandwidth and the amount of peaking in the transfer function. This can be a benefit when such parameters are defined by a specification such as Synchronous Optical Network (SONET) [15]. Additional advantages include low complexity and low power consumption.

There are several drawbacks to this PD. First, this PD requires conditioning on the swing and duty cycle of the input data via a limiting amplifier. Second, the maximum rate of operation is limited by the intrinsic speed of the flip-flops in current mode logic (CML) and the XOR gate in CMOS. The adaptation of this phase detector for multiphase operation, a common method of overcoming fundamental circuit speed limitations, is not straight forward [21]. Third, the average PD output when the phase error is zero differs between the case when the input data pattern is a long train of 1's or 0's, referred

to as consecutive identical digits (CID), and when the input is a clock pattern. This in turn causes the average PD output to be pattern dependent which results in data dependent jitter. Designers have addressed this problem but have done so with a significant increase (about twice) the hardware [18-19]. Fourth, the linear PD's analog output necessitates a sigma-delta ADC to make it usable in digital CDRs that are gaining increased interest due to the leakage current in on-chip capacitors as well as the reluctant scaling of analog circuits [20]. Finally and most importantly, the edges of Data do not experience the same clk-q delay seen by D<sub>rt</sub> and D<sub>out</sub>. This clk-q delay mismatch causes a phase offset between Clk and the center of the Data in steady state. Hogge recognized this problem and proposed the insertion of a delay on Data to provide a replica of the clk-q delay. Unfortunately, this is an imperfect solution that is affected by process, voltage, and temperature (PVT) variations. Nonetheless, the linear transfer characteristic of this PD compensates for these shortcomings in certain applications leading to its apparent popularity.

#### 2.1.2 PLL Loop Dynamics

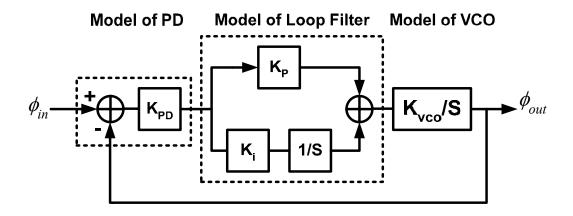

Figure 2.3 shows the linear continuous-time model of an analog PLL. We assume for now that the input is a clock pattern. The notable difference to Figure 2.1 is that the charge pump and RC network have been replaced with two branches (proportional and integral) that are summed in parallel [24]. The equivalence of these seemingly different structures will be shown later. The linear model only applies when the phase error between the input data and the recovered clock is small. The acquisition behavior of PLLs is a nonlinear phenomenon that cannot be predicted using this model. Furthermore, the continuous time model requires that the sampling frequency (i.e. the recovered clock frequency) be much larger than the bandwidth of the loop itself. This assumption allows one to ignore the discrete sampling effects and hence apply the Laplace transform [23].

Figure 2.3: Linear PLL model.

The transfer function of the linear PLL has two poles and a zero. The gain of the VCO (Kvco) represents the conversion factor from voltage at its input to a frequency at its output. Hence, its units are in  $Hz \cdot V^{-1}$ .  $K_{PD}$  is unitless, the proportional gain ( $K_P$ ) is in V, and the integral gain ( $K_i$ ) is in V·sec<sup>-1</sup>.

$$\frac{\phi_{out}}{\phi_{in}} = \frac{s \cdot K_P \cdot K_{PD} \cdot K_{VCO} + K_i \cdot K_{PD} \cdot K_{VCO}}{s^2 + s \cdot K_P \cdot K_{PD} \cdot K_{VCO} + K_i \cdot K_{PD} \cdot K_{VCO}}$$

(2.1)

The transfer function of the PLL in Figure 2.1 is exactly in the form of (2.1) when we make the following substitutions for  $K_P$  and  $K_i$ .  $I_C$  is the charge pump current.

$$K_P = I_C \cdot R \tag{2.2}$$

$$K_i = \frac{I_C}{C} \tag{2.3}$$

Equation (2.1) can be rewritten using  $\zeta$  (damping factor) and  $\omega_n$  (natural frequency) which are parameters that give insight into the time domain behavior of the PLL. A larger damping factor translates into less peaking and ringing of the output step response. On the other hand, a larger natural frequency translates into a larger 3-dB bandwidth and hence a faster rise time in the step response [25].

$$\frac{\phi_{out}}{\phi_{in}} = \frac{s \cdot (2 \cdot \zeta \cdot \omega_n) + \omega_n^2}{s^2 + s \cdot (2 \cdot \zeta \cdot \omega_n) + \omega_n^2}$$

(2.4)

By equating (2.1) and (2.4),  $\zeta$  and  $\omega_n$  are found to depend on the various loop gains as follows.

$$\omega_n = \sqrt{K_i \cdot K_{PD} \cdot K_{VCO}}$$

(2.5)

$$\zeta = \frac{K_P}{K_i} \cdot \frac{\omega_n}{2} \tag{2.6}$$

In stabilizing the PLL, the two parameters most readily available to the designer are  $K_P$  and  $K_i$ . Equation (2.6) tells us that to keep constant  $\zeta$  (a measure of relative stability),  $K_i$  must be increased four-fold for every two-fold increase in  $K_P$ . This is because  $\omega_n$  also depends on the square root of  $K_i$ .

#### 2.1.3 CDR Loop Dynamics

As a CDR, the PLL loop dynamics found in Section 2.1.2 are modified by the transition density (TD) of the input data [23]. The transition density is the ratio of the number of transitions to the number of bits transmitted in a serial bitstream. It is 1.0 when the input is a clock pattern. Many serial test patterns, such as PRBS, have a transition density close to 0.5 [26-27]. The impact of transition density is to scale  $K_{PD}$  by the same factor since the absence of transitions reduces the *average* output pulse width observed over many bits. Equations (2.1) and (2.5) are modified simply by replacing  $K_{PD}$  with TD·  $K_{PD}$ .

$$\frac{\phi_{out}}{\phi_{in}} = \frac{s \cdot K_P \cdot (TD \cdot K_{PD}) \cdot K_{VCO} + K_i \cdot (TD \cdot K_{PD}) \cdot K_{VCO}}{s^2 + s \cdot K_P \cdot (TD \cdot K_{PD}) \cdot K_{VCO} + K_i \cdot (TD \cdot K_{PD}) \cdot K_{VCO}}$$

(2.7)

$$\omega_n = \sqrt{K_i \cdot (TD \cdot K_{PD}) \cdot K_{VCO}}$$

(2.8)

An approximation of the 3-dB bandwidth can be made when  $\zeta$  is large. This is a reasonable condition given that CDRs are designed for  $\zeta$  larger than 5 such that the loop is over-damped and approaches a single pole response [26]. The purpose of over-damping is to minimize any amplification of the jitter at the input of the CDR. Under this condition, (2.4) and (2.7) can be approximated with the following equation.

$$\frac{\phi_{out}}{\phi_{in}} = \frac{K_P \cdot (TD \cdot K_{PD}) \cdot K_{VCO}}{s + K_P \cdot (TD \cdot K_{PD}) \cdot K_{VCO}} = \frac{2 \cdot \zeta \cdot \omega_n}{s + 2 \cdot \zeta \cdot \omega_n}$$

(2.9)

Then the 3-dB bandwidth (in Hz) is approximated with (2.10). Notice the absence of  $K_i$  from this equation since an infinite damping factor corresponds to zero  $K_i$ . In reality, the bandwidth of the CDR shows some dependence on  $K_i$ .

$$f_{-3dB} \cong \frac{K_P \cdot (TD \cdot K_{PD}) \cdot K_{VCO}}{2 \cdot \pi} = \frac{\zeta \cdot \omega_n}{\pi}$$

(2.10)

#### 2.1.4 Noise to Phase Estimation Error Transfer Function

When used in chip to chip applications where a large number of high speed transceivers are integrated with a noisy digital core onto a single substrate, there are two dominant sources of jitter that concerns the CDR designer. The first is jitter at the input of the CDR due primarily to RJ and ISI.<sup>3</sup> The second is from instability in the VCO frequency caused either by device noise (i.e. thermal and 1/f) or supply and substrate noise. The momentary frequency errors cause jitter accumulation until the CDR is able to correct this disturbance. These observations for the CDR are similar to those made by Mansuri [28] for clock generation PLLs except that the main source of input jitter in that work is from the inherent noise of an off-chip oscillator (e.g. crystal).

Figure 2.4 shows the model used to find the transfer function from the noise source to the phase estimation error ( $\Phi_{ee}$ ) in order to assess the impact of these noise sources on

<sup>&</sup>lt;sup>3</sup> This is true even when equalizers are used in the design. Most equalizers are symbol spaced. Regardless of whether they are implemented in the TX as a finite impulse response (FIR) filter or at the RX as a decision feedback equalizer (DFE), they only minimize the ISI at the data sampling point. ISI for times in between, including the transitions, are not improved significantly [29].

the CDR's performance. Phase estimation error implies that the CDR is sampling the data away from the optimal point in time and hence should be minimized. Figure 2.5 shows the normalized transfer functions from the two noise ports to  $\Phi_{ee}$ .

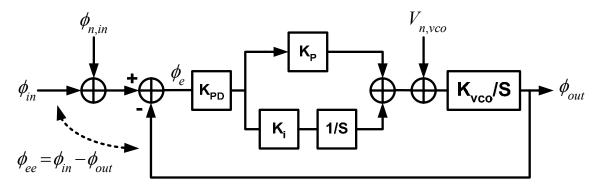

Figure 2.4: Linear model for finding noise to phase estimation error transfer functions.  $\Phi_{n,in}$  is the jitter at the input.  $V_{n,vco}$  is the device, supply, and substrate noise affecting the VCO frequency. The output of interest is the phase estimation error ( $\Phi_{ee}$ ).

The transfer function from  $\Phi_{n,in}$  to  $\Phi_{ee}$  (2.11) is identical to the input-output transfer function of (2.7) except for an inversion and is a low pass response. Therefore, it is desired to minimize the bandwidth of the CDR in order to reduce the amount of phase estimation error caused by input jitter.

$$\frac{\phi_{ee}}{\phi_{n,in}} = -\frac{\phi_{out}}{\phi_{n,in}} = -\frac{\phi_{out}}{\phi_{in}}$$

(2.11)

It is important to note that the BER of the link is ultimately determined by the phase error ( $\Phi_e$ ). However, using  $\Phi_e$  instead of  $\Phi_{ee}$  in the preceding analysis leads to the wrong conclusion that a larger CDR bandwidth is desired at all costs. This is because the model ignores the uncorrelated nature of the input jitter and the existence of finite loop delay. For uncorrelated jitter, minimizing  $\Phi_{ee}$  leads to minimum  $\Phi_e$  and hence the best BER. As we will see later in the context of jitter tolerance, the phase of the TX ( $\Phi_{in}$ ) can contain correlated jitter (e.g. from the off-chip oscillator) that has low-frequency content. The need to track low frequency changes in  $\Phi_{in}$  places a practical bound on how small the CDR bandwidth can be before degrading rather than improving the BER.

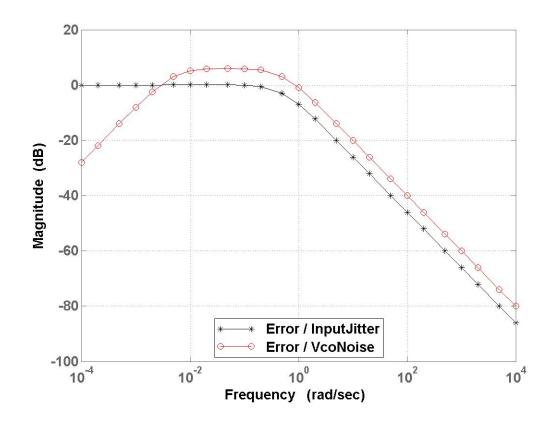

Figure 2.5: Normalized transfer functions from  $\Phi_{n,in}$  to  $\Phi_{ee}$  and from  $V_{n,vco}$  to  $\Phi_{ee}$ . TD = 0.5, K<sub>PD</sub> = 1, K<sub>P</sub> = 1, K<sub>i</sub> = 0.005, K<sub>vco</sub> = 1, and  $\zeta$  = 5 in this example.

The transfer function from  $V_{n,vco}$  to  $\Phi_{ee}$  is a band pass response (Figure 2.5). It has a single zero at 0 Hz and two poles at the same location as the input-output transfer function.

$$\frac{\phi_{ee}}{V_{n,vco}} = -\frac{\phi_{out}}{V_{n,vco}} = \frac{-s \cdot K_{VCO}}{s^2 + s \cdot K_P \cdot (TD \cdot K_{PD}) \cdot K_{VCO} + K_i \cdot (TD \cdot K_{PD}) \cdot K_{VCO}}$$

(2.12)

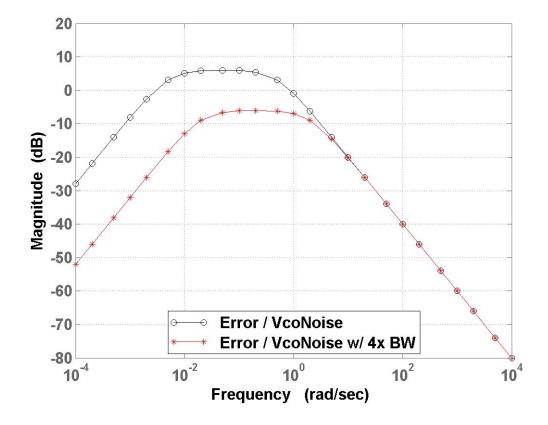

Figure 2.6 shows how the bandpass response changes when the bandwidth of the CDR is increased by a factor of 4. It is clear that increasing the bandwidth of the CDR not only reduces the width (in frequency) of the pass band, but also reduces the peak gain of the noise transfer function. This is in line with intuition which says that to minimize

the impact of VCO noise, a large CDR bandwidth is desired so that it can quickly correct for the disturbances in the VCO phase.

Figure 2.6: Normalized transfer function from  $V_{n,vco}$  to  $\Phi_{ee}$  for two different loop bandwidths. Bandwidth is adjusted by changing  $K_P = 1$  and  $K_i = 0.005$  to  $K_P = 4$  and  $K_i = 0.08$ .  $\zeta = 5$  for both cases for fair comparison.

Link performance degradation from uncorrelated input jitter calls for a small CDR bandwidth whereas VCO jitter calls for a large one. These opposing constraints on the bandwidth of the analog PLL based CDR make its design difficult in highly integrated chip to chip applications.<sup>4</sup>

<sup>&</sup>lt;sup>4</sup> Predicting the characterisitics of supply and substrate noise during the design phase also makes it difficult to optimize the bandwidth of the CDR. Recent advances in supply noise measurement make it possible to at least garner information from a previous chip to improve subsequent revisions [30].

### 2.2 Semi-Digital Dual Loop CDR