# MEMORY HIERARCHY DESIGN FOR STREAM COMPUTING

# A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

Nuwan S. Jayasena September 2005

© Copyright by Nuwan S. Jayasena 2006 All Rights Reserved I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

William J. Dally (Principal Adviser)

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

Mark A. Horowitz

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

Christoforos Kozyrakis

Approved for the University Committee on Graduate Studies.

# Abstract

To be filled in...

# Acknowledgements

To be filled in too...

# Contents

| A            | bstra | nct                                            | iv           |

|--------------|-------|------------------------------------------------|--------------|

| $\mathbf{A}$ | ckno  | wledgements                                    | $\mathbf{v}$ |

| 1            | Inti  | roduction                                      | 1            |

|              | 1.1   | Research Contributions                         | 3            |

|              | 1.2   | Thesis Roadmap                                 | 4            |

| 2            | Bac   | ekground and Motivation                        | 6            |

|              | 2.1   | Exploiting Data Parallelism                    | 7            |

|              | 2.2   | Stream Programming                             | 9            |

|              | 2.3   | Stream Processor Architecture                  | 13           |

|              |       | 2.3.1 Bandwidth Hierarchy                      | 15           |

|              | 2.4   | Alternative Data Parallel Architectures        | 20           |

|              |       | 2.4.1 Vector Processors                        | 21           |

|              |       | 2.4.2 Multi-threaded Processors                | 22           |

|              |       | 2.4.3 Media Extensions to General-purpose CPUs | 23           |

|              | 2.5   | DRAM Characteristics                           | 23           |

|              | 2.6   | Emerging Trends                                | 26           |

|              | 2.7   | Summary                                        | 27           |

| 3            | Gra   | anularity of Data Parallelism                  | 28           |

|              | 3.1   | Register Capacity Requirements                 | 28           |

|              |       | 3.1.1 Impact of Parallel Execution             | 29           |

|   |     | 3.1.2   | Discussion                                                    | 31  |

|---|-----|---------|---------------------------------------------------------------|-----|

|   | 3.2 | DRAM    | I Performance                                                 | 33  |

|   |     | 3.2.1   | Impact of Caches                                              | 36  |

|   |     | 3.2.2   | Evaluation Methodology                                        | 38  |

|   |     | 3.2.3   | Microbenchmarks                                               | 40  |

|   |     | 3.2.4   | Application Performance                                       | 45  |

|   |     | 3.2.5   | Sensitivity to System Parameters                              | 50  |

|   |     | 3.2.6   | Discussion                                                    | 53  |

|   | 3.3 | Multi-  | threaded Architectures                                        | 54  |

|   | 3.4 | Summ    | ary                                                           | 55  |

| 4 | Cor | nmunio  | cation Hierarchy                                              | 57  |

|   | 4.1 | Comm    | unication in Time: Data Reuse                                 | 58  |

|   | 4.2 | Comm    | nunication in Space: Resources and Constraints in Stream Pro- |     |

|   |     | cessors | 3                                                             | 59  |

|   |     | 4.2.1   | Alternatives to SRF-level Communication                       | 61  |

|   |     | 4.2.2   | Application Examples                                          | 62  |

|   |     | 4.2.3   | SRF-Level Bandwidth Requirements                              | 67  |

|   | 4.3 | A Stre  | eam Register File with Indexed Access                         | 69  |

|   |     | 4.3.1   | Standard SRF Implementation                                   | 69  |

|   |     | 4.3.2   | In-lane Indexed Access                                        | 70  |

|   |     | 4.3.3   | Cross-lane Indexed Access                                     | 78  |

|   |     | 4.3.4   | Programmer Interface                                          | 82  |

|   |     | 4.3.5   | Evaluation Methodology                                        | 84  |

|   |     | 4.3.6   | Results and Discussion                                        | 88  |

|   |     | 4.3.7   | Sensitivity to Access Latency                                 | 92  |

|   |     | 4.3.8   | Cross-lane Communication Resource Utilization                 | 94  |

|   |     | 4.3.9   | Area and Energy Impact                                        | 96  |

|   |     | 4.3.10  | Further Optimizations                                         | 98  |

|   | 4.4 | Summ    | ary                                                           | 100 |

| 5 | Soft | ware-   | vs. Hardware-Managed Memories                          | 102 |

|---|------|---------|--------------------------------------------------------|-----|

|   | 5.1  | Source  | es of Performance Differences                          | 103 |

|   | 5.2  | Memo    | ry Use Characteristics of Applications                 | 107 |

|   | 5.3  | Perfor  | mance Evaluation                                       | 110 |

|   |      | 5.3.1   | Evaluation Methodology                                 | 110 |

|   |      | 5.3.2   | Results and Discussion                                 | 116 |

|   |      | 5.3.3   | Off-chip Accesses on Cache-based Systems               | 119 |

|   |      | 5.3.4   | Performance Sensitivity to Cache Parameters            | 121 |

|   |      | 5.3.5   | Desired Cache Characteristics                          | 122 |

|   | 5.4  | Epoch   | based Invalidation                                     | 123 |

|   |      | 5.4.1   | Epoch Allocation                                       | 125 |

|   |      | 5.4.2   | Hardware Support for Epochs                            | 127 |

|   |      | 5.4.3   | Performance Evaluation                                 | 129 |

|   |      | 5.4.4   | Sensitivity to System Parameters                       | 131 |

|   | 5.5  | Relate  | ed Work                                                | 133 |

|   | 5.6  | Summ    | nary                                                   | 133 |

| 6 | Hyb  | orid Ba | andwidth Hierarchies                                   | 136 |

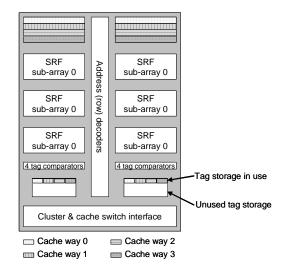

|   | 6.1  | Organ   | ization and Microarchitecture                          | 138 |

|   |      | 6.1.1   | Capacity and Resource Allocation                       | 140 |

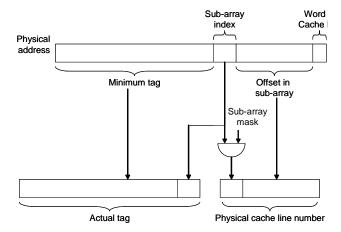

|   |      | 6.1.2   | Addressing Considerations                              | 145 |

|   |      | 6.1.3   | Memory Reallocation                                    | 145 |

|   | 6.2  | Perfor  | mance Evaluation                                       | 147 |

|   | 6.3  | Relate  | ed Work                                                | 151 |

|   | 6.4  | Summ    | nary                                                   | 152 |

| 7 | Con  | clusio  | $\mathbf{n}\mathbf{s}$                                 | 154 |

|   | 7.1  | Future  | e Research                                             | 155 |

|   |      | 7.1.1   | Hybrid Memory Hierarchies and Epoch-based Invalidation | 157 |

# List of Tables

| 2.1 | Bandwidth hierarchy of Imagine and Merrimac processors                 | 16  |

|-----|------------------------------------------------------------------------|-----|

| 2.2 | Example SDRAM access latencies (Micron 256Mb DDR2, speed grade         |     |

|     | -5)                                                                    | 25  |

| 3.1 | Loop unrolling and software pipeline depths of application kernels for |     |

|     | stream processing                                                      | 31  |

| 3.2 | Memory system parameters for stream and vector access comparison .     | 38  |

| 3.3 | Processor parameters for stream and vector access comparison           | 39  |

| 3.4 | Microbenchmarks used to evaluate memory system performance of          |     |

|     | stream and vector accesses                                             | 40  |

| 3.5 | Application benchmarks used to evaluate memory system performance      |     |

|     | of stream and vector accesses                                          | 46  |

| 3.6 | Memory access pattern distribution of benchmarks (percentages)         | 47  |

| 4.1 | Machine configurations for indexed SRF evaluation                      | 84  |

| 4.2 | Machine parameters for indexed SRF evaluation (SRF access latencies    |     |

|     | shown for the case with no arbitration failures or bank conflicts)     | 85  |

| 4.3 | Parameters for IG benchmark datasets (strip size is the average number |     |

|     | of neighbor records processed per kernel invocation)                   | 88  |

| 5.1 | Application benchmarks used to compare stream computing perfor-        |     |

|     | mance on software- and hardware-managed on-chip memories               | 108 |

| 5.2 | Processor parameters for software- and hardware-managed on-chip mem-   |     |

|     | ory comparison                                                         | 111 |

| 5.3 | SRF parameters for software- and hardware-managed on-chip memory        |     |

|-----|-------------------------------------------------------------------------|-----|

|     | comparison                                                              | 111 |

| 5.4 | Cache parameters for software- and hardware-managed on-chip mem-        |     |

|     | ory comparison                                                          | 115 |

| 5.5 | Variations of $RBW$ cache configuration for evaluating performance sen- |     |

|     | sitivity to cache parameters                                            | 121 |

| C 1 |                                                                         |     |

| 6.1 | Bit masks for qualifying sub-array selection in hardware-managed cache  |     |

|     | access in hybrid memory                                                 | 146 |

| 6.2 | Hybrid streaming memory configurations evaluated. Memory capacity       |     |

|     | shown is the total across all lanes. Number of sub-arrays shown in      |     |

|     | parentheses is per lane                                                 | 148 |

# List of Figures

| 2.1  | Simple kernel computing the square of the distance between two se-                  |    |

|------|-------------------------------------------------------------------------------------|----|

|      | quences of coordinates                                                              | 10 |

| 2.2  | Stream representation of simplified finite element method                           | 10 |

| 2.3  | Block diagram of a stream processor                                                 | 13 |

| 2.4  | Sequence of host processor operations for simple FEM example                        | 14 |

| 2.5  | Block diagram of a single compute cluster                                           | 14 |

| 2.6  | Bandwidth hierarchy mapping of FEM example. Solid arrows represent                  |    |

|      | stream transfers, dotted arrows represent index transfers                           | 16 |

| 2.7  | Stream buffers match the access characteristics of the SRF and com-                 |    |

|      | pute clusters (only a single lane is shown for simplicity)                          | 18 |

| 2.8  | Block diagram of the streaming memory system shown with two stream                  |    |

|      | load/store units and an optional on-chip data cache                                 | 19 |

| 2.9  | Vector processing representation of squared distance computation                    | 21 |

| 2.10 | Internal structure of a modern DRAM                                                 | 24 |

| 2.11 | Example DRAM access operations schedule                                             | 25 |

| 3.1  | Vector register capacity requirements relative to stream registers using            |    |

|      | realistic parameters: $P_{vec} = 1, F = 4, L_{vec} = L_{str} = 256$ elements, $B_M$ |    |

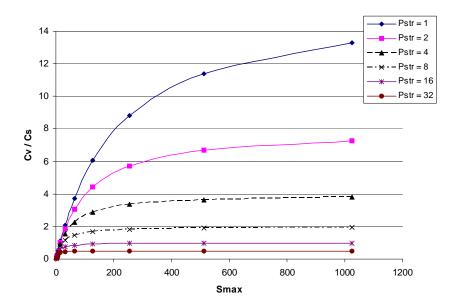

|      | = 8 words/cycle, $T_M$ = 200 cycles, $N_{cl}$ = 8, $S_{IO}$ = 10                    | 32 |

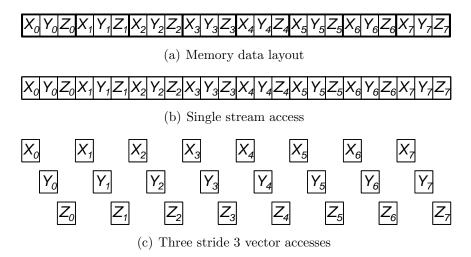

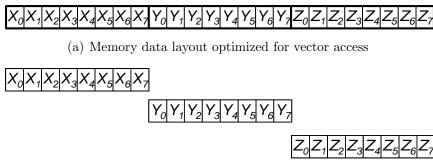

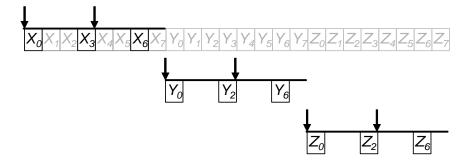

| 3.2  | Stream and vector access to linear array of 3-word records in memory                | 34 |

| 3.3  | Array of 3-word records optimized for vector access                                 | 35 |

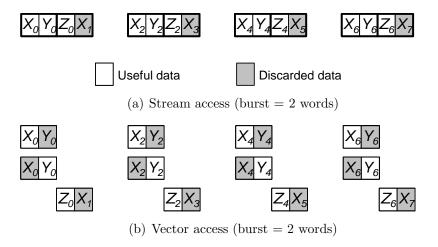

| 3.4  | Stride 2 access to array of 3-word records using 2-word DRAM bursts                 | 35 |

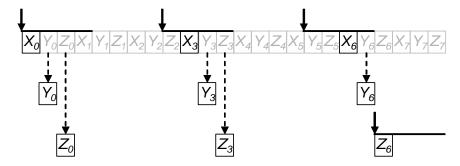

| 3.5  | Strided vector access with larger cache lines than data record size. Solid                |    |

|------|-------------------------------------------------------------------------------------------|----|

|      | arrows indicate cache line fetch initiations, dotted arrows represent                     |    |

|      | cache hits due to previous fetches, and horizontal dark lines indicate                    |    |

|      | the spans of cache lines                                                                  | 36 |

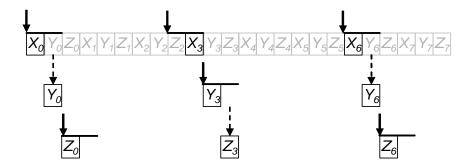

| 3.6  | Strided vector access with shorter cache lines than data record size.                     |    |

|      | Solid arrows indicate cache line fetch initiations, dotted arrows rep-                    |    |

|      | resent cache hits due to previous fetches, and horizontal dark lines                      |    |

|      | indicate the spans of cache lines                                                         | 37 |

| 3.7  | Strided vector access with cache and vector-optimized data layout.                        |    |

|      | Arrows indicate cache line fetch initiations and horizontal dark lines                    |    |

|      | indicate the spans of cache lines                                                         | 37 |

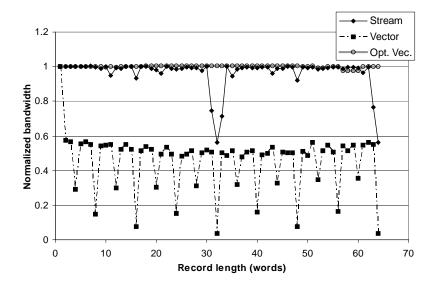

| 3.8  | Uncached sequential access ( $Seq$ microbenchmark) performance under                      |    |

|      | Stream, Vector, and Optimized Vector accesses as record size varies                       |    |

|      | (normalized to $Seq$ with 1-word records)                                                 | 41 |

| 3.9  | Cached sequential access ( $SeqC$ microbenchmark) performance under                       |    |

|      | Stream, Vector, and Optimized Vector accesses as record size varies                       |    |

|      | (normalized to $Seq$ with 1-word records)                                                 | 42 |

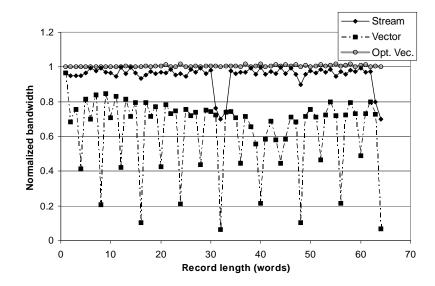

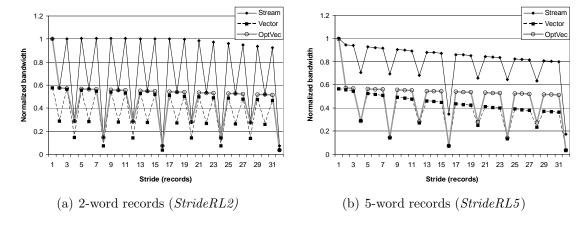

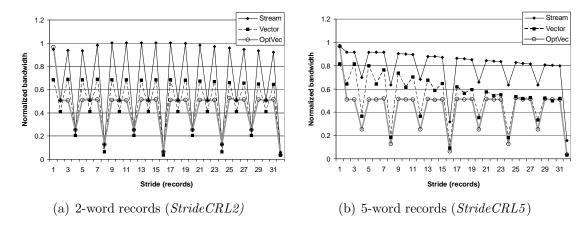

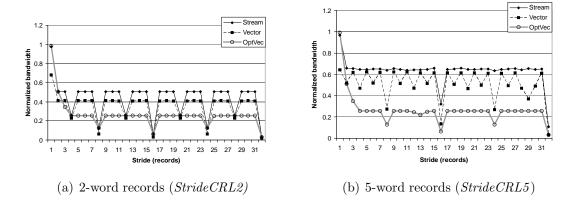

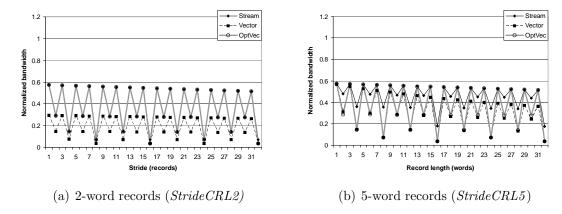

| 3.10 | Uncached strided access performance under Stream, Vector, and Opti-                       |    |

|      | $mized\ Vector\ accesses\ as\ stride\ varies\ (normalized\ to\ Seq\ with\ 1-word$         |    |

|      | ${\rm records})  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $         | 43 |

| 3.11 | Cached strided access performance under Stream, Vector, and Opti-                         |    |

|      | mized Vector accesses as stride varies (normalized to Seq with 1-word                     |    |

|      | records)                                                                                  | 44 |

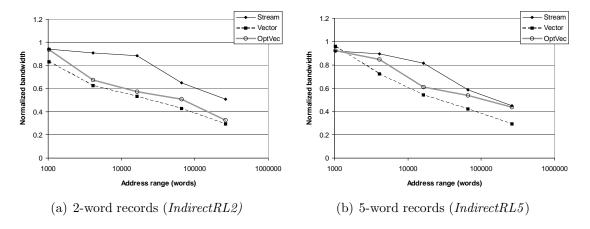

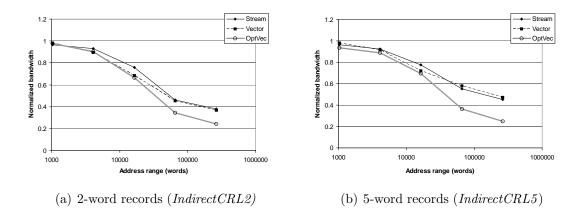

| 3.12 | Uncached indirect access performance under <i>Stream</i> , <i>Vector</i> , and <i>Op-</i> |    |

|      | timized Vector accesses as the sparseness of the access pattern varies                    |    |

|      | (normalized to Seq with 1-word records)                                                   | 44 |

| 3.13 | Cached indirect access performance under <i>Stream</i> , <i>Vector</i> , and <i>Opti-</i> |    |

|      | mized Vector accesses as the sparseness of the access pattern varies                      |    |

|      | (normalized to Seq with 1-word records)                                                   | 45 |

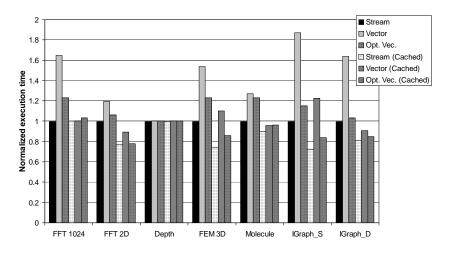

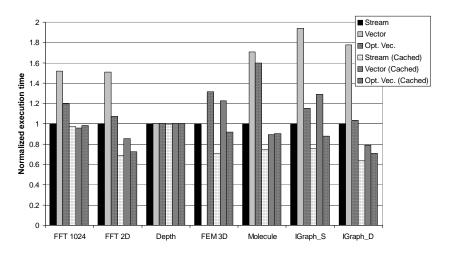

| 3.14 | Application performance under Stream, Vector, and Optimized Vector                        |    |

|      | accesses (normalized to the uncached <i>Stream</i> case)                                  | 47 |

| 3.15 | Application performance under Stream, Vector, and Optimized Vec-           |    |

|------|----------------------------------------------------------------------------|----|

|      | tor accesses in the limiting case where computation is instantaneous       |    |

|      | (normalized to the uncached <i>Stream</i> case)                            | 49 |

| 3.16 | Cached strided access performance $StrideCRLn < 4, 2, 4 >$ (normalized     |    |

|      | to $Seq < 2, 2, 2 > $ with 1-word records)                                 | 51 |

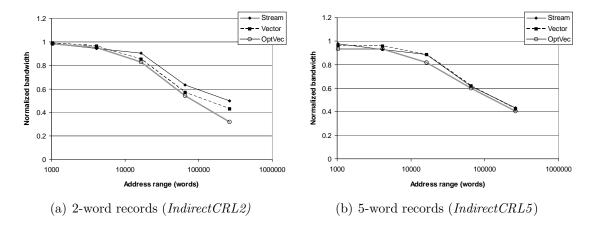

| 3.17 | Cached indirect access performance of $IndirectCRLn < 4, 2, 4 > $ (nor-    |    |

|      | malized to $Seq < 2, 2, 2 > \text{with 1-word records})$                   | 52 |

| 3.18 | Cached strided access performance of $StrideCRLn < 1, 1, 1 > $ (normal-    |    |

|      | ized to $Seq < 2, 2, 2 > $ with 1-word records)                            | 53 |

| 4.1  | Parallelization transforms a subset of temporal reuse to spatial com-      |    |

|      | munication                                                                 | 58 |

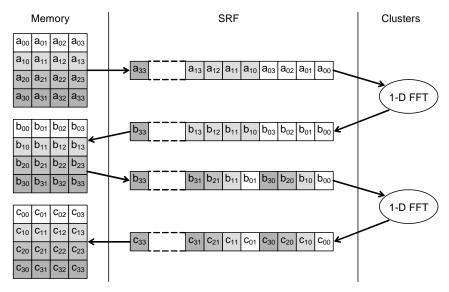

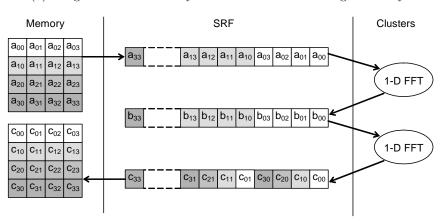

| 4.2  | Irregular stream access in 2D FFT: capturing irregular producer-consumer   |    |

|      | locality in the SRF reduces memory bandwidth demands                       | 63 |

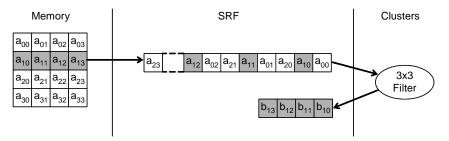

| 4.3  | Neighborhood access in 2D array: communication at the SRF elimi-           |    |

|      | nates the need to hold large amounts of array data in local registers $$ . | 64 |

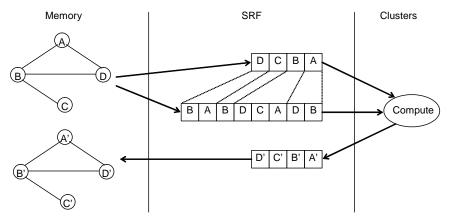

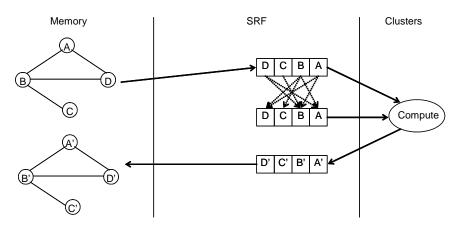

| 4.4  | Neighbor access in irregular graphs: capturing irregular temporal lo-      |    |

|      | cality at the SRF reduces memory bandwidth and data replication in         |    |

|      | the SRF                                                                    | 65 |

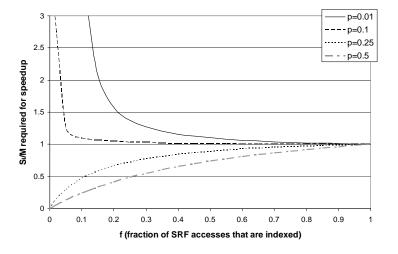

| 4.5  | Required ratio of indexed SRF to memory system bandwidth in order          |    |

|      | to achieve application speedup based on model of application perfor-       |    |

|      | mance as being limited by memory or SRF bandwidth                          | 68 |

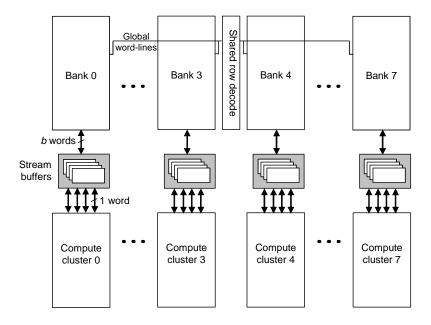

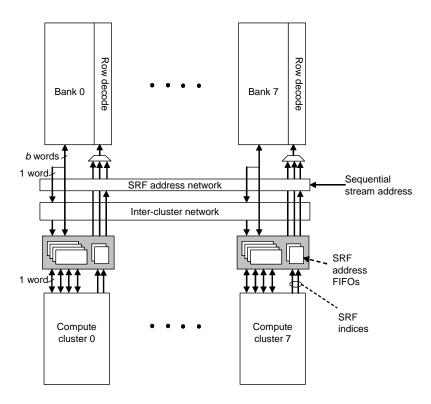

| 4.6  | Block diagram of sequentially accessed SRF with 8 banks                    | 70 |

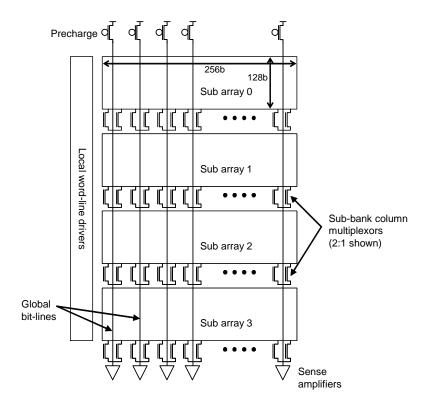

| 4.7  | Block diagram of a single bank in a sequentially accessed SRF. Bank        |    |

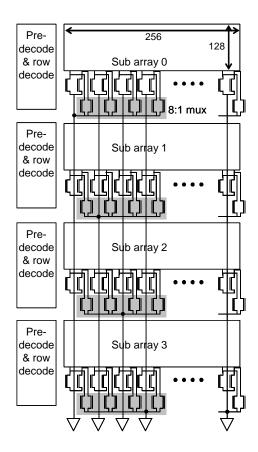

|      | capacity = 16<br>KB, block access = 128b, and array width = 256b as shown  | 71 |

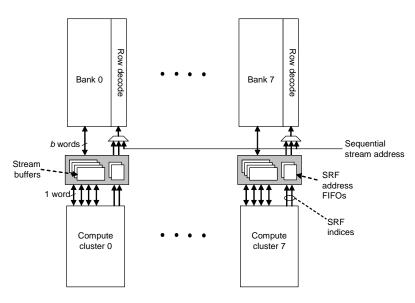

| 4.8  | Block diagram of an 8-bank SRF with in-lane indexed access                 | 72 |

| 4.9  | Block diagram of a single bank in an SRF with in-lane indexed access.      |    |

|      | Bank capacity = $16KB$ , block access = $128b$ , and array width = $256b$  |    |

|      | as shown                                                                   | 75 |

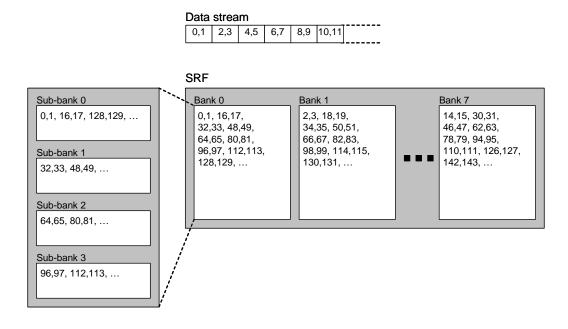

| 4.10 | Data distribution among banks and sub-banks of the SRF. Example         |     |

|------|-------------------------------------------------------------------------|-----|

|      | shown for 8 banks, 4 sub-banks per bank, and 128-bit block size (32-bit |     |

|      | words)                                                                  | 76  |

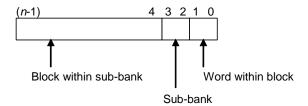

| 4.11 | In-lane SRF address bit mapping. Example shown for 4 sub-banks per      |     |

|      | bank, and 128-bit block size (32-bit words)                             | 76  |

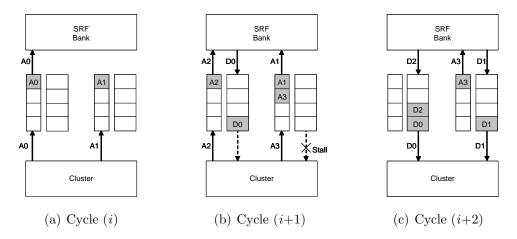

| 4.12 | In-lane indexed SRF access example. Hardware and timing simplified      |     |

|      | for clarity                                                             | 78  |

| 4.13 | Block diagram of an 8-bank SRF with cross-lane indexed access $\dots$   | 79  |

| 4.14 | Indexed SRF access syntax example                                       | 82  |

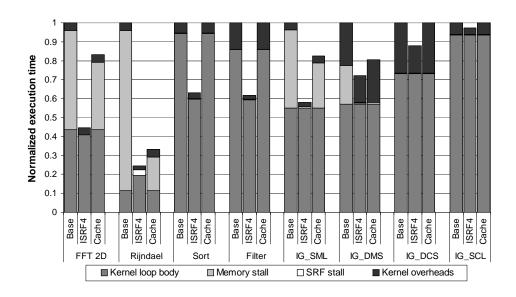

| 4.15 | Benchmark performance impact of indexed SRF access                      | 89  |

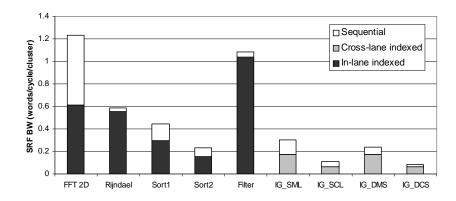

| 4.16 | Sustained SRF bandwidth (both Sort1 and Sort2 kernels are used by       |     |

|      | the $Sort$ benchmark)                                                   | 91  |

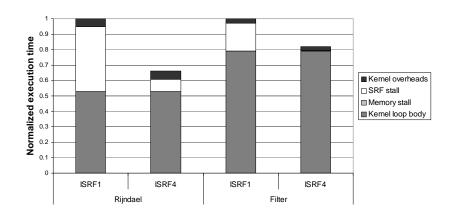

| 4.17 | Impact of indexed SRF bandwidth on benchmark performance                | 91  |

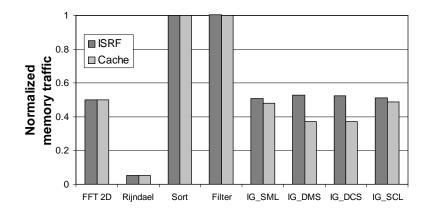

| 4.18 | Off-chip memory traffic generated by indexed SRF and $Cache$ machine    |     |

|      | organizations, normalized to $Base$                                     | 92  |

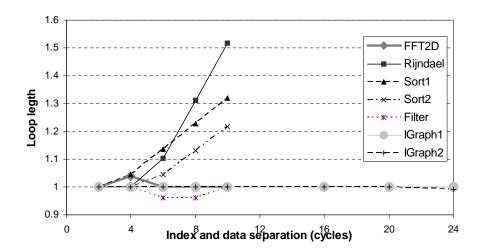

| 4.19 | Static schedule length variation of loop bodies with address and data   |     |

|      | separation of indexed SRF accesses                                      | 93  |

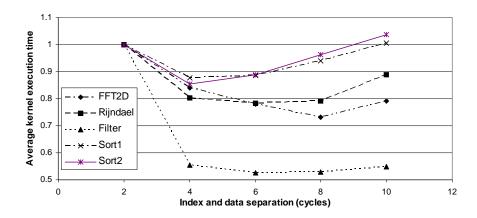

| 4.20 | Execution time variation of benchmarks with address and data sepa-      |     |

|      | ration of in-lane indexed SRF accesses                                  | 94  |

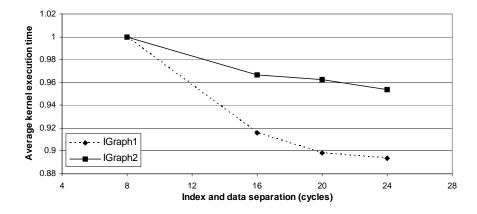

| 4.21 | Execution time variation of benchmarks with address and data sepa-      |     |

|      | ration of cross-lane indexed SRF accesses                               | 94  |

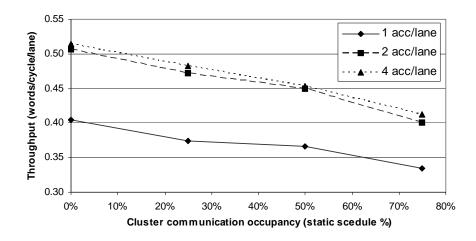

| 4.22 | Cross-lane indexed throughput variation with number of SRF accesses     |     |

|      | per cycle and inter-cluster traffic                                     | 95  |

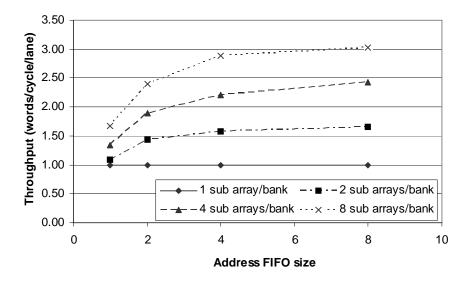

| 4.23 | In-lane indexed SRF throughput scaling with the number of sub-banks     |     |

|      | per SRF bank and address FIFO size                                      | 100 |

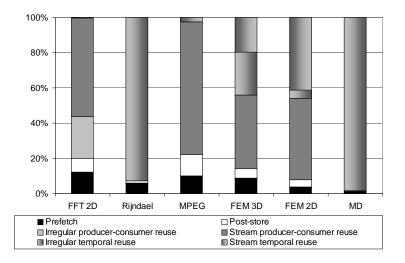

| 5.1  | On-chip memory access classification of benchmarks used in the com-     |     |

|      | parison of software- and hardware-managed memories for stream com-      |     |

|      | puting                                                                  | 109 |

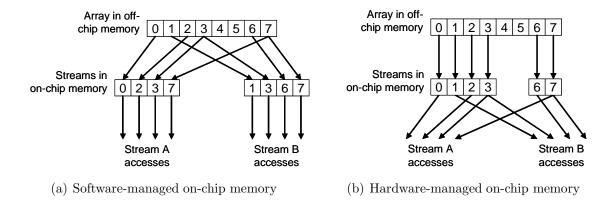

| 5.2  | Example of inter-stream irregular reuse                                 | 109 |

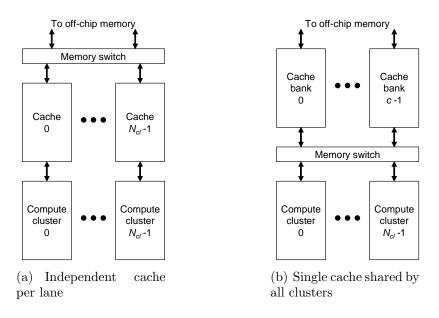

| 5.3  | Cache implementation alternatives for stream processing                 | 119 |

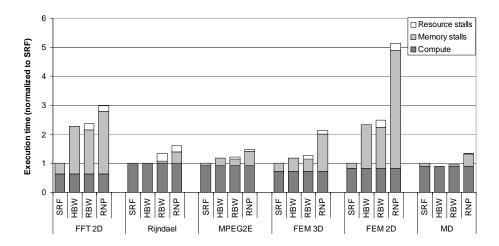

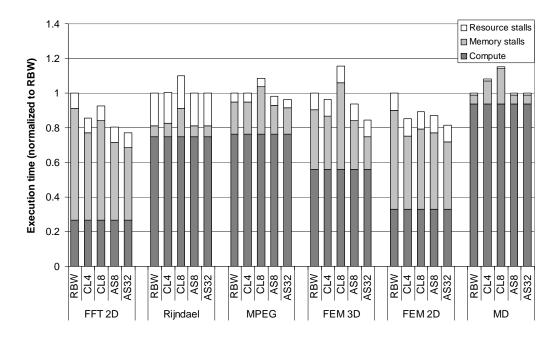

| 5.4  | Benchmark execution times on software-managed SRF and hardware-               |      |

|------|-------------------------------------------------------------------------------|------|

|      | managed cache configurations                                                  | 116  |

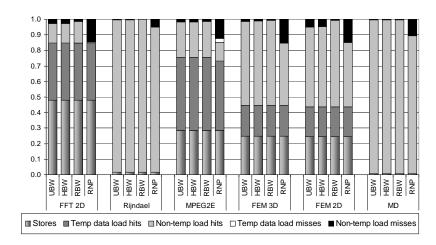

| 5.5  | Cache miss behavior for benchmarks used in software- and hardware-            |      |

|      | managed memory configurations                                                 | 118  |

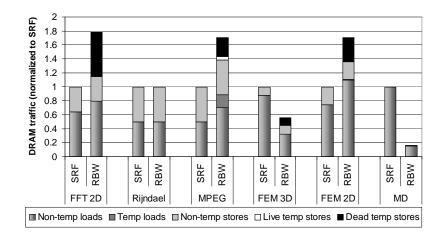

| 5.6  | Off-chip memory traffic generated by benchmarks under software- and           |      |

|      | hardware-managed on-chip configurations                                       | 120  |

| 5.7  | Sensitivity of benchmark execution time to cache parameters                   | 122  |

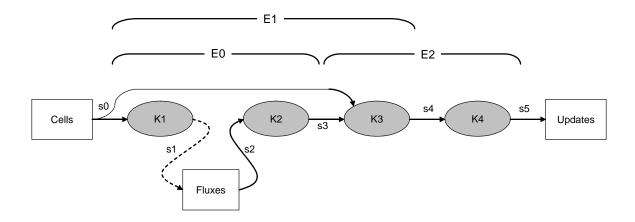

| 5.8  | Example epoch allocation over the stream graph of simplified finite           |      |

|      | element method                                                                | 125  |

| 5.9  | Simplified algorithm for epoch allocation within a basic block of stream      |      |

|      | graphs                                                                        | 126  |

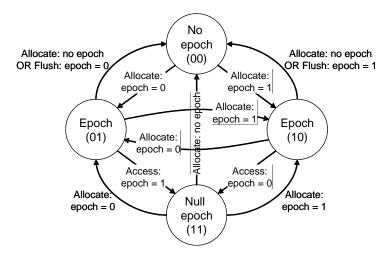

| 5.10 | State transitions of the epoch ID bits of a single cache line for $E_{max} =$ | 2128 |

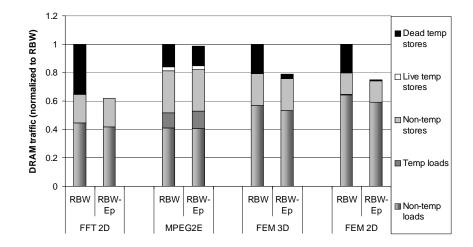

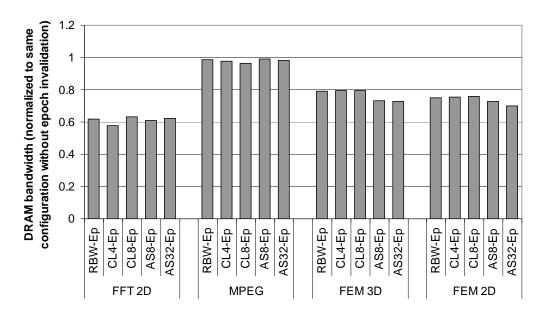

| 5.11 | Off-chip memory traffic generated by benchmarks with epoch invalidation       | n130 |

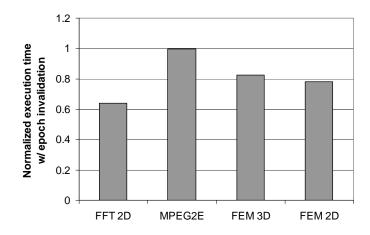

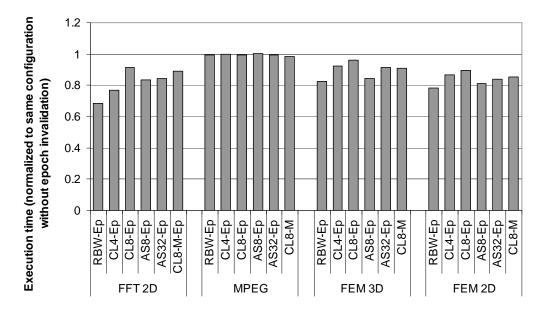

| 5.12 | Benchmark execution times with epoch invalidation                             | 130  |

| 5.13 | Sensitivity of execution time reduction with epoch invalidation to sys-       |      |

|      | tem parameters                                                                | 131  |

| 5.14 | Sensitivity of off-chip memory bandwidth reduction with epoch inval-          |      |

|      | idation to system parameters                                                  | 132  |

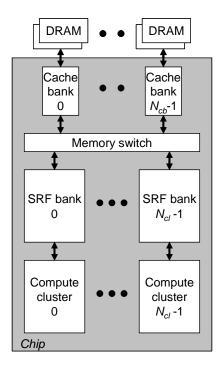

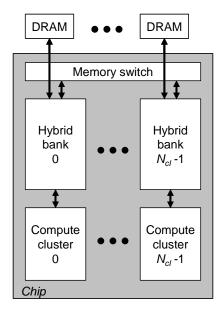

| 6.1  | Block diagram of stream processor bandwidth hierarchy with hardware-          |      |

|      | managed on-chip cache (SRF-level cross-lane communication network             |      |

|      | not shown for simplicity)                                                     | 137  |

| 6.2  | Overview of hybrid software- and hardware-managed on-chip memory              |      |

|      | for stream computing (SRF-level cross-lane communication network              |      |

|      | not shown for simplicity)                                                     | 138  |

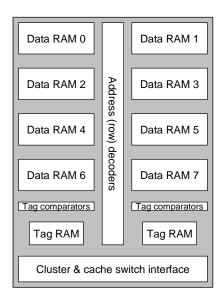

| 6.3  | Block diagram of a single bank of the hybrid software- and hardware-          |      |

|      | managed on-chip memory. This example shows a bank consisting of 8             |      |

|      | sub-arrays                                                                    | 140  |

| 6.4  | Example hybrid memory configuration with two and six sub-arrays               |      |

|      | allocated to hardware cache and software SRF respectively                     | 143  |

| 6.5 | Cache index and tag extraction for hybrid memory (assuming physi-             |     |

|-----|-------------------------------------------------------------------------------|-----|

|     | cally indexed and tagged cache)                                               | 146 |

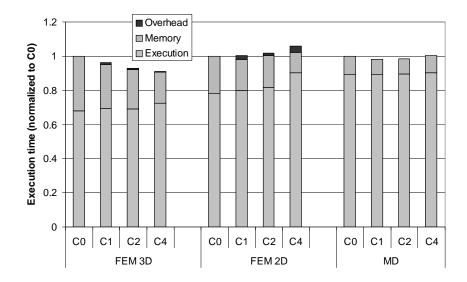

| 6.6 | Execution times of scientific benchmarks on hybrid memory organiza-           |     |

|     | tions (normalized to $C\theta$ )                                              | 149 |

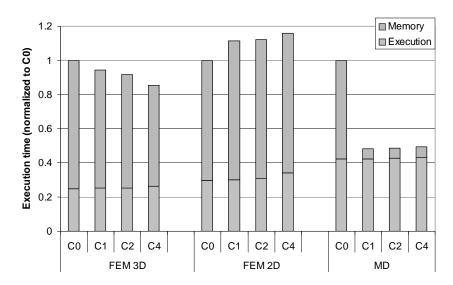

| 6.7 | Execution times of scientific benchmarks on hybrid memory organiza-           |     |

|     | tions (normalized to $C\theta$ ) with increased computation to off-chip band- |     |

|     | width ratio                                                                   | 150 |

# Chapter 1

### Introduction

Recent application trends have made media and signal processing, and graphics some of the most important applications across a broad range of computing platforms ranging from desktop to mobile devices. At the same time, demands on high performance computing systems continue to grow as scientific applications in fields such as biotechnology and climate modeling attempt to simulate larger-scale phenomena for longer periods with increasing precision. A characteristic common to both these application classes, as well as several other important ones such as network processing and encryption, is the presence of *data parallelism* which enables the computation on many data elements to take place simultaneously.

The parallelism available in these applications provide an excellent match to the characteristics of modern VLSI implementation technology. The very large number of devices available on a single chip today enables many arithmetic units to be integrated on to a single processor, allowing several computations to proceed in parallel. However, bandwidth for providing operands for these computations must be managed carefully. While very high bandwidths can be sustained on-chip, only a small fraction of that potential bandwidth can be supplied from off-chip memory due to pin bandwidth limitations. Therefore, it is important to capture as much data reuse, or locality, available in applications in on-chip memory. Stream programming expresses data parallel applications in a manner that exposes the available parallelism

and locality. Stream processor architectures exploit the parallelism and locality exposed by the programming model to achieve high performance and energy efficiency. Stream processing has been demonstrated to be effective for both media and scientific applications [RDK+98; DHE+03].

Stream processors implement a bandwidth hierarchy made up of registers and memory to sustain high operand bandwidth to arithmetic units. The registers closest to the arithmetic units provide the operands, and each successively further level of the hierarchy sustains decreasing bandwidth, matching the available off-chip bandwidth at the final level. Therefore, designing the bandwidth hierarchy in a manner that enables capturing the locality available in a broad range of data access patterns at levels close to the arithmetic units is critical for efficiently supporting a wide range of data parallel applications.

This thesis focuses on techniques for improving the efficiency of off-chip band-width utilization by capturing a broad range of locality on-chip, and by reducing non-essential off-chip traffic. We present a novel architecture for stream register files (SRF) that supports a wider range of access patterns than current stream processors through the use of explicitly indexed accesses. The SRF is a key component in the bandwidth hierarchy of a stream processor, and the additional flexibility afforded by indexed accesses enables more of the locality available in applications to be captured on-chip. We also compare the specialized bandwidth hierarchies of stream processors, which rely on software-managed memories, with the hardware-managed caches of general-purpose processors. We highlight the relative strengths of these two types of memories, and identify optimizations necessary in caches to better support streaming applications. Hybrid bandwidth hierarchies that incorporate characteristics of both stream register files and cache memories are also explored, and an organization characteristics is presented.

We also explore the efficiency of stream processing in terms of register requirements, and DRAM and cache bandwidth utilization. These studies show that the ordering of computation and memory accesses in stream processing lead to lower register requirements and provide a better match to modern memory hierarchy characteristics relative to other mainstream, programmable data parallel execution models.

### 1.1 Research Contributions

The main contributions of this thesis to the field of computer architecture and stream processing are:

- 1. An analysis of the register capacity requirements of stream processing compared to other widely used, programmable data parallel processing techniques. This analysis demonstrates the reduced register capacity requirements that arise from structuring the parallel computation at the granularity of operations on entire data records, as is done in stream processing, compared to alternative techniques that express parallelism at a granularity smaller than entire records.

- 2. An evaluation of cache and DRAM performance of stream processing compared to other widely used, programmable data parallel processing techniques. This evaluation shows that stream processing, by exposing the record-granularity locality present in applications to the hardware, improves utilization in modern DRAM-based memory hierarchies, thereby achieving higher performance for bandwidth-constrained applications.

- 3. A novel architecture for stream register files that supports flexible access patterns through explicit indexing. This design enables a more complete *communication hierarchy* within the bandwidth hierarchy of stream processors, enabling a broader range of data reuse to be captured at the stream register file level. This directly results in reduced demands on scarce off-chip memory bandwidth for a variety of application classes. A microarchitecture for a low-area-overhead implementation of the proposed design is also presented.

- 4. An evaluation of software- and hardware-managed on-chip memories for stream computing, which provides insights on the key benefits and sources of inefficiencies in each of these two types of memories. Hardware-managed (cache) memories benefit from fine-grain memory management implemented in hardware,

but suffer due to inefficiencies in replacement policies, name translation, and bandwidth limitations. Software-managed memories suffer due to coarse-grain memory management in software, but benefit from application-aware management policies and greater flexibility in name translation. This evaluation also establishes design requirements for hardware-managed (cache) memories when used in the context of a streaming bandwidth hierarchy.

- 5. Epoch-based cache invalidation, a novel technique for improving hardware-managed memory performance for stream computing based on identifying and actively invalidating cached state that is no longer live. This enables cache lines with dead data to be evicted without generating memory writes even if the lines are marked as dirty in the cache, resulting in reduced memory traffic.

- 6. A microarchitecture for a hybrid memory that supports both software and hardware management while preserving the key requirements of each type of memory for stream computing. The proposed structure allows the available capacity to be dynamically allocated between hardware- and software-managed memories based on application requirements identified at compile-time. Evaluations of this memory demonstrate that no single allocation of capacity between hardware- and software-managed memory is optimal over different applications, and customizing the allocation on a per-application basis leads to improved performance, particularly as off-chip bandwidth becomes increasingly scarce.

### 1.2 Thesis Roadmap

Chapter 2 provides an overview of background material including a brief introduction to stream programming, stream processor architecture, and alternative data parallel architectures.

Chapter 3 evaluates the impact that the granularity at which data parallelism is exploited at - individual operations or entire loop bodies - has on intermediate state storage requirements and off-chip memory system performance. This distinction in granularity correlates closely to a key difference between vector and stream

processing - two common data parallel execution models used in a number of recent programmable data-parallel architectures.

Chapter 4 explores the spatial and temporal communication requirements of data parallel applications, and the importance of a communication hierarchy in enabling the bandwidth hierarchy to efficiently capture a broad range of application data reuse patterns. Chapter 4 also introduces and evaluates a novel stream register file architecture that efficiently supports significantly more communication freedom compared to prior designs. This added flexibility enables efficient support for a wider range of access patterns, improving the performance of several classes of applications both in terms of execution time and reduced off-chip memory traffic.

While on-chip memories of traditional data parallel architectures have often been software-managed, using hardware managed memories for data parallel computing is becoming increasingly important due to a number of recent trends. Chapter 5 addresses these trends and studies the tradeoffs in software and hardware management of on-chip memory for data parallel computing. We characterize application data access patterns, and correlate these to memory system performance in order to identify the types of accesses that benefit from each type of memory. This study also highlights the sources of performance loss in the hardware and software managed memories, and establishes a set of requirements for each type of memory for sustaining high performance for the application classes studied. Chapter 5 also introduces epoch-based cache invalidation, a technique to improve the performance of hardware managed memories by identifying and explicitly invalidating dead data in the cache.

Chapter 6 introduces and evaluates a hybrid memory architecture that supports both software and hardware management while retaining the desirable characteristics of each type of memory identified in chapter 5. This design allows the available on-chip memory capacity to be dynamically allocated between software and hardware management, enabling the memory hierarchy to be better tailored to each application's access characteristics. The microarchitecture proposed for this design is a logical extension of the stream register file architecture introduced in chapter 4, enabling a low overhead implementation in the context of stream processing.

Finally, chapter 7 presents conclusions and discusses future research directions.

## Chapter 2

# Background and Motivation

Today's VLSI circuit technology enables billions of transistors to be integrated on a single chip. Therefore, the potential exists for thousands of arithmetic units to be incorporated on a single processor to achieve very high performance. However, in order to realize this potential, two technology constraints must be overcome. First, the long latency of memory accesses, which can be hundreds to thousands of cycles for an off-chip access in modern high performance processors, must be tolerated. Second, off-chip memory bandwidth, which is significantly lower than that available to on-chip memory structures, must not become a performance bottleneck.

Traditional general-purpose processors rely on instruction-level parallelism (ILP) to achieve high performance across a broad range of applications. However, extracting ILP from instruction sequences at compile-time is hindered by the lack of run-time information, and doing so at run-time requires complex and expensive hardware structures. Therefore, resources of processors designed for ILP are allocated to anticipate a relatively small amount of simultaneous computation. Significantly greater resources are spent on discovering the parallelism and on cache hierarchies designed to reduce the average latency of memory accesses. As a result, only a small fraction of the raw capability of the underlying implementation technology is realized in terms of true computational performance in such architectures.

Several important application classes exhibit data parallelism where computation

can be applied to a large number of data items simultaneously. Unlike ILP, data parallelism can often be analyzed and scheduled at compile-time, eliminating the need for expensive hardware techniques to dynamically discover parallelism. Application classes with large amounts of data parallelism include media and signal processing, where long sequences of samples are operated on, and scientific applications where the behavior of physical systems are approximated by modeling a large number of small segments of the overall system. These application classes are also some of the most demanding consumers of compute cycles. It is widely accepted that media applications will continue to consume an increasingly greater fractions of the computing capability on personal computing devices [DD97]. At the same time, scientific computing applications often drive the requirements for high-end supercomputer designs. The parallelism available in these applications can be exploited by processor architectures specialized for extracting data parallelism to sustain very high performance, realizing a greater fraction of the capabilities enabled by implementation technology.

### 2.1 Exploiting Data Parallelism

The presence of data parallelism in an application provides two important opportunities to achieve high performance – the parallelism itself, and latency tolerance. It is important to note that the memory hierarchy design plays a critical role in enabling both these opportunities.

First, computation on large numbers of data elements can proceed in parallel, increasing the compute rate. This is further facilitated by the fact that operations on one data element are largely independent of operations on other data elements in most media and scientific applications. However, the levels of the memory hierarchy closest to the arithmetic units (usually the register files) must be designed to provide sufficient operand bandwidth to sustain the parallel computation. Furthermore, the overall compute rate is ultimately limited by the rate at which application inputs and outputs can be read or written from off-chip memory through any intermediate stages of the memory hierarchy. Therefore, efficient utilization of the bandwidth available at all levels, especially off-chip memory, is crucial for sustaining high performance.

Second, the available parallelism allows long memory latencies to be tolerated. Unlike ILP processors, whose ability to continue beyond a long latency memory operation is limited by available ILP and the sizes of the issue window and commit queue, a data parallel architecture can continue to operate on the many other independent data elements available. However, the memory hierarchy must be designed to support continued execution while the long latency accesses are outstanding. While some degree of such support is found in most modern high-performance memory systems in the form of non-blocking caches with multiple outstanding misses, the requirements are more stringent for data parallel architectures. The cost of a memory stall in terms of wasted instruction issue slots is extremely high in data parallel architectures due to the highly-parallel execution capabilities. In order to minimize the probability of memory stalls, the number of concurrently outstanding memory accesses that must be supported by data parallel architectures to the i<sup>th</sup> level of the memory hierarchy is given by Little's Law as expressed by equation (2.1), where  $A_i$ ,  $BW_i$ , and  $L_i$  are the outstanding accesses, bandwidth, and latency for the i<sup>th</sup> level of the memory hierarchy. In modern systems where off-chip memory accesses take several hundred cycles to complete, this requires the memory system to support thousands of in-flight accesses.

$$A_i = BW_i \times L_i \tag{2.1}$$

The latency tolerance of data parallel applications shifts the focus of memory hierarchy design of architectures targeted at these applications from reducing average latency (which is the critical concern in general-purpose CPUs) to achieving high bandwidth. The ability to sustain many in-flight memory operations is crucial from this perspective as well, since it allows the entire memory pipeline to be filled, enabling a high fraction of the peak memory bandwidth to be sustained.

The techniques presented in this thesis build on these capabilities enabled by data parallelism in order to further improve the off-chip memory bandwidth utilization for a variety of application classes.

### 2.2 Stream Programming

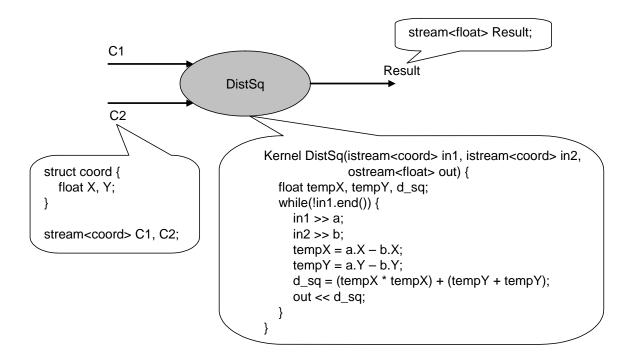

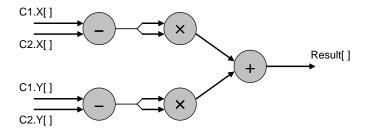

The stream programming model can be used to express data parallel applications in a manner that exposes the available locality and parallelism. In this model, an application is composed of a collection of data *streams* passing through a series of computation *kernels*. Each stream is a sequence of homogeneous data records. Each kernel is a loop body that is applied to each record of the input stream(s). A trivial example is a kernel that computes the square of the distance between two points in 2D space and is shown in figure 2.1. The compute kernel is represented by the oval and streams are represented by the arrows in the figure. The kernel takes two input streams, each a sequence of 2D coordinates, and outputs a single stream, the squared distances between each pair of input coordinates. In general, kernels may have zero or more input streams and one or more output streams. Kernels that perform *reductions* may generate scalar outputs instead of, or in addition to, output streams. The computation performed within the kernel loop bodies may be arbitrarily complex.

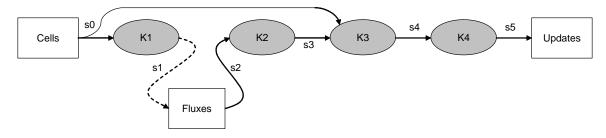

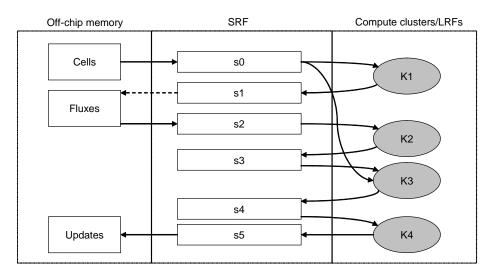

A more complex example – a simplified portion of a finite element method (FEM) expressed as a stream program – is shown in figure 2.2. The first kernel in this example (K1) receives an input stream of grid cells and generates a stream of indices in to an array of flux values stored in memory. These indices are used to lookup a sequence of flux values that form the input stream to kernel K2. K2 and subsequent kernels all produce output streams that are fed to later kernels as inputs, until the final kernel (K4) produces the application's outputs.

### Locality

This stream representation allows the programmer to express multiple levels of locality [RDK<sup>+</sup>98] that can be captured at various levels of the bandwidth hierarchy. *Kernel locality* is exploited by keeping all intermediate values generated during a kernel's execution in registers without writing them to higher levels of the memory hierarchy. Only the input and output streams of a kernel are read from or written to the memory hierarchy. *Producer-consumer locality* is exposed by forwarding the streams produced

Figure 2.1: Simple kernel computing the square of the distance between two sequences of coordinates

Figure 2.2: Stream representation of simplified finite element method

by one kernel to subsequent kernels as shown by the arrows in the example of figure 2.2. Ideally, these intermediate streams are captured entirely in on-chip memory, and do not generate off-chip memory accesses. Stream-level temporal locality is expressed by a single stream being consumed by multiple kernels. Once generated or fetched from memory, such streams are held in on-chip memory whenever possible for the entire duration of all uses. Finally, off-chip memory accesses are performed for reading

essential application inputs and writing final application outputs. This programming model matches well with the hierarchy of registers, on-chip memory, and off-chip memory present in most architectures. The registers are typically optimized for high bandwidth to sustain computation while the on-chip memory is optimized for large capacity to capture the working sets of applications and to hide memory latency.

The partitioning of applications in to kernels is driven by the available register and memory resources of the target architecture. Kernels are sized to minimize register spills, potentially partitioning loop bodies that generate more intermediate state than can be held in registers in to multiple kernels. At the application level, data sets that are too large to fit in on-chip memory are partitioned using a technique known as strip-mining [Lov77]. Strip-mining partitions the input data set in to segments known as strips such that all of the intermediate state for the computation on a single strip fits in on-chip memory. Thus multiple strips can be operated on in sequence, still limiting off-chip memory accesses to only the essential application inputs and outputs.

### **Parallelism**

The stream programming model also exposes multiple levels of parallelism inherent in the application. Data parallelism is expressed since the kernel loop body may be applied to many records of an input stream at once. In the solver example, the K1 kernel can be applied to all of the cells of its input stream in parallel, assuming the processor the stream program is being executed on has sufficient compute resources. ILP may also be exploited within the stream programming model by executing multiple independent operations among those that must be applied to a single data element (i.e. within a single iteration of the kernel loop body) in parallel. This may be achieved via pipelining and/or issuing multiple instructions per cycle.

Task-level parallelism across kernels is also exposed by the stream programming model. For example, kernels K1 and K2 in the solver example may execute in parallel on different processors, with the results of K1 being passed on to K2. In addition, the execution of a kernel may also be overlapped with the loading of application inputs for a subsequent kernel or storing of results generated by a previous kernel.

The stream programming model does not allow arbitrary accesses to global memory within kernels. This restriction enables inter-kernel access disambiguation to be performed at the stream level. In this context, applications that require data-dependent address generation must first generate a set of indices and use those to gather data in to contiguous streams which can then be used as inputs to subsequent kernels. Such an example is shown by the access to the flux array in the example of figure 2.2, where K1 generates the indices and the gathered stream is consumed by K2. Similarly, data dependent writes my be performed by scattering a result stream using an index stream after the completion of the kernel(s) that generates the results.

### **Stream Programming Languages**

Applications can be expressed in the stream programming model through specialized high-level languages. [Mat02] describes KernelC, a language for representing compute kernels, and StreamC, a language for orchestrating sequences of kernels and stream manipulations along with serial portions of code that are not data parallel. [BFH+04] presents Brook, a unified language for expressing kernel and serial code as well as the orchestration of kernels. [TKA02] describes streamit, a language for expressing stream computation as a collection of filters connected via pipelines, split-joins, and feedback loops. All of these languages are based on the familiar syntax of mainstream languages such as C/C++ and Java and add additional semantics to express streams and impose restrictions to enable data flow and dependency analysis among kernels or filters.

The benchmarks used for evaluations in this thesis were implemented in the stream programming model using the *StreamC* and *KernelC* programming languages. This allows the locality and parallelism in the applications to be exploited across a variety of processor architectures. In addition, novel techniques introduced in this thesis, such as indexed SRF access, epoch-based cache invalidation, and hybrid memory hierarchies, are evaluated within the context of stream programming. While these techniques also have potential applications outside the domain of stream programming, the locality exposed by this programming model enable these techniques to achieve a high degree of efficiency.

### 2.3 Stream Processor Architecture

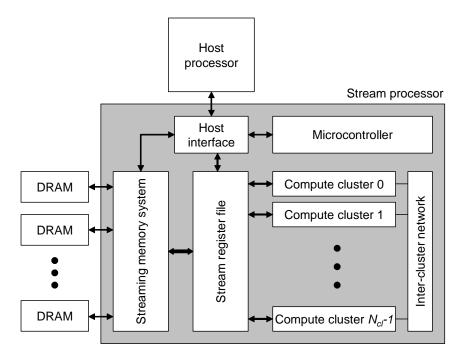

Stream processors are programmable processors that are optimized for executing programs expressed using the stream programming model. A block diagram of a stream processor is shown in figure 2.3.

Figure 2.3: Block diagram of a stream processor

The stream processor operates as a coprocessor under the control of the host processor, which is often a standard general-purpose CPU. A stream program executing on the host processor orchestrates the sequence of kernels to be executed and the necessary transfer of input and output data streams between the stream processor and off-chip memory. Kernel execution takes place directly on the stream processor from instructions stored in the microcontroller. New kernels may be loaded into the microcontroller as needed, possibly under explicit control of the host processor. The sequence of operations initiated by the host processor to orchestrate the stream program of figure 2.2 is shown in figure 2.4. The host interface of the stream processor issues the commands received from the host to the appropriate units as resources

become available, subject to dependencies among the commands.

```

load_microcode(K1);

load_microcode(K2);

load_microcode(K3);

load_microcode(K4);

load_stream(Cells, s0);

K1(s0, s1);

load_stream(Fluxes[s1], s2);

K2(s2, s3);

K3(s0, s3, s4);

K4(s4, s5);

store_stream(s5, Updates);

```

Figure 2.4: Sequence of host processor operations for simple FEM example

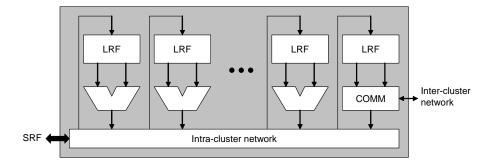

The arithmetic units of the stream processor are grouped in to n identical compute clusters. Each cluster consists of several functional units and associated registers. A block diagram of an example cluster organization is shown in figure 2.5. The local register files (LRFs) attached to each functional unit provide the input operands for that unit, and results are written to one or more of the LRFs via the intra-cluster network. Loop-carried state and other shared data may be communicated among compute clusters over the inter-cluster network via the COMM unit.

Figure 2.5: Block diagram of a single compute cluster

The microcontroller executes the instruction streams for the kernels and broadcasts the control for arithmetic operations to the compute clusters. Therefore all compute clusters execute the same sequence of operations in single-instruction multipledata (SIMD) fashion. While SIMD execution is not fundamental to stream computation, it amortizes the overhead of instruction storage and control sequencing hardware over all clusters, leading to implementation efficiencies. The data parallelism in applications is exploited by each compute cluster operating on a separate element of the input stream(s). Techniques such as predication and *conditional streams* [KDR<sup>+</sup>00] are used to provide efficient support for conditional execution within this SIMD framework.

The units within a compute cluster are controlled in VLIW fashion, exploiting the ILP available within a single iteration of the kernel loop. Loop unrolling and software pipelining may be performed at compile time to increase arithmetic unit utilization in kernels that do not have sufficient ILP to fill a large fraction of the VLIW issue slots.

The stream register file (SRF) is a large on-chip memory that provides storage for intermediate streams, capturing the producer-consumer and temporal locality that exists between kernels at stream granularity.

The *streaming memory system* includes one or more stream load/store units for transferring streams between off-chip memory and the SRF, memory controllers for off-chip DRAM, and optionally, an on-chip cache.

### 2.3.1 Bandwidth Hierarchy

The bandwidth hierarchy of a stream processor is formed by the LRFs, SRF, and the streaming memory system. Table 2.1 lists the bandwidths available at each level of the hierarchy for the Imagine [RDK<sup>+</sup>98] and Merrimac [DHE<sup>+</sup>03] stream processors. In these processors, each level of the hierarchy closer to the arithmetic units provides approximately an order of magnitude or more bandwidth than the previous level. By capturing data reuse in high-bandwidth levels, these architectures have demonstrated sustained high utilization on many arithmetic units despite limited off-chip memory

| 1     | 1   | • 1  | 1 / 1 |    |

|-------|-----|------|-------|----|

| ban   | dxx | 710  | 1+    | h  |

| ואמוו | UV  | vici | L L   | и. |

|                                        | Imagine<br>(400 MHz) | Merrimac<br>(1 GHz) |

|----------------------------------------|----------------------|---------------------|

| Local register files, aggregate (GB/s) | 435.2                | 3072                |

| Stream register file (GB/s)            | 25.6                 | 512                 |

| Memory system (GB/s)                   | 1.6                  | 64                  |

Table 2.1: Bandwidth hierarchy of Imagine and Merrimac processors

The bandwidth hierarchy of a stream processor also forms a close match to the levels of locality exposed by the stream programming model. The LRFs capture kernel locality while the SRF captures stream-level producer-consumer and temporal locality among kernels. Figure 2.6 shows how the example application of figure 2.2 maps to the bandwidth hierarchy.

Figure 2.6: Bandwidth hierarchy mapping of FEM example. Solid arrows represent stream transfers, dotted arrows represent index transfers

### Local Register Files

The total register capacity of a stream processor is divided between the SRF and LRFs. This allows the SRF to be optimized for high capacity to capture the working

set while the local registers are optimized for high bandwidth, albeit with smaller capacity. In order to sustain the necessary high bandwidth, the local registers are implemented in a distributed manner, consisting of several register files in each compute cluster. Each LRF has a small number of read ports that directly feed arithmetic units, and one or more write ports that are connected to the intra-cluster network. The high bandwidth for sustaining parallel computation is provided by the aggregate of all LRFs.

The implementation described above partitions the register set of a stream processor along multiple axes – between the SRF and LRFs, among the compute clusters, and the LRFs within each cluster. [RDK+00b] provides a detailed analysis of partitioned register implementations for stream processing, and shows that such architectures suffer only minimal performance loss compared to unified register architectures while achieving area and power savings of orders of magnitude. In addition, the distributed LRFs can be implemented in close physical proximity to the arithmetic units that they feed, further reducing the energy spent on operand accesses.

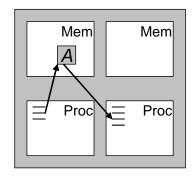

### Stream Register File

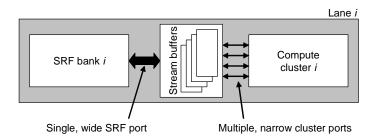

The SRF is partitioned in to  $N_{cl}$  banks, where  $N_{cl}$  is the number of compute clusters. As describe in [RDK+00b], each compute cluster is closely tied to a single SRF bank. A compute cluster and the associated bank of the SRF is referred to as a *lane* of the stream processor. A compute cluster can only access the bank of the SRF in its own lane.

The banked implementation reduces the number of SRF ports needed. Since each bank only needs to support one cluster, the SRF can be implemented using single-ported memories. In order to increase the SRF bandwidth of such an implementation, the single port of each SRF bank is several words wide. Therefore, each access reads or writes a contiguous block of words in the SRF. However, a compute cluster typically consumes or generates streams a single words at a time, but may require multiple streams to be accessed simultaneously for some kernels. This difference in SRF and compute cluster stream access characteristics is resolved by *stream buffers* as introduced in [RDK+00b] (not to be confused with the cache prefetch structure

of the same name described in [Jou98]). Stream buffers mediate the communication between the SRF and compute clusters as shown in figure 2.7 and provide a rate matching function between the two units. On an SRF read of stream i, a wide block of several data words is read and placed in to stream buffer i. On cluster reads of stream i, the block of data is funneled into the compute cluster a single word at a time. The process is reversed for write streams, collecting the individual words written by the clusters in to the stream buffer until sufficient data is available to perform a block write in the SRF. The stream buffers also provide the abstraction of sustaining multiple concurrent streams by time-multiplexing the single, wide SRF port among several active streams, each mapped to a different stream buffer. Access to the single SRF port among multiple active streams is managed through dynamic arbitration. Data streams are distributed among SRF banks at the granularity of records such that record r of a stream maps to SRF bank r mod  $N_{cl}$ . The SIMD nature of the execution applies to the SRF as well. During an SRF access, the same block is accessed within every bank.

Figure 2.7: Stream buffers match the access characteristics of the SRF and compute clusters (only a single lane is shown for simplicity)

The SRF also acts as a staging area of stream transfers to and from memory. Input streams are loaded in to the SRF and held there until the kernel that consumes them is executed. Similarly, application results generated by kernels are held in the SRF until written to memory. Therefore, the SRF is a critical component in enabling the overlap of memory accesses with computation since kernels can continue to operate on data in the SRF while memory transfers take place in the background.

### Streaming Memory System

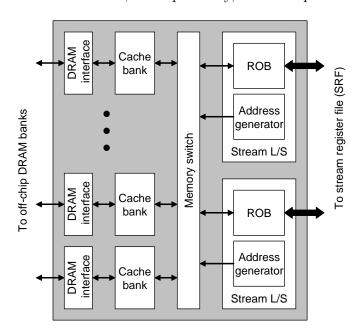

The streaming memory system (SMS) manages the transfer of streams between offchip memory and the SRF. A block diagram of the key components of the SMS is shown in figure 2.8, which includes one or more stream load/store (L/S) units, the memory switch, DRAM interfaces, and optionally, an on-chip cache.

Figure 2.8: Block diagram of the streaming memory system shown with two stream load/store units and an optional on-chip data cache

Once a stream L/S units is setup for a stream transfer by the host processor, the address generator produces a sequence of memory addresses that correspond to the locations to be accessed in off-chip memory. In the case of a read stream, those locations are read, and the data is transferred to the reorder buffer (ROB) in the L/S unit. The accesses may return from the memory out of sequence, requiring the ROB to recreate the intended stream order. The ROB also acts as a stream buffer, interfacing the memory system to the SRF in much the same way the stream buffers for the compute clusters do. In the case of write streams, the data is read from the SRF via the ROB, and is written to memory. The number of ROB entries is

determined by the number of memory requests necessary to be outstanding at a time in order to achieve high bandwidth utilization as described in section 2.1.

An optional cache may also be integrated in to the memory system. However, unlike caches in scalar processor architectures, the main objective of the cache is not to reduce the average memory access latency (i.e. sufficient outstanding accesses to fill the memory pipeline to off-chip memory must still be supported, even in the presence of a cache). The main purpose of the cache is to provide bandwidth filtering by capturing potentially reused data, reducing the the bandwidth that must be sustained from off-chip memory. However, since not all stream accesses may have data reuse that can be exploited through caching, the programmer or compiler may selectively specify which accesses are to be cached.

The off-chip memory of stream processors consist of commodity DRAM. The memory controllers integrate the DRAM controllers on chip, and several DRAM channels are supported to increase bandwidth. The memory interfaces also implement *memory access scheduling* to optimize the performance of the off-chip DRAMs [RDK+00a].

Despite the presence of an efficient bandwidth hierarchy, performance of applications (or segments of applications) may still be constrained by bandwidth if the computation performed per unit of data accessed at any level of the hierarchy is less than what can be sustained by the processor architecture. This is a particular concern for off-chip memory, which forms the lowest bandwidth level of the hierarchy. Therefore, a key focus of this thesis is to identify and evaluate enhancements to on-chip levels of the bandwidth hierarchy that allow more efficient utilization of scarce off-chip memory bandwidth by eliminating non-essential accesses.

### 2.4 Alternative Data Parallel Architectures

The following sections briefly introduce vector and multi-context architectures and CPU media extensions – three commonly used alternatives to stream processors for exploiting data parallelism. A more comprehensive discussion of the similarities and relative strengths of these architectures from a bandwidth hierarchy perspective will be presented in chapter 3.

#### 2.4.1 Vector Processors

Vector processing expresses an application as sequence of vector operations operating on vectors of data. A vector is an array of one-word data elements of a primitive type, and a vector operation is a single arithmetic operation such as an add or a multiply that is applied to all elements of its input vectors. Figure 2.9 revisits the simple computation of figure 2.1, but expressed as a sequence of vector operations. Conceptually, a single operations is applied to all elements of a vector before any operations are applied to the resulting output. This differs from stream processing where, conceptually, all operations on a single input stream element are applied before any operations are applied to the subsequent input elements. Therefore, vector processing differs from stream processing on the granularity at which the data-parallel computation is expressed.

Figure 2.9: Vector processing representation of squared distance computation

Vector processing was originally proposed in the context of high-performance supercomputers [Rus78]. Modern implementations such as Cray X-1 [Cra02] and NEC SX family [KTHK03] continue to target scientific computing. However, the applicability of vector processing to other data parallel application domains, such as media processing, has been demonstrated [Koz02].

Modern vector processors share many implementation similarities with stream processors. Arithmetic units within a vector processor are grouped in to *vector pipes*. Multiple vector pipes may operate in parallel using SIMD execution, operating on independent vector element similarly to the compute clusters of a stream processor. Vectors are stored in a *vector register file* (VRF) that captures the intermediate results

between vector operations. The VRF is multi-banked with independent banks associated with vector pipes, each bank providing high bandwidth access to its associated pipe only. Vector processors also exploit ILP, executing multiple vector instructions in parallel. A technique known as *chaining*, first introduced in the Cray-1 [Rus78], is used to forward results between arithmetic units within the same pipe that are executing different vector instructions in parallel. Simple chaining requires that the chained instructions be carefully synchronized, but requires no significant buffering of intermediate results or additional ports to the VRF. A more general extension of the idea, *flexible chaining*, relaxes the synchronization constraints at the cost of additional buffering and/or VRF ports for chained intermediate results.

Most vector architectures rely on the VRF to both provide the bandwidth necessary to sustain computation and to capture the working set. However, some vector architectures share a further commonality with stream processors in that they employ a 2-level register hierarchy similar to the SRF and LRFs. For example, the NEC SX family of vector processors partition the register space in to a small number of vector arithmetic registers (8 256-element vectors in the case of the SX-6) and a larger number of vector data registers (64 256-element vectors in the SX-6) [SX-02]. The vector arithmetic registers provide the operand bandwidth for the arithmetic units. The vector data registers cannot be directly operated on, and must be explicitly copied to an arithmetic register before being operated on. However, results of vector operations may be directly written to both types of registers.

A detailed discussion of vector processors and their design tradeoffs can be found in [Asa98].

#### 2.4.2 Multi-threaded Processors

Multi-threaded architectures can also be used to exploit data parallelism. Conceptually, every iteration of a data parallel loop can be viewed as a separate thread or context, enabling stream programs to be mapped easily to such architectures. Therefore, long memory latencies can be overlapped with computation on other contexts which operate on independent data elements. Parallel execution among data elements

may be achieved in multi-threaded processors using techniques such as *simultaneous* multi-threading [TEL98], which executes instructions from multiple threads concurrently on a single processor, or by integrating multiple processor cores on a single chip.

# 2.4.3 Media Extensions to General-purpose CPUs

Virtually all major general-purpose CPU families have incorporated some form of support for exploiting data parallelism targeted at media applications [PW96; TONH96; DDHS00; Lee96]. These techniques enable a small number of SIMD computations to be specified using a single instruction to be executed on data read from a wide register file. However, these extensions do not exploit data parallelism to the degree that specialized data parallel architectures such as stream or vector processors do. Media extensions provide neither special support for overlapping computation with memory accesses in order to tolerate memory latency (beyond what support exists for scalar computation in the CPU), nor do they provide a specialized bandwidth hierarchy to sustain computation on very large numbers of arithmetic units. Further, each instruction, which specifies only a small number of operations, must be issued via the out-of-order scalar issue mechanism present in most modern processors, incurring high energy overheads.

# 2.5 DRAM Characteristics

Most modern data parallel architectures use commodity DRAM for main memory due to cost, density, and power considerations. This section provides a brief introduction to DRAM access timing and characteristics in order to understand the impact on the performance of stream accesses from off-chip memory.

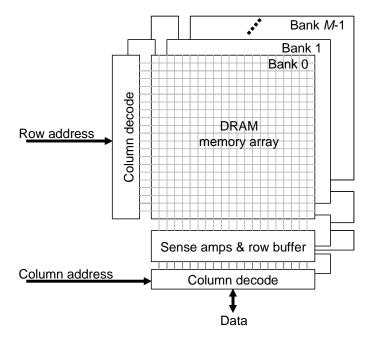

Modern DRAM memories, such as DDR2 SDRAM and DRDRAM, contain multiple internal banks, and the cells within each bank are arranged as a 2D array with sense amplifiers along one edge (or two parallel edges) as shown in figure 2.10. Addressing for DRAM access is done in two stages. During row access (also referred

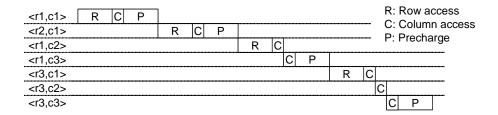

to as activate), an entire row of the array is read via the sense amplifiers and stored in latches called the row buffer. Data in the row buffer is referred to as the active row, and portions of it are read or written using column accesses. Therefore, typical DRAM access consists of a row access followed by one or more column accesses. When data from a different row of the DRAM is needed, the currently active row is closed, i.e. written back to the DRAM cells, and the array bitlines precharged to prepare for the next row access. Typically, new row activations take significantly longer than a column access to an already active row. Some critical latencies for a current DDR2 SDRAM part [Mic03] are summarized in table 2.2. Figure 2.11 shows a simple example of a sequence of accesses to a single DRAM bank and the ensuing operations. As can be seen from this simple example, the bandwidth and the distribution of access latencies of DRAMs depend heavily on the access pattern, which varies the mix of row and column accesses.

Figure 2.10: Internal structure of a modern DRAM

DRAMs support a few options to reduce the impact of long precharge and row access latencies:

Figure 2.11: Example DRAM access operations schedule

| Operation                                                   | Latency          |

|-------------------------------------------------------------|------------------|

| Minimum time from row access to column access $(t_{RCD})$   | 20ns             |

| Column access to data read time (CL)                        | 20ns             |

| Minimum time between successive column accesses $(t_{CCD})$ | $10\mathrm{ns}$  |

| Minimum time from precharge to next activate $(t_{RP})$     | 20ns             |

| Minimum time between row accesses to same bank $(t_{RC})$   | $65 \mathrm{ns}$ |

Table 2.2: Example SDRAM access latencies (Micron 256Mb DDR2, speed grade -5)

- Burst mode rapidly accesses multiple consecutive data elements from the active row following a single column access command. Such accesses provide high throughput for sequential access patterns.

- Multiple banks within a DRAM chip allow overlapping of commands to different banks. While the address pins of the DRAM are occupied during the communication of each command, this approach enables some fraction of the long latency precharge and row activations to be overlapped with operations in other banks.

- Open row policies maintain the active row after pending access(es) complete, anticipating subsequent accesses to map to the same row. If this is indeed the case, row accesses are avoided. If subsequent accesses map to other rows, both precharges and row accesses are incurred. Alternatively, closed row policies proactively close the active row and precharge the array when pending accesses to the active row complete. This avoids the precharges but incurs row accesses for subsequent operations regardless of the row they map to.

# 2.6 Emerging Trends

Several trends in applications and implementation technology make memory system design even more crucial for stream processing.

While stream processors were originally proposed to handle media and signal processing applications with straightforward data access patterns, there have been recent efforts to extend stream processing to more complex applications in signal processing as well as other application domains such as scientific computing [Raj04; DHE+03]. These applications require the memory system to support a wider range of access patterns. Therefore, extensions to the streaming bandwidth hierarchy that efficiently support a wider range of accesses enables the high performance potential of stream processors to be realized over a larger class of applications.

At the same time, implementation technology scaling continues to exponentially increase the number of devices available on a single chip, increasing the potential compute capability of processors. However, off-chip memory bandwidth and latency are scaling at a much lower rate [Pat04], increasing the demands on the bandwidth hierarchy to make ever more efficient use of the scarce off-chip bandwidth. A number of tradeoffs need to be evaluated in order to determine how best to use a storage hierarchy to achieve the best gains in performance, energy efficiency, and/or off-chip memory bandwidth reductions for stream processors.

The increasing number of devices also makes it possible to integrate stream processors or other data parallel processors along with general purpose CPUs on the same die in order to accelerate media processing and other similar tasks [EAE<sup>+</sup>02; Bor04]. In such implementations, the data parallel processor must share portions of the memory hierarchy designed for the general-purpose processor. Insights drawn from dedicated stream processor memory hierarchies can be used to develop techniques to adapt the general-purpose memory hierarchies to better suit stream processing in these implementations.

# 2.7 Summary

This chapter was intended to provide an overview of concepts central to stream processing, and a brief introduction to stream processing itself. We explored the characteristics of data parallel application classes that make them ideal candidates for exploiting the raw potential of today's VLSI circuit technology. The high degree of parallelism available in these applications were identified as the critical aspect that enables parallel computation on many arithmetic units while tolerating the long off-chip memory access latencies of modern processors.

The stream programming model was introduced as a way of expressing data parallel applications in a manner that exposes the inherent parallelism as well as the available data locality. This programming model enables filtering of the high operand bandwidth needed to sustain computation by capturing the exposed locality at multiple levels of a bandwidth hierarchy. Stream processors, a class of architectures optimized for executing applications expressed using the stream programming model was also introduced in this chapter, along with a discussion of the specific implementation of the bandwidth hierarchy in these processors.

This chapter also provided a brief overview of alternative programmable data parallel architectures, such as vector and multi-threaded processors. We will expand on this introduction in terms of the relative strengths of these architectures from the perspective of bandwidth hierarchy design in chapter 3. A short introduction was also presented to modern DRAMs, a crucial component in the memory systems of most data parallel architectures. Finally emerging trends in applications and implementation technology that encourage further research on memory systems for stream computing was presented.

The next several chapters of this thesis will build on the background provided in this chapter to identify opportunities to broaden the applicability of stream processing, and to further improve the performance and implementation efficiency of bandwidth hierarchies for data parallel architectures.

# Chapter 3

# Granularity of Data Parallelism

An important aspect of data parallel computing is the granularity at which the parallelism is expressed. In the case of a stream processing, data parallelism is expressed at the granularity of stream elements, or entire records. An alternative is to express the parallelism at the granularity of individual words, as is done in vector processing. This distinction leads to two important implications for memory hierarchy design. First, since the order of operations differs in these two cases as described in section 2.4.1, the amount of intermediate state generated, and hence the amount of register space needed to store that state, is different. Second, the order in which the data words are accessed from memory is different in the two cases, leading to differences in the access patterns seen by the memory hierarchy. This chapter explores the impact that expressing data parallelism at record and word granularity has on both these aspects.

# 3.1 Register Capacity Requirements