# DESIGN OF CMOS RECEIVERS FOR PARALLEL OPTICAL INTERCONNECTS

#### A DISSERTATION

SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING

AND THE COMMITTEE ON GRADUATE STUDIES

OF STANFORD UNIVERSITY

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

Azita Emami-Neyestanak August 2004 © Copyright by Azita Emami-Neyestanak 2004 All Rights Reserved I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

> Mark A. Horowitz (Principal Adviser)

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

David A. B. Miller

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

Bruce A. Wooley

Approved for the University Committee on Graduate Studies.

### Abstract

The growing demand for high-bandwidth communication between integrated circuit chips calls for large numbers of high-speed inputs and outputs (IOs) per chip. IO data rates have increased to the point where electrical signaling is now limited by the channel properties. In order to achieve multi-Gb/s data rates, complex designs that equalize the channel are necessary.

Using optics for chip-to-chip interconnections is promising since the optical channel dispersion and cross-talk are small. In this work we demonstrate the possibility of building small and low-power optical receivers that facilitate large numbers of IOs. A new double sampling/integrating front-end is proposed and implemented. Unlike prior designs, this receiver removes the need for a gain stage that runs at the data rate, making it suitable for low-power implementations. This front-end allows a time-division multiplexing technique to support very high data rates. The dynamic range of the integrating input node can be improved by a proposed decision-directed common-mode control loop, which reduces the dependency of the dynamic range on the power supply voltage.

The required receive clock can be generated in many ways. While the standard oversampled clock recovery is possible, it needs extra clock phases in the middle of main data samples. In order to reduce the power, a baud rate clock recovery technique is proposed and implemented as part of a transceiver array test-chip. The resulting transceiver consumes less than 150mW per channel at 5.0 Gb/s in a  $0.25 \mu \text{m}$  CMOS technology. If projected to a 90nm CMOS technology, 15 Gb/s data rate and 30 mW power per IO are possible, which allow more than 10 Tb/s chip-to-chip bandwidth, with up to one thousand IOs per chip.

### Acknowledgements

During my graduate studies in Stanford University, I had the privilege of learning from the best teachers and receiving support from the most caring friends. This work would not have been possible without any of the two.

First of all, I would like to thank my Ph.D. advisor Professor Mark Horowitz. Mark's knowledge, vision and personality make him the greatest advisor and teacher one could ever wish for. Every single meeting with Mark helped me to go another step forward in my research, and motivated me to learn more. Mark's enthusiasm and care were the driving forces for creation of new ideas in this work. He also effectively helped me to improve my public speaking and writing skills. I sincerely thank him for his kindness and patience.

I gratefully acknowledge my co-advisor Professor David Miller for his invaluable advice and help. Professor Miller was the one who initiated this research and inspired this project as a collaboration between the two research groups. Working in his laboratory and with his students was a great opportunity for me to expand my knowledge to the area of photonics. I also would like to thank him for being a member of my oral defence and reading committees.

I would like to extend my gratitude to Professor Bruce Wooley for his advice, encouragements and help throughout my years at Stanford, and for serving as members of my oral defence and reading committees. I sincerely appreciate his kindness.

Faculty of Electrical Engineering department at Stanford are among the most brilliant teachers in the world and I had the opportunity of learning from many of them. Particularly, I would like to express my gratitude to Professor Fabian Pease, chair of my orals committee and Professor Tom Lee, who both helped me during my first year at Stanford.

With no doubt, a great aspect of being one of Mark's students was to be in a friendly and highly cooperative research group. This thesis builds upon the work done by many former members of the Horowitz group. I would like to thank Samuel Palermo, Hae-Chang Lee and Elad Alon for helping in the design of my chip. I also thank Jaeha Kim and Dean Liu for their technical help and for answering my numerous questions. I am also grateful for technical discussions with Vladimir Stojanovic, Ken Mai, Ron Ho, Kun-Yung Chang, Ken Yang and Bill Ellersik. I appreciate the friendship of other former and current students in the Horowitz group, Bennett Wilburn, Michal Smulski, Evelina Yeung, Gu-Yeon Wei, Amin Firoozshahian, Francois Labonte, Alex Solomatnikov, Vicky Wong and Dinesh Patil.

Members of Professor Miller's group greatly helped me in the optical testing of my chips. I would like to thank Aparna Bhatnagar, Gordon Keeler, Noah Helman and Diwakar Agarwal for the integration of optical devices, lab set-ups and technical discussions.

This work was possible with the generous support from National Semiconductor, Vitesse Semiconductor, DARPA and MRCO IFC. I also would like to thank CIS staff members, computer administrators and Mark's administrators, Teresa Lynn, Penny Chumley and Taru Fisher for creating an amazing work environment for us. I sincerely thank CIS former students Hirad Samavati, Joel Dawson and Lalit Nathawad who took the responsibility of National tape out.

The highly academic environment at Sharif University of Technology helped me to build the required background in engineering and encouraged me to pursue my graduate studies abroad. I sincerely thank my undergraduate advisors Professor Sharif-Bakhtiyar, Professor Fotovat, and my teacher Professor Jahanbeglo.

My first exposure to science and engineering goes back to my high-school years. I was extremely fortunate to go to Farzanegan, with the most dedicated and caring teachers. I would like to thank, Ms. Poorsaeed, Mr. Niusha, Mr. Helli, Ms. Mokhtari, Ms. Rohani, Mr. Kazemi and Mrs Haerizadeh.

I would like to thank my friends Valeria Bertacco, Vace Shakoori, Fatemeh Jalayer, Yasamin Mostofi, Mahmood Reza Kasnavi, Dara Ghahremani, Farid Nemati, Ali

Hajimiri, Ramin Farjad-rad, Amy Droitcour, Ardavan Maleki, Mina Matin, Parisa Gholami and Nogol Rashidi for making Stanford a fun place to live and work.

I sincerely thank my best friend Kaveh Hosseini who helped me to go forward in every stage of my graduate studies. His encouragements and friendship brought peace and happiness to my life.

My brother Sohrab has been an amazing mentor. He always inspired and motivated me to do my best. All these years, my lovely sisters Maryam and Mitra eased the hardship of being away from home by their love, beautiful gifts and letters. My deepest love and gratitude go to these three.

I dedicate this thesis to my parents, Mr. Akbar Emami-Neyestanak and Mrs. Khatoon Hadavi-Neyestanaki for their lifelong efforts to provide the best for me. I deeply appreciate their endless love, support and sacrifices.

At the end, I cherish the memory of Masoomeh Hadavi and Zhila Asghari.

### Contents

| $\mathbf{A}$ | Abstract Acknowledgements |         |                                      | iv           |  |

|--------------|---------------------------|---------|--------------------------------------|--------------|--|

| $\mathbf{A}$ |                           |         |                                      | $\mathbf{v}$ |  |

| 1            | Intr                      | oduct   | ion                                  | 1            |  |

|              | 1.1                       | Organ   | nization                             | 3            |  |

| 2            | Bac                       | kgrou   | nd                                   | 7            |  |

|              | 2.1                       | Electr  | ical Link Basics                     | 7            |  |

|              |                           | 2.1.1   | Channel Termination                  | 10           |  |

|              |                           | 2.1.2   | Transmitter Design                   | 12           |  |

|              |                           | 2.1.3   | Receiver Design                      | 13           |  |

|              |                           | 2.1.4   | Time Division Multiplexing           | 14           |  |

|              | 2.2                       | Clock   | Generation and Recovery Loops        | 15           |  |

|              |                           | 2.2.1   | Phase-Locked Loop                    | 16           |  |

|              |                           | 2.2.2   | Voltage and Timing Margins           | 18           |  |

|              |                           | 2.2.3   | Clock Recovery                       | 19           |  |

|              | 2.3                       | Chanr   | nel                                  | 24           |  |

|              |                           | 2.3.1   | Equalization                         | 27           |  |

|              | 2.4                       | Summ    | nary                                 | 31           |  |

| 3            | Rec                       | eiver l | Design for Optical Interconnects     | 33           |  |

|              | 3.1                       | High-S  | Speed Optical Interconnects Overview | 34           |  |

|              |                           | 3.1.1   | Photodetectors                       | 36           |  |

|   | 3.2 | Prior Art in Design of Optical Receiver Front-Ends | 88         |

|---|-----|----------------------------------------------------|------------|

|   |     | 3.2.1 Front-End Design Challenges                  | 8          |

|   |     | 3.2.2 Transimpedance Amplifiers                    | 10         |

|   |     | 3.2.3 TIA Design Consideration                     | 16         |

|   |     | 3.2.4 Integrating Front-Ends                       | 18         |

|   | 3.3 | Double Sampling/Integrating Front-End              | 52         |

|   |     | 3.3.1 Receiver Design Overview                     | 52         |

|   |     | 3.3.2 Sampling and Comparison                      | 55         |

|   |     | 3.3.3 Filter and Current Feedback                  | 60         |

|   |     | 3.3.4 Supporting Circuits                          | 52         |

|   |     | 3.3.5 Performance Analysis                         | 64         |

|   | 3.4 | Receiver Testing                                   | 8          |

|   | 3.5 | Results and Performance Comparison                 | 70         |

|   | 3.6 | Summary                                            | 73         |

| 4 | Sca | aling and Common-Mode Control 7                    | <b>'</b> 5 |

|   | 4.1 | Double Sampling Front-End Scaling                  | 6          |

|   | 4.2 | Decision Directed Current Control                  | 9          |

|   | 4.3 | TIA Scaling                                        | 34         |

|   | 4.4 | Summary                                            | 86         |

| 5 | Clo | ock Generation and Timing Recovery 8               | 7          |

|   | 5.1 | 2X OverSampled Clock Recovery                      | 88         |

|   | 5.2 | Baud Rate Clock Recovery                           | 39         |

|   |     | 5.2.1 Principles of Baud Rate Clock Recovery 9     | 0          |

|   |     |                                                    | 92         |

|   | 5.3 | Optical Transceiver Test-Chip                      | )4         |

|   |     | 5.3.1 Clocking High-Level Architecture             | 95         |

|   |     | 5.3.2 CDR Building Blocks                          | 7          |

|   | 5.4 | Experimental Results                               | )4         |

|   | 5.5 | Design Improvements                                | )6         |

|   | 5.6 | Summary                                            | 0          |

| 6            | Conclusions  | 112 |

|--------------|--------------|-----|

| $\mathbf{A}$ | TIA Analysis | 115 |

| Bi           | bliography   | 119 |

### List of Tables

| 3.1 | Chip performance summary                                | 72  |

|-----|---------------------------------------------------------|-----|

| 5.1 | 4-bit patterns with phase information for baud rate CDR | 92  |

| 5.2 | Chip performance summary                                | 105 |

## List of Figures

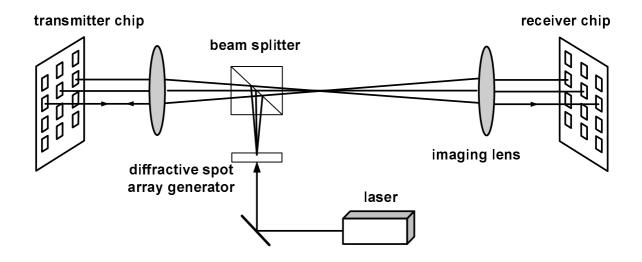

| 1.1  | Parallel optical chip-to-chip interconnection over free space                      | 3  |

|------|------------------------------------------------------------------------------------|----|

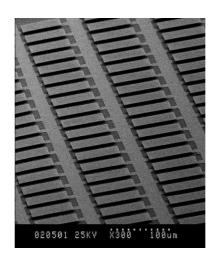

| 1.2  | Array of GaAs optical devices, flip-chip bonded to the silicon CMOS                |    |

|      | chip                                                                               | 4  |

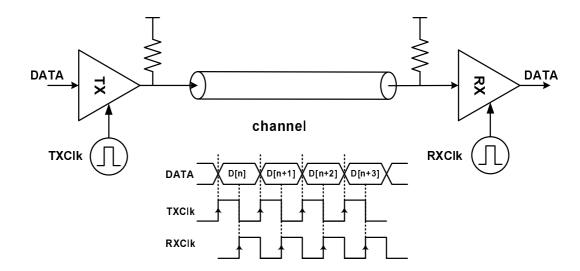

| 2.1  | Components of a basic electrical link                                              | 8  |

| 2.2  | Plesiochronous serial link                                                         | 9  |

| 2.3  | Parallel source-synchronous link                                                   | 10 |

| 2.4  | Electrical signaling (a) with no termination, (b) properly terminated .            | 11 |

| 2.5  | Data transmission schemes (a) low-impedance, voltage mode drive, (b)               |    |

|      | high-impedance, current mode drive                                                 | 12 |

| 2.6  | Current mode driver                                                                | 13 |

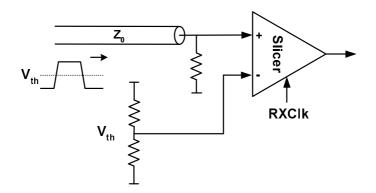

| 2.7  | Data resolution at the receiver using a slicer                                     | 14 |

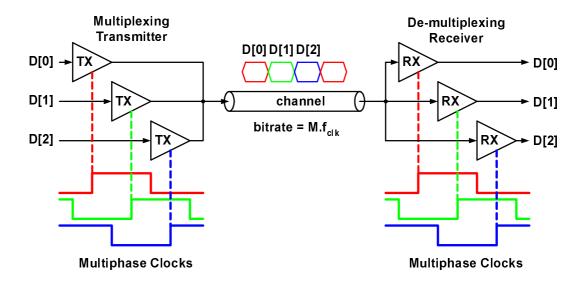

| 2.8  | Time division multiplexing and parallelism                                         | 15 |

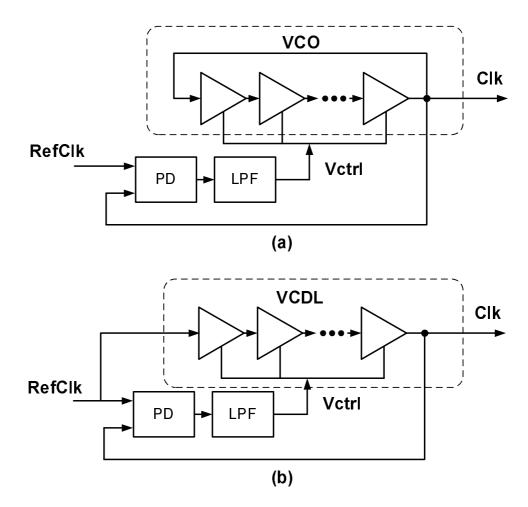

| 2.9  | Phase-locked loops (a) a VCO-based PLL, (b) a VCDL-based DLL .                     | 17 |

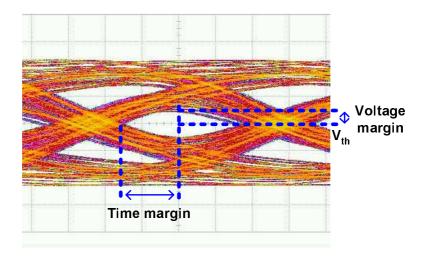

| 2.10 | Receiver voltage and timing margins                                                | 19 |

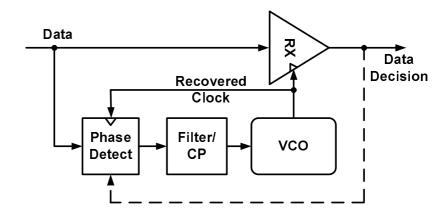

| 2.11 | Timing recovery from the received data                                             | 20 |

| 2.12 | $2\mathbf{x}$ over-sampled CDR with two clock phases for data and phase resolution | 21 |

| 2.13 | 2x over-sampled phase detection, loop error signal and implementation              | 22 |

| 2.14 | Channel pulse response and criteria for baud rate recovery                         | 24 |

| 2.15 | Signal path and channel components in a typical backplane                          | 25 |

| 2.16 | Typical frequency transfer function of a backplane channel                         | 26 |

| 2.17 | Dispersion in a band-limited channel                                               | 26 |

| 2.18 | Signaling methods (a) single-ended signaling, (b) differential signaling           | 27 |

| 2.19 | Linear equalization, flattens the frequency response                               | 28 |

| 2.20 | Linear equalization at the receiver with FIR filtering                         | 29 |

|------|--------------------------------------------------------------------------------|----|

| 2.21 | Linear equalization at the transmitter with FIR filtering                      | 29 |

| 2.22 | Decision feedback equalization                                                 | 30 |

| 3.1  | Synchronous optical transmission over free space                               | 36 |

| 3.2  | Equivalent electrical model of a reverse-biased photodiode                     | 37 |

| 3.3  | Simplified model of a photodiode                                               | 39 |

| 3.4  | Simple resistive optical front-end                                             | 40 |

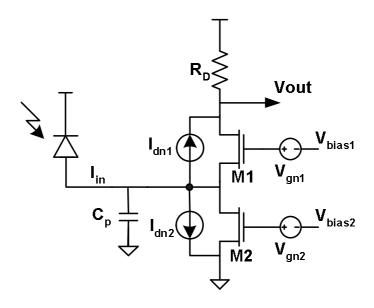

| 3.5  | Common-gate TIA and its noise sources                                          | 41 |

| 3.6  | Regulated cascode TIA input satge                                              | 42 |

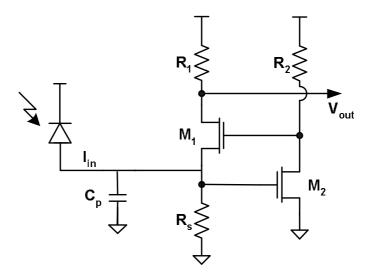

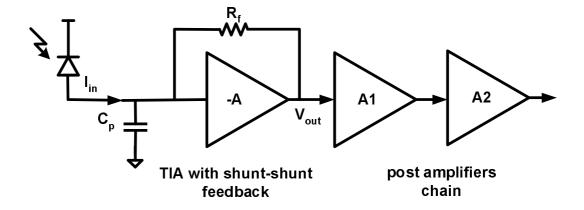

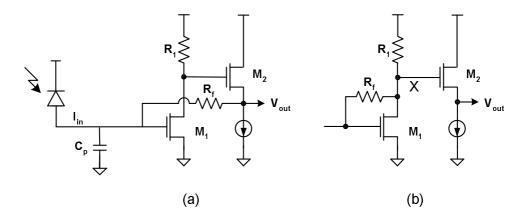

| 3.7  | Shunt-shunt feedback TIA with limiting amplifiers                              | 44 |

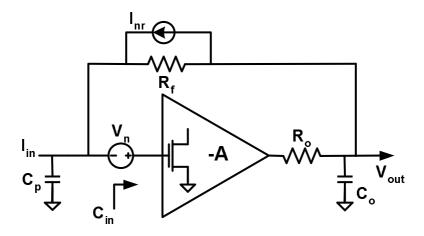

| 3.8  | Shunt-shunt resistive-feedback TIA model                                       | 44 |

| 3.9  | Common-source shunt-shunt feedback TIA designs                                 | 45 |

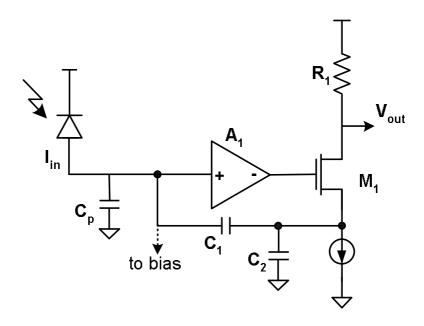

| 3.10 | Capacitive network feedback TIA                                                | 46 |

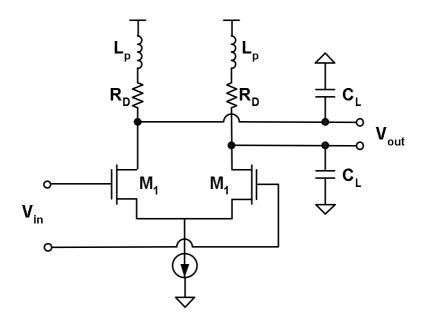

| 3.11 | Inductive peaking for limiting amplifiers                                      | 49 |

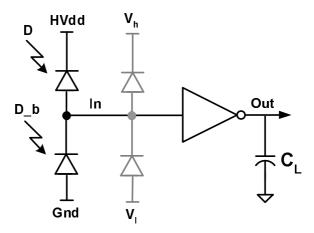

| 3.12 | Receiver-less front-end with totem-pole and clamp diodes                       | 50 |

| 3.13 | Sense-amp-based front-end                                                      | 51 |

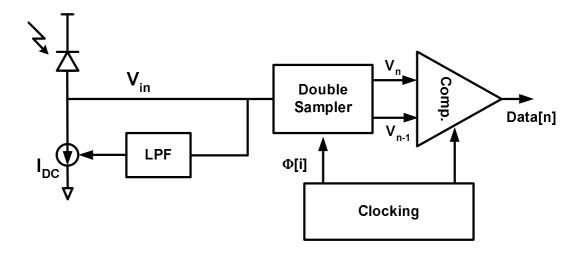

| 3.14 | Block diagram of double sampling/integrating front-end                         | 53 |

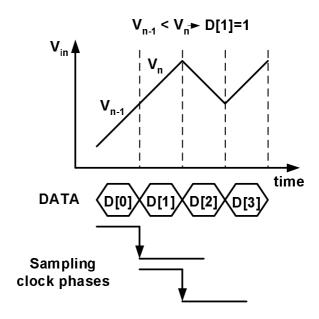

| 3.15 | Data resolution and input voltage waveform of the integrating front-end        | 54 |

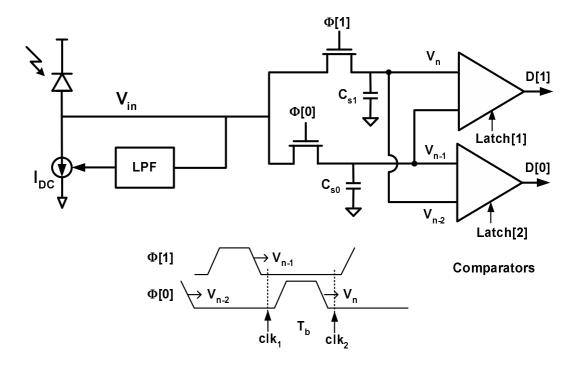

| 3.16 | Double sampling/integrating front-end implementation                           | 54 |

| 3.17 | De-multiplexing double sampling/integrating front-end                          | 55 |

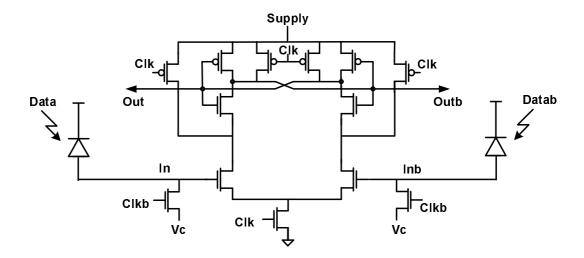

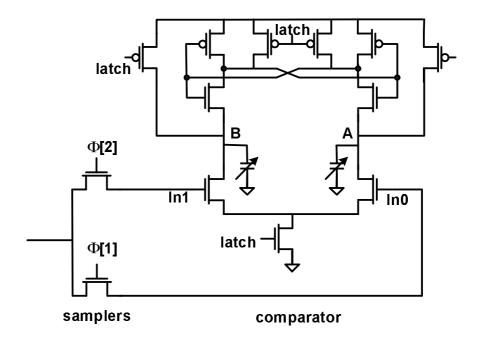

| 3.18 | Double sampler and comparator circuits                                         | 56 |

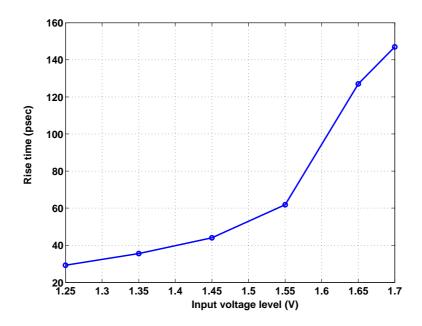

| 3.19 | Rise-time of the NMOS sampler in response to a $10 \text{mV}$ step voltage as  |    |

|      | a function of input voltage level                                              | 57 |

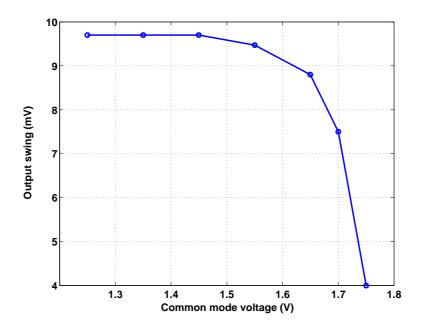

| 3.20 | Output voltage swing of the sampler with a $10\mathrm{mV}$ step voltage at the |    |

|      | input as a function of input voltage level                                     | 58 |

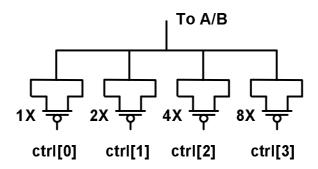

| 3.21 | PMOS adjustable capacitors for offset compensation                             | 59 |

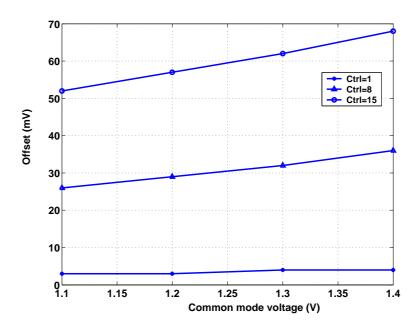

| 3.22 | Input-referred offset as function control signals and input common-            |    |

|      | mode voltage                                                                   | 60 |

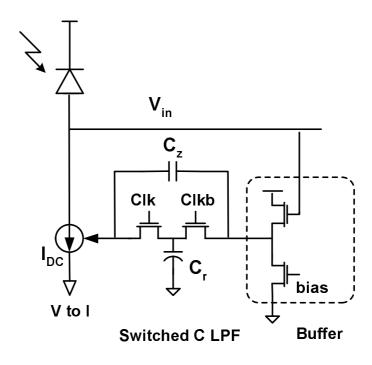

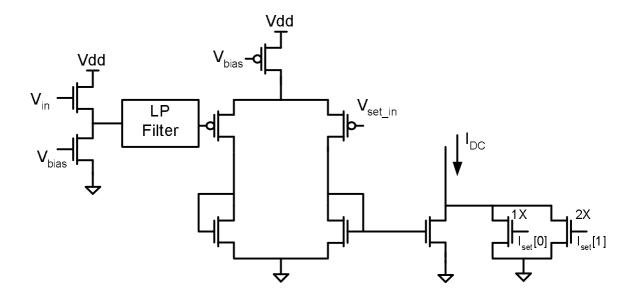

| 3.23 | Feedback loop with low-pass-filter to adjust $I_{DC}$                          | 61 |

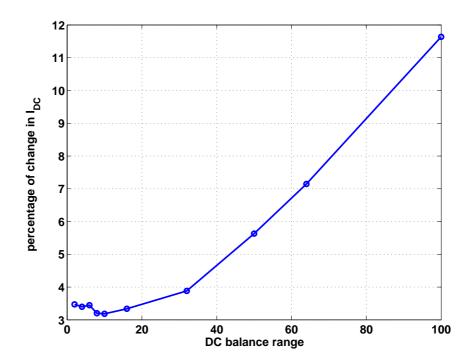

| 3.24 | Inc. variations with the DC-balance range of input data                        | 62 |

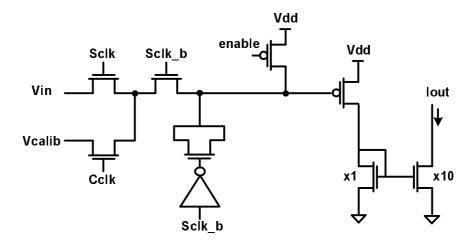

| 3.25 | Voltage to current conversion for $I_{DC}$ loop                                                 | 63 |

|------|-------------------------------------------------------------------------------------------------|----|

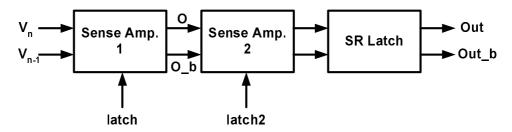

| 3.26 | Comparator and following stages of sense-amp and SR latch $$                                    | 63 |

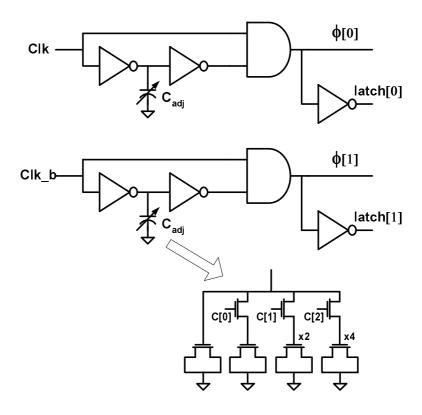

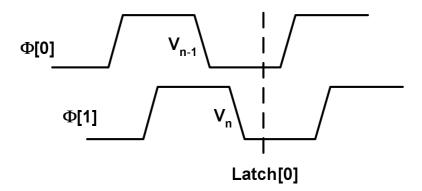

| 3.27 | Chopping the clock for 1:2 de-multiplexing                                                      | 64 |

| 3.28 | Multi-phase clocking, which automatically allows time for comparison                            | 65 |

| 3.29 | Sampler and half circuit of the StrongArm latch comparator                                      | 66 |

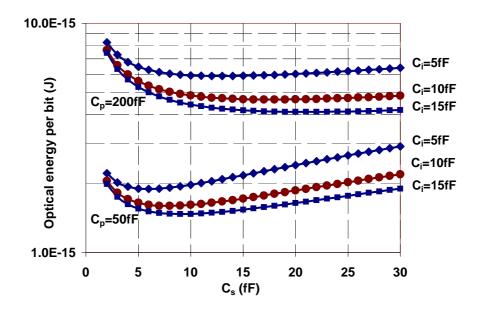

| 3.30 | Required optical energy per bit versus $C_s$ , $C_i$ and $C_p$ assuming $n=5$ ,                 |    |

|      | $R = 0.5 \text{A/W}, SNR = 36 \text{ (BER} = 10^{-10}), \text{ and } A_c = 1 \dots \dots \dots$ | 68 |

| 3.31 | Analog sampler for monitoring the input voltage waveform                                        | 69 |

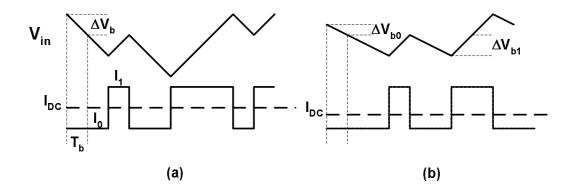

| 3.32 | Effect of sending unbalanced input data stream to the receiver, (a)                             |    |

|      | balanced input data (b) unbalanced input data, $\Delta V_b = 2\Delta V_{b0}$                    | 70 |

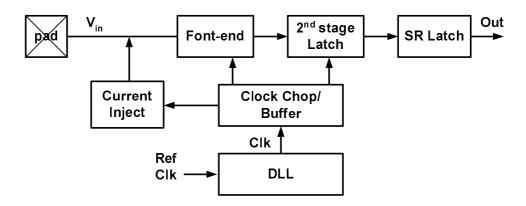

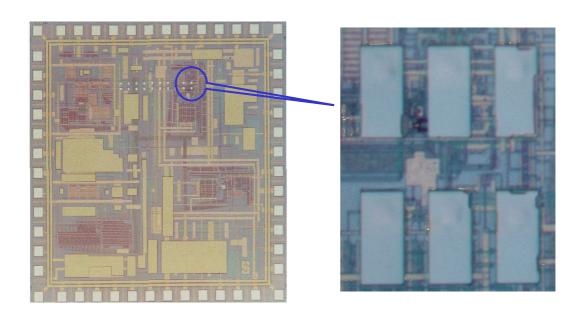

| 3.33 | Top level block diagram of the first receiver test-chip                                         | 71 |

| 3.34 | Fabricated test-chip with the flip-chip bonded devices                                          | 72 |

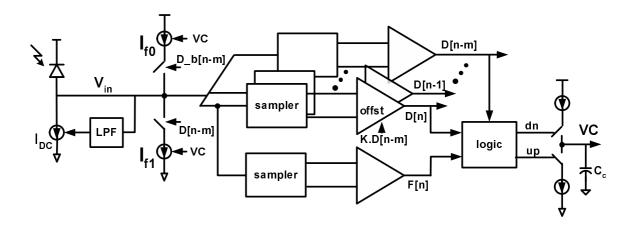

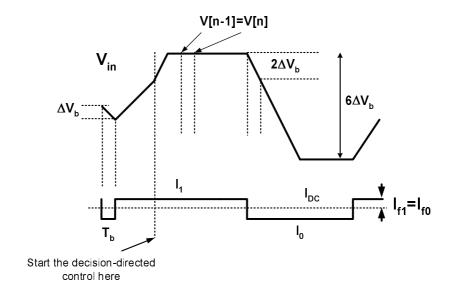

| 4.1  | Block diagram of decision-directed common-mode control                                          | 80 |

| 4.2  | Input voltage waveform with the decision-directed current control $$ . $$                       | 80 |

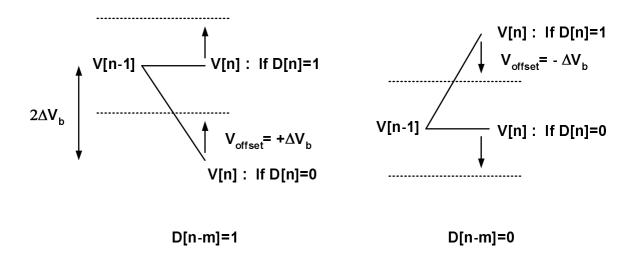

| 4.3  | Data resolution for DDCC by adding offset, four possible cases for                              |    |

|      | different values of $D[n]$ and $D[n-m]$ are shown                                               | 81 |

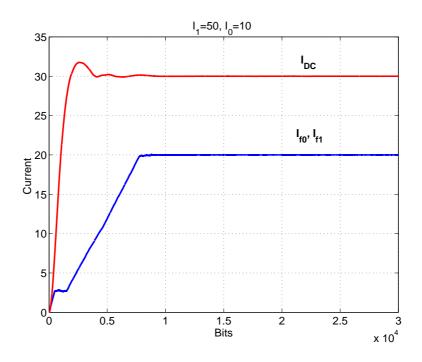

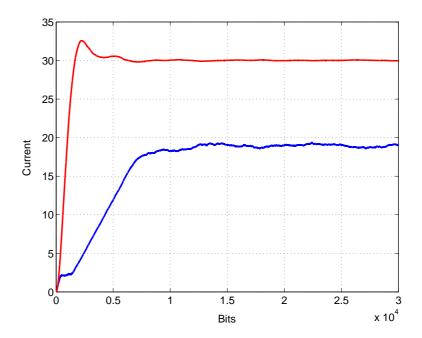

| 4.4  | Simulated loop dynamic for DDCC                                                                 | 82 |

| 4.5  | Simulated loop dynamic for DDCC with comparator noise and offset,                               |    |

|      | $\sigma_n = 1$ , offset=3                                                                       | 83 |

| 5.1  | 2x-oversampled phase deetction for the integrating front-end                                    | 89 |

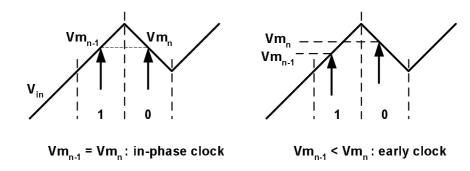

| 5.2  | Integrating input waveform and baud rate phase detection                                        | 91 |

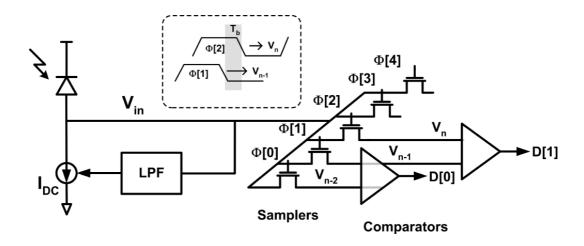

| 5.3  | Samplers and comparators for baud rate CDR                                                      | 91 |

| 5.4  | Bangbang CDR loop architecture used for the performance analysis .                              | 93 |

| 5.5  | Percentage of phase correction commands vs. phase misalignment for                              |    |

|      | the 2x-oversampled and baud rate techniques                                                     | 94 |

| 5.6  | Percentage of phase correction commands after a majority filtering over                         |    |

|      | every 5 bits                                                                                    | 95 |

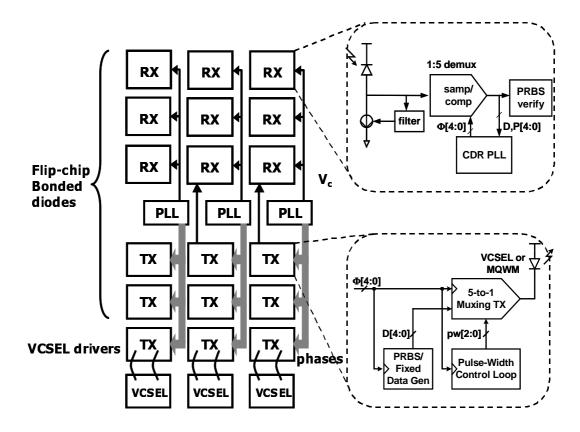

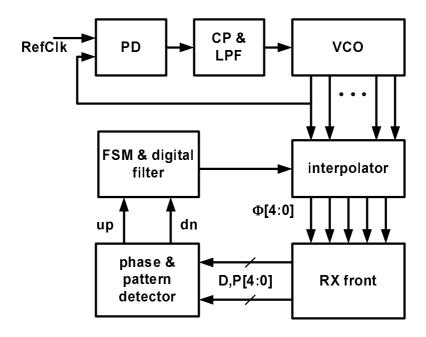

| 5.7  | Optical transceiver chip block diagram                                                          | 96 |

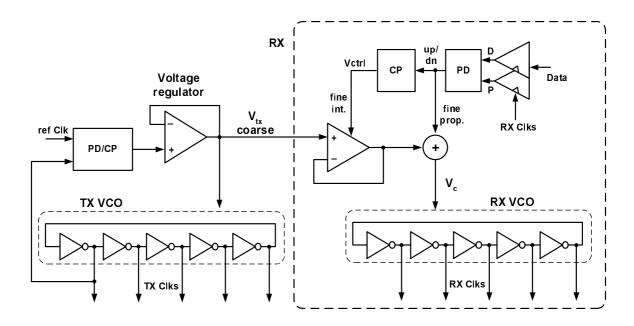

| 5.8  | Multiphase clock generation for the transmitter and clocked integrating                         |    |

|      | front and                                                                                       | 07 |

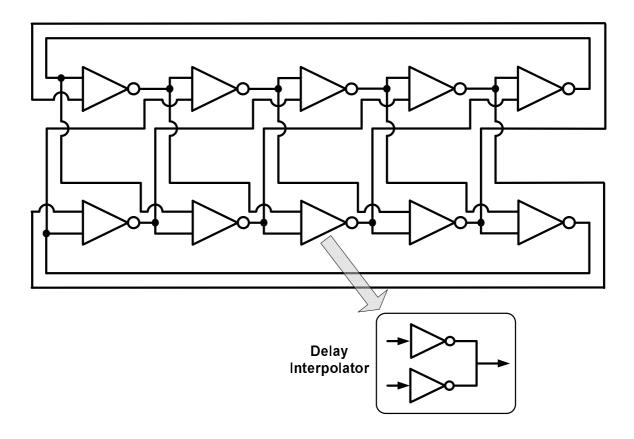

| 5.9  | Coupled ring-oscillator [1]                                                    | 96  |

|------|--------------------------------------------------------------------------------|-----|

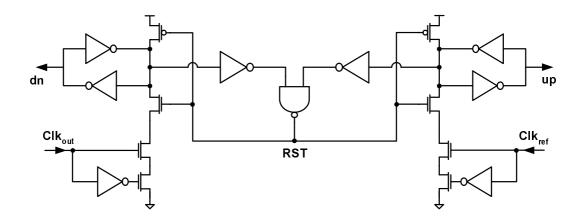

| 5.10 | Phase-frequency detector for the global PLL [2] $\dots$                        | 96  |

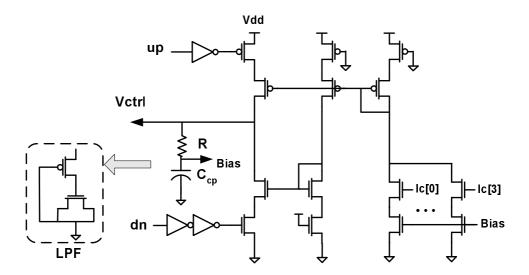

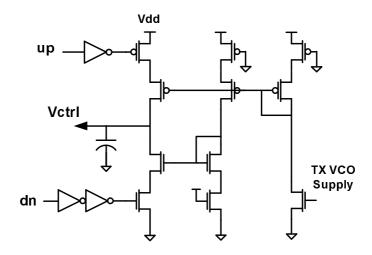

| 5.11 | Charge pump and loop filter                                                    | 100 |

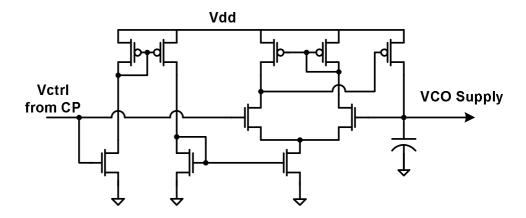

| 5.12 | Linear voltage regulator for low noise VCO voltage control $\ \ldots \ \ldots$ | 101 |

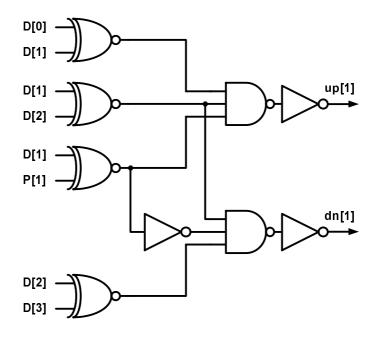

| 5.13 | Phase and pattern detector for baud rate CDR                                   | 102 |

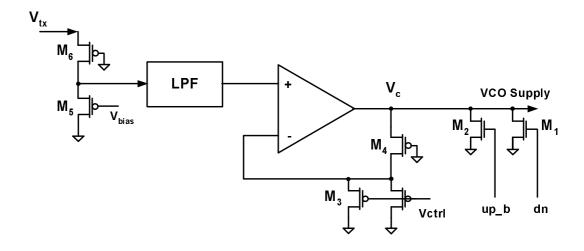

| 5.14 | Receiver VCO fine control, integral and proportional gains $\ \ldots \ \ldots$ | 103 |

| 5.15 | Receiver PLL charge-pump                                                       | 103 |

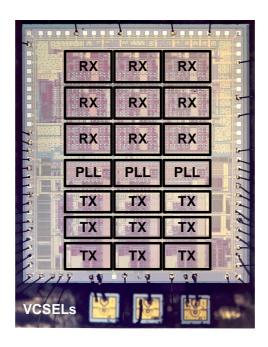

| 5.16 | Transceiver test-chip for parallel optical interconnection                     | 105 |

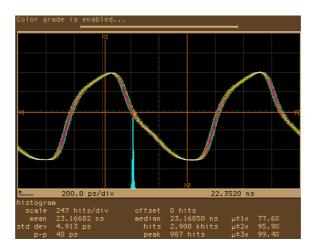

| 5.17 | Receiver recovered clock signal                                                | 106 |

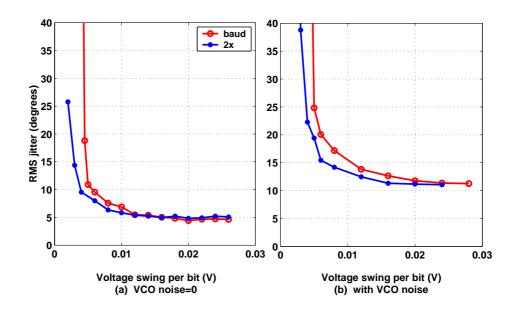

| 5.18 | Simulated jitter and measured jitter vs. input volatge                         | 107 |

| 5.19 | Jitter vs. input voltage swing with low loop gain and offset                   | 108 |

| 5.20 | Dual Loop Clock and Data Recovery Loop                                         | 109 |

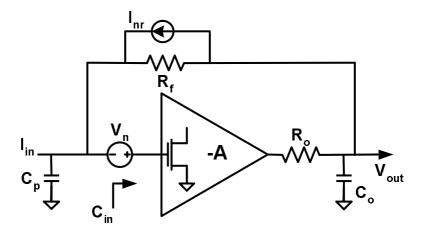

| A 1  | Shunt-shunt resistive feedback TIA model                                       | 116 |

### Chapter 1

### Introduction

In most applications today, integrated circuit (IC) chips need to communicate with many other ICs or modules in the system [3] [4]. The increasing speed of on-chip data processing and computation creates a growing demand for high-bandwidth input and output (IO) on these chips [5]. The required bandwidth is achieved by both increasing the signalling rate of each IO pin and increasing the number of IO pins on the chip.

Until recently, technology scaling facilitated faster transceiver circuits and on-chip clocking, allowing IO rates to scale with the technology [6] [7]. Unfortunately, the nature of the IO design problem has changed. Today internal circuits can run at 10's of Gb/s, but the performance of the link is limited by the characteristics of the channel - the electrical path from one die to the other. In order to achieve desired data rates over existing channels, many multi-Gb/s links use complex signal processing to get around the channel limitations [8].

Instead of continuing to increase the links complexity, a different approach for scaling performance of IOs is to change the signaling method and the channel media. The electrical loss in the copper wires has long motivated the use of optical fiber communication for data transmission over long distances. Reduced number of amplifiers in the signal path, higher bandwidth, improved signal-to-noise-ratio (SNR) and effectively lower cost have made optical fiber communication the favored choice for links longer than 10m.

The possibility of using optics for interconnection at short distances recently has

been a subject of considerable research and analysis [9] [10]. By providing a high-capacity channel, optical signaling can potentially close the gap between the inter-connect speed and on-chip data processing speed. This dissertation investigates the challenges of designing electronics for short-haul optical links and proposes a number of solutions to enable optical IOs. We focus on techniques to design simple, small and low power receivers suitable for dense parallel optical interconnects. In order to achieve low power and area a novel receiver front-end using a double sampling/integrating technique is proposed and the supporting circuits are presented. This design facilitates a number of interesting solutions such as parallelism and demultiplexing, an efficient baud-rate clock and data recovery (CDR) and a decision directed common-mode control technique to enhance the dynamic range of the receiver.

Although optical signaling involves electrical-to-optical (EO) conversion and vice versa (OE), its large channel bandwidth can simplify the design of the transceiver electronics. The frequency dependent loss and dispersion in optical signaling over short distances are negligible and the channel itself can support very high data rates [11]. The maximum data rate of an optical link is in fact limited by the performance of the optical devices and the speed of on-chip electronics. Although the data rate per channel might not be significantly higher than electrical signaling, the overall design might have lower power allowing more IOs built on die. In many systems, the maximum power consumption and area are among the limiting factors for the number of IOs possible on-chip. Moreover for parallel optical signaling at short distances, one can either use fiber-bundles or free space to send collimated beams in parallel from one chip to the other. In both situations the cross-talk among the beams is negligible, avoiding another problem with large numbers of electrical IOs. Note that optical signaling does not have impedance matching and pin allocation restrictions either. A three dimensional configuration for parallel optical interconnection in free space is shown in Figure 1.1. The integration of dense two dimensional (2D) arrays of optical devices with standard complementary-metal-oxide-semiconductor (CMOS) ICs has been demonstrated, and allows a huge chip-to-chip interconnection bandwidth [12] [13] [14] [15] [16]. Figure 1.2 shows an example of hybrid integration of

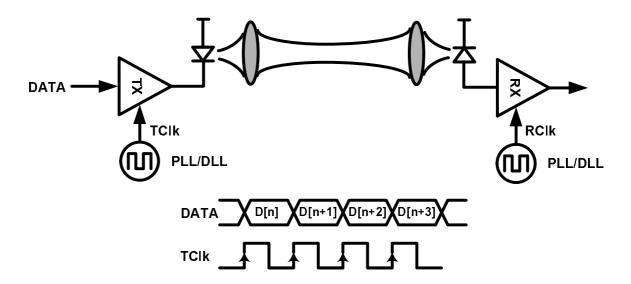

Figure 1.1: Parallel optical chip-to-chip interconnection over free space optical devices to the surface of silicon, developed in Stanford University.

### 1.1 Organization

Link designers have solved many of the problems associated with high-speed electrical signaling. Understanding these issues and solutions for electrical links is critical for us for a number of reasons. First, all optical links have an electrical link embedded in them. They surround that electrical link with an electrical-to-optical (EO) and optical-to-electrical (OE) conversion. Second, since optical links are proposed as an alternative to the electrical links, recognizing the limitations and performance of electrical links is essential to evaluate the utility of optical links. Chapter 2 of this thesis is dedicated to reviewing electrical links. That chapter provides a background in high speed data transmission systems and motivates the application of optical signaling.

Optical links can have significant advantages over electrical links only if large number of parallel optical beams can interface with each IC. Scaling of parallel optical interconnects to hundreds and thousands of links on a single chip requires receiver and transmitter circuitry that are very small and have very low power consumption at

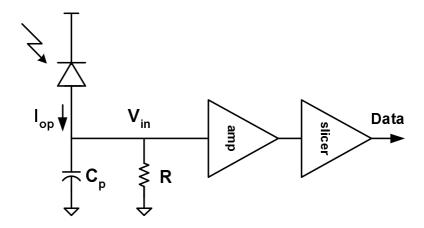

Figure 1.2: Array of GaAs optical devices, flip-chip bonded to the silicon CMOS chip

high data-rates. This is a different requirement than that for long-haul communication links, where sensitivity and bandwidth are the most critical issues and complex designs are allowed. For parallel optical interconnects, the design of a low power receiver frontend is particularly challenging. A photodetector, usually a reverse-biased photodiode, converts the optical power to a small proportional electrical current. The front-end receiver tasks mainly include converting this current to voltage, amplification and data detection. The receiver must add minimum noise and distortion to the signal at high data-rates and operate over a wide range of input optical power.

Chapter 3 of this thesis focuses on the receiver design for short-haul optical interconnects. It starts by reviewing optical to electrical conversion and optical devices used for this purpose. Understanding the properties of these devices is essential in designing an optimized and high performance front-end. Chapter 3 continues by exploring the prior art in optical receiver design. Optical signaling has been used for many years for long-haul communication and considerable effort has been dedicated to the design of the front-end for those applications. Investigation of the existing solutions can help us to understand the challenges of optical front-end design. Finally Chapter 3 presents a new low-power optical receiver front-end that uses a double sampling/integrating technique for data resolution. Unlike most prior designs, this receiver avoids having any linear/analog gain in the active-path and does not rely on

a high gain-bandwidth product voltage amplifier.

The eventual goal in optical interconnect design is to have thousands of transceivers in a single chip. The continuing scaling of feature sizes in the CMOS technology, allows smaller and faster circuitries. Chapter 4 investigates how the performance of the proposed front-end scales with the advanced technologies. In particular we look into what factors will eventually limit performance scaling. While the data-rate, power consumption and area of electronic circuits improve with the scaling, the reduced power supply voltage and increased leakage current can introduce new problems to any design. The integrating nature of our receiver brings concern regarding the dynamic range of input optical power, as well as the acceptable data formats for the correct operation of the front-end. These concerns are even more serious with the scaled power supplies of the advanced CMOS technologies. In this chapter we propose a decision directed control scheme that significantly reduces these effects.

In any synchronous data transmission scheme, clocking and synchronization are among the most challenging problems. The proposed double sampling/integrating receiver is a clocked front-end and needs a synchronous clock signal to perform the sampling and comparison. Multi-phase clock generation and synchronization issues are discussed in Chapter 5. The timing of the bits is precisely controlled by a phase-locked loop at the transmitter. The optimal sampling time at the receiver is maintained by clock generation and timing recovery circuits. The clocking circuits, both at the transmitter side and receiver side generate multi-phase clocks for the de-multiplexing. The integrating front-end allows an efficient band rate clock recovery technique that reduces the power consumption and complexity compared to the standard clock recovery techniques.

The techniques proposed in this thesis were implemented in two test-chips fabricated in  $0.25\mu m$  CMOS. The first chip demonstrated the possibility of very low-power receiver design that achieves a high bandwidth and sensitivity [17]. The performance of this chip is discussed in Chapter 3. The low-power consumption of the front-end makes it an excellent candidate for building dense receiver arrays on-chip. We implemented a two dimensional array of optical transmitters and receivers in the second

test-chip. The receiver design was improved to achieve higher data-rates and implemented the clock recovery techniques described in Chapter 5 [18].

Finally, in Chapter 6 we summarize the conclusions of this work.

### Chapter 2

### Background

Point-to-point parallel electrical links have been widely used in short-distance applications such as multiprocessor interconnections [19] [3], networking and communication switches [4] [20], and consumer products [21]. As we mentioned in Chapter 1, in this thesis we explore a number of techniques that facilitate using optical signaling as an alternative in applications that demand high bandwidths. While the traveling signal in optical links are light beams, they still interconnect electrical IC chips. The complete link always starts with an electrical signal at the transmitter and results in an electrical signal at the receiver side. Therefore many internal blocks and principles of electrical links and optical links are identical. Before focusing on optical link design as a replacement for electrical signaling, it is essential to understand the latter. This chapter provides a background in electrical link design. We investigate the basic structure of electrical links, transmitter and receiver design, as well as clock recovery techniques. Since channel capacity and noise are the major limitations for increasing the data rate in most systems, we continue this chapter with reviewing the channel properties and techniques developed to solve the problems associated with them.

#### 2.1 Electrical Link Basics

Electrical links can provide high communication bandwidths between chips, and consist of three major components as shown in Figure 2.1. The transmitter converts the

Figure 2.1: Components of a basic electrical link

digital data into an electrical signal that travels through the channel. The electrical channel is the complete electrical path from one die to the other. This channel can consist of traces on a printed circuit board (PCB), coaxial cables, shielded or unshielded twisted pairs of wires, traces within chip packages, and the connectors that join these various parts together. A receiver then converts the incoming electrical signal back into digital data.

The conversion of a discrete-time digital signal into a continuous-time analog signal is called modulation. Here we limit ourselves to the simple non-return-to-zero (NRZ) modulation format, where the data is sent directly on the channel, and the signal levels are represented by different electrical voltages. This modulation technique is called pulse amplitude modulation (PAM). 2-PAM is the simplest signaling scheme where the transmit symbol is a binary signal. The electrical signaling is often low swing to reduce the power consumption.

In most electrical links a synchronous or plesiochronous transmission scheme is adopted, where a clock signal at the transmitter is used to define uniform time periods for sending the data signals successively one after another. At the receiver side a similar clock signal, synchronized with the data is used to sample the incoming signal. While the synchronous data transmission scheme can be high-bandwidth, it requires

Figure 2.2: Plesiochronous serial link

very precise control on the timing of the signals at the transmitter and receiver. In most systems, phase-locked loops (PLLs) or delay-locked loops (DLLs) are employed to achieve a high level of timing accuracy [22] [23] [24]. The receiver sampling clock should be optimally positioned to minimize the bit error rate (BER) and achieve very high data rate. The optimum sampling point is usually close to the middle of the bit-period. The adjustment of the receiver clock frequency and phase is called clock and timing recovery.

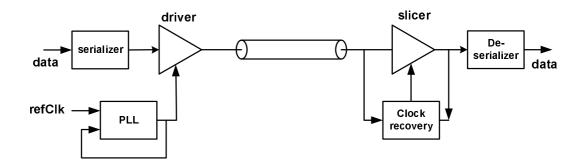

Point-to-point data transmission techniques historically have been divided in two groups: serial and parallel links. Figure 2.2 illustrates a typical serial link, where the transmit data is serialized and sent through a single, high-data-rate link to the receiver, where the data is de-serialized to parallel slower sets of bits. In this scheme the receiver needs to recover the clock and timing from the transitions embedded in the incoming data stream [25] [26]. This clocking scheme is called plesiochronous. Many serial links are designed to support very high data-rates over relatively long distances [20] [27] [28]. In order to meet these objectives and perform the accurate clock recovery, serial links may need relatively complex designs [8] [29].

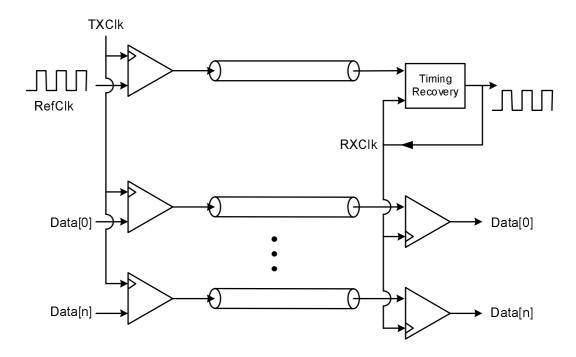

Figure 2.3 on the other hand illustrates a typical parallel link. This is a common architecture to enable high bandwidth communication between two chips that integrates several parallel sets of data links whose delays through the channels match [30]. A separate reference clock, synchronized with the data, is then sent from the transmitter to the receiver. This clocking scheme is called source-synchronous. The transmission of reference clock (RefClk) simplifies the design of the receiver clock recovery.

Figure 2.3: Parallel source-synchronous link

A simple delay-locked loop can be used to align the edge of the RXClk to the mid point of the RefClk. Simple IO design is crucial when many numbers of IOs per chip is required.

As system requirements change over time, the design goals, features, and applications of modern serial links and parallel links are converging. In parallel links, due to the process mismatches a precise delay matching between different pins is not practical and can limit the data rate. Many parallel links now employ traditional serial link techniques with per pin clock and data recovery (CDR) [31] [32], in the quest for higher bandwidth. On the other hand reducing power consumption and design complexity are now among the goals of serial link designers.

#### 2.1.1 Channel Termination

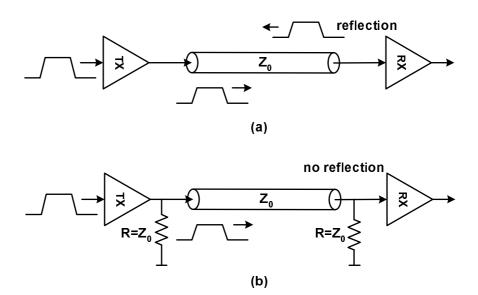

The electrical channel used for high speed signaling is normally impedance-controlled and is modeled as a transmission line with the intrinsic impedance  $Z_0$ . Termination

Figure 2.4: Electrical signaling (a) with no termination, (b) properly terminated

of the channel to an impedance matched with the channel is critical in design of high speed links. Termination effectively suppresses reflection, which can cause interference and limit the signalling rate. Figure 2.4 illustrates the cases when the channel is properly terminated and when it is not. When the channel is not terminated, the signal that arrives at the receiving end can bounce back to the opposite direction. With no termination at the transmitter side the signal keeps bouncing back and forth until it dissipates in the channel. In this situation, for the correct data decision, the transmitter may wait until the reflections are very small to send the next bit. However, this will reduce the data rate significantly.

With proper channel termination at both transmitter side and receiver side, the signal is fully absorbed and therefore consecutive bits can be sent through the channel with no delay imposed by the reflections. In fact the next bit can be sent even before the previous bit reaches the receiver. The termination at the transmitter is necessary since deviations from ideal matching at the receiver can cause some reflections that should be absorbed at the transmitter side.

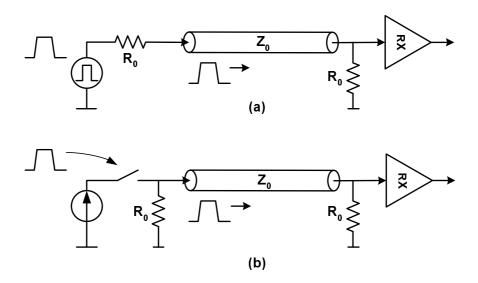

Figure 2.5: Data transmission schemes (a) low-impedance, voltage mode drive, (b) high-impedance, current mode drive

#### 2.1.2 Transmitter Design

A signal transmitter converts digital data into electrical signals that propagate through the impedance-controlled channel to a receiver at the opposite end. For high-speed data communication links, this must be done with accurate signal levels and timing. The receiver chooses a threshold voltage to resolve the data sent from the transmitter. A common voltage reference is then required to correctly resolve the data value. Usually ground is chosen to be the common voltage reference for communication.

The signal transmission over the line can be done with either a low-impedance driver or a high-impedance driver, shown in Figure 2.5. High-impedance signaling is the most common type of signaling in today high-speed links [29].

In high-impedance signaling, the output signals are generated via a current source that turns on and off depending on the polarity of the transmitted data. The voltage swing at the output depends on the termination and the size of the current source. In order to control the voltage swing and proper termination - to avoid reflections - the current source should be kept in the saturation region and the termination resistor should be carefully designed and controlled [33] [34] [35]. Figure 2.6 shows a possible

Figure 2.6: Current mode driver

implementation of the transmitter with PMOS transistor current driver and NMOS transistors in linear region as termination resistor.

For high-speed applications, it is crucial to maintain a robust voltage swing and slew rate at the output of transmitter. The properties of transistor and passive elements that set these values are strongly dependent on temperature and process. Therefore, in many designs the switching current source is determined via a feedback loop to monitor and control the output voltage swing.

### 2.1.3 Receiver Design

A conventional receiver design is a slicer that samples the incoming data in the middle of the bit-period and compares that sample with a threshold voltage chosen to be between the signal levels of the adjacent symbols; see Figure 2.7. For high-speed applications, designers try to avoid linear amplification of the input signal - which requires a high-bandwidth amplifier - by launching enough signal power into the channel. Therefore the slicer samples the raw input signal with no pre-amplification.

The general requirements of a receiver in high-speed applications are high bandwidth, high gain, low noise and low offset. The noise and offset of the comparator plus the coupled noise can increase the bit error rate significantly.

Many receiver designs have been implemented and published in the literature [36] [37] [38]. A different approach that offers good noise filtering is the integrating receiver

Figure 2.7: Data resolution at the receiver using a slicer

proposed by Sidiropoulos et al. and described in [39]. The integration of the received signal over the bit-period rejects high frequency noise. However, it requires accurate phase alignment between the clock and data.

#### 2.1.4 Time Division Multiplexing

In all transmitter and receiver designs mentioned in the previous sections, the data rate is dictated by the maximum on-chip clock frequency. The clock is used to generate the bit stream at the transmitter and to sample the input signal at the receiver side. In any CMOS technology the maximum clock frequency that can be buffered and transferred robustly across the chip is limited by the switching speed of transistors. Technology speed is sometimes evaluated by the delay of an inverter buffer with a fanout-of-four (FO4). With no loss in amplitude, a chain of CMOS inverters can propagate pulses that are as short as 3-4 FO4 inverter delays. Therefore the minimum clock period is limited to 6-8 FO4 inverter delays. The FO4 inverter delay in picoseconds will decrease as the device feature size shrinks.

The data transmission rate can significantly increase if we use parallelism by effectively implementing a time-division multiplexing. This is possible by using multiple branches of transmitters and receivers as well as multiple phases of the clock, which are equally shifted over time [25] [26] [20]; see Figure 2.8. Assuming that the number of branches is M, in this scheme each branch is driven by a clock, which is M times

Figure 2.8: Time division multiplexing and parallelism

slower than the data rate. Multiple transmitters connected in parallel convert low-frequency parallel data streams into a single high-frequency stream on the channel. Multiple phases of the lower-frequency clock control the on- and off-timing of each transmitter. Similarly, the parallel receivers convert the high-frequency data stream back to the low-frequency parallel data streams. Note that multiphase clocks evenly divide a clock period and set the receiving window of each receiver. The bandwidth requirement of the receiver front-end is relieved by the de-multiplexing scheme since there is no amplifier running at the bit rate. Instead each slicer operates at the clock frequency. With this parallelism approach, bit-periods as low as 1 FO4 inverter delays are possible [25].

### 2.2 Clock Generation and Recovery Loops

Most high speed links use clock signals to generate a defined bit-time at the transmitter and correctly recover the data at the receiver side. The timing uncertainties of clocks or data signals are referred to as jitter, the AC variation of the period of the waveform over time, and skew, the DC component of the timing misalignment

between the waveform and a reference clock. Phase-locked loops are commonly used at the transmitter side to generate and synthesize a very low-jitter clock from a periodic reference. PLLs can be used for frequency multiplication when the on-chip clock frequency needs to be higher than the reference clock coming from the PCB boards. PLLs are also used at the receiver side to generate a synchronous clock for data resolution. This section reviews the basics of PLL and clocking and timing recovery in high-speed links.

#### 2.2.1 Phase-Locked Loop

A PLL controls the phase of an output clock so its phase is aligned to an incoming signal. In other words, the output clock tracks the phase variations of the input signal. The phase tracking behavior in a PLL is implemented through a negative feedback loop. A PLL can be built around a voltage-controlled oscillator (VCO) or a voltage-controlled delay line (VCDL). Phase-locked loops with VCOs are simply called PLLs while the ones with VCDL are commonly referred to as delay-locked loops (DLLs). Figure 2.9 shows typical block diagrams of a PLL and a DLL.

A VCO-based PLL consists of a phase detector (PD), a loop filter, a VCO and possibly a frequency divider. The phase difference between the output clock and the input signal generates a proportional error signal at the output of the phase detector. The loop filter, which is usually a single-pole low-pass filter (LPF), smooths out this signal and generates a control voltage, called *Vctrl* in Figure 2.9.

Since in a PLL we measure the phase but control the frequency, a VCO acts as an phase integrator. The resulting PLL transfer function has at least two poles and needs a stabilizing zero in the LPF. The positioning of the zero is critical and careful design is required to ensure the stability when process variations are considered. DLLs on the other hand use a VCDL, which has a linear phase transfer function, therefore DLLs are inherently first order loops and stability concerns are relaxed in this case. However, a PLL can filter out the jitter of the incoming signal and generate a clean clock from a noisy input, while any jitter in the input of a DLL will directly appear at the output.

Figure 2.9: Phase-locked loops (a) a VCO-based PLL, (b) a VCDL-based DLL

The general purpose of a PLL is to generate very low-jitter clock signals that track the phase of the input signal. The jitter characteristics depend on the noise of the internal blocks such as delay elements and oscillators, as well as loop bandwidth and phase margin. The most common approaches to design VCOs are ring oscillators and LC oscillators. The noise performance of these VCOs are investigated by Hajimiri: [40]. Although noise performance of the LC oscillator is generally superior to the ring oscillator, rings have been used widely in high speed IOs due to their simplicity, smaller area and easily accessed multi-phase outputs. A differential delay element proposed by Maneatis in [41] uses a replica biasing technique to ensure linearity and high power supply noise rejection. Simple inverters with regulated power supply are also used as adjustable delay elements for building DLLs and PLLs [42]. A regulator essentially isolates the VCO from the noisy power supply in order to reduce the VCO clock jitter.

#### 2.2.2 Voltage and Timing Margins

In most high-speed signaling systems the received signal contains a significant amount of amplitude and timing noise. The noise is added both at the transmitter and during the travel time along the channel. For the receiver that samples, both timing and amplitude uncertainty in the input signal translate into a voltage noise in the sampled value. The quality of the received signal is important since the receiver itself is not ideal. An eye diagram is usually used to examine the quality of the received signal, see Figure 2.10. The jitter and phase offset in the receiver clock as well as the comparator noise and offset calls for a wide eye-opening in the received signal. Voltage and timing margins at the receiver are defined in Figure 2.10.

With conventional electrical signaling, the voltage and timing margins are decreasing rapidly as the data rate increases. For such systems generation of very accurate synchronous timing at the receiver is crucial to sample the signal where noise is minimum.

Figure 2.10: Receiver voltage and timing margins

#### 2.2.3 Clock Recovery

In typical high-speed links, due to the process mismatches, time variations and undefined delays in the signal path, the received data can have an undefined phase and frequency. As we mentioned before, either a separate clock signal is sent along the data signal for timing information or the clock should be recovered from the incoming data signal.

The transmitter's limited bandwidth, frequency dependent losses in the channel and reflections all create inter-symbol interference (ISI). This ISI combines with the transmitter clock jitter and cross-talk to add amplitude noise and timing jitter to the received waveform. A clock recovery block should extract the clock component of the incoming signal and filter out the timing jitter. Finding the best sampling time with low variance and phase shift is particularly critical for bandlimited channels to minimize the BER. In most systems direct estimation of a sampling time that minimizes the probability of error in the data resolution is not a practical task. Instead sub-optimal practical solutions are adopted to define the best sampling point. The most common approach is to assume that the best sampling time is where the overall ISI is minimum. At this point the vertical eye-opening in the eye-diagram is maximum as is shown in Figure 2.10.

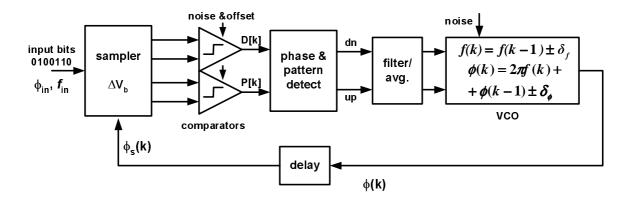

Figure 2.11: Timing recovery from the received data

Figure 2.11 illustrates a typical timing recovery loop for a serial link. In case of phase mismatch between the clock and received data, the phase detector generates an error signal to adjust the VCO's phase and frequency. The output of the phase detector can be an analog signal for an analog loop or a digital correction commands for a bangbang-controlled loop. In a bangbang-controlled PLL, the phase and frequency of the VCO are corrected by constant steps in two different directions depending on the decisions of the phase detector. The correction commands are called "up" and "dn" commands in this thesis. As we will see in the following sections, a decision-based phase detector is used in many CDR techniques. In these CDRs, the data decisions are usually used to determine the type of transition that occurred and then use that information to find the correction needed.

A number of different techniques for phase detection and definition of best sampling time have been proposed [25] [26] [43]. The over-sampling technique described in [25] takes 3 or more samples per each bit and performs the data resolution for all of them. Then, by looking at the sequence of resolved values, it decides which sample is the most reliable one, which is simply the one farthest from the transitions. This technique is very robust but requires a considerable hardware, power and area overhead for the oversampling. It also needs phase spacings that are at least three times shorter than a bit-period. For systems that run at data rates close to the technology limitations, such sampling schemes are not practical.

Figure 2.12: 2x over-sampled CDR with two clock phases for data and phase resolution

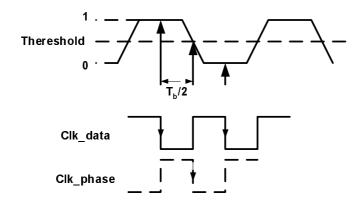

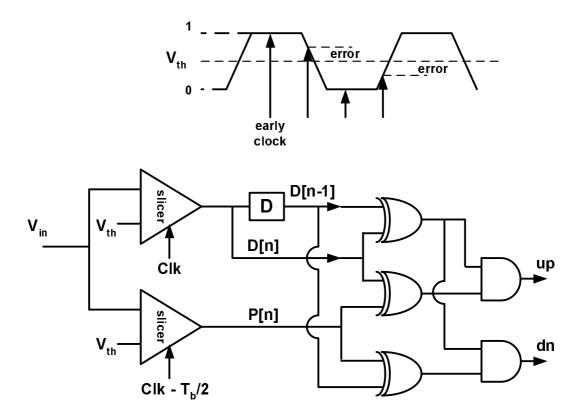

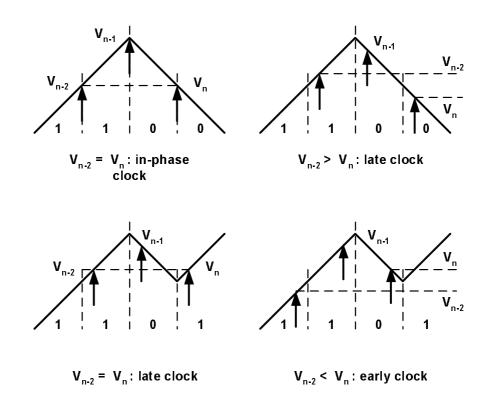

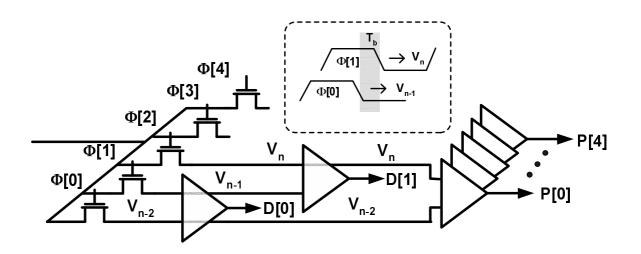

A common CDR technique in electrical signaling is the 2x-oversampling scheme [26]. This technique is based on the assumption that if the best sampling time with minimum ISI is at time  $\tau$ , at any "one-zero" (10) or "zero-one" (01) transition, an edge sample at time  $\tau - T_b/2$  is expected to be equal to the threshold value.  $T_b$  here is the bit-period shown in Figure 2.12. Any phase error will cause deviation of edge-sample from the threshold value. The difference can be used as an error signal in a phase correction feedback loop. This error signal can indicate both the magnitude and direction of phase error. The effect of an early clock is shown in Figure 2.13. Depending on the direction of transition, 10 or 01, the error signal can be positive or negative for an early clock. A simple block diagram of a 2x-oversampling bangbang-controlled CDR is shown in Figure 2.13. The P[n] signals are generated by comparing the edge sample with the threshold value. P[n] and the resolved data values before and after the edge sample, D[n-1] and D[n] provide complete information for phase detection. As shown in this figure, a replica of front-end slicer, clocked with an extra clock phase that is shifted by half a bit-period, can generate the phase information, P signals.

The 2x-oversampling clock recovery technique is used widely in high-speed PAM links. This technique is called zero-forced-detection (ZFD) in some literature. Clearly for binary 2-PAM the phase information is valid at all transitions, which occur 50% of times. For higher levels of PAM, specific types of transitions that ideally cross

Figure 2.13: 2x over-sampled phase detection, loop error signal and implementation

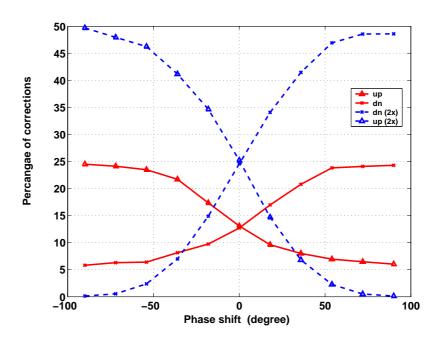

the threshold at time  $\tau - T_b/2$  are the ones that generate accurate phase information [26] [44]. One of the concerns with this clock recovery technique is the uncertainties of edge samples in the presence of ISI, as well as the inaccuracy of comparison with  $V_{th}$ . In other words the error rate in P signals could be much higher than the error rate in resolved data D, which means heavy filtering of phase information is needed for good performance. Moreover, 2x-oversampled CDR needs an extra clock phase that is accurately positioned in the middle of main phases for data samples. Generation and distribution of extra phases are particularly challenging and power hungry when a time division multiplexing technique is used.

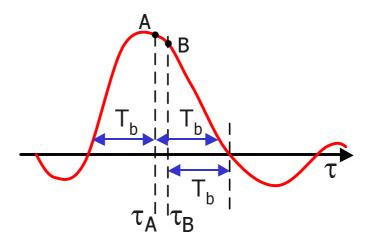

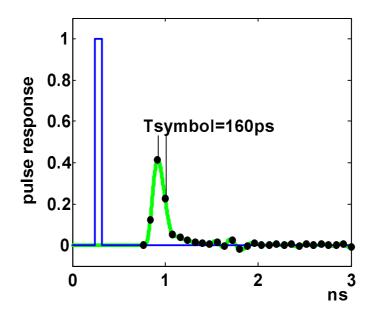

Baud rate clock recovery refers to techniques that use only main data samples for both data recovery and adjusting the clock frequency and phase. Thus the baud rate CDR does not need the extra clock phases and edge samples. This implies that this technique potentially reduces the complexity and power consumption compared to the over-sampled techniques. There are a number of different techniques proposed for baud rate clock recovery in digital data communication systems. The technique proposed by Mueller and Muller in [43] provides phase information by identifying certain properties of the pulse response of the ISI channel. In this technique we can find a relationship between the baud rate samples of the channel pulse response that is true only if the timing of the samples are aligned with the pulse. If this relationship is defined as  $f(\tau)=0$ , then  $\tau$  is the best sampling time and a phase misalignment generates a positive or negative  $f(\tau)$ . Figure 2.14 shows a typical channel pulse response,  $h(\tau)$  and two different ways of identifying the best sampling time. In the first technique point A at time  $\tau = \tau_A$  is defined as a solution to  $f(\tau) = h(\tau + T_b) - h(\tau - T_b) = 0$ , where  $T_b$  is the bit-period. Point B on the other hand is the solution to  $f(\tau) = h(\tau + T_b) = 0$ .

During the data transmission the baud rate samples of the incoming waveform are not equal to the samples of this pulse response. However, each baud rate sample of the incoming signal is equal to the sum of the pulse response sample at time  $\tau$  and other samples at  $\tau + kT_b$ , k=1,2,... which act as ISI. All these samples are modulated by their corresponding bit values. Therefore, theoretically, if we know the bit values, it is possible to reconstruct a similar relationship between the baud rate samples of the

Figure 2.14: Channel pulse response and criteria for baud rate recovery

incoming signal that has timing information for clock recovery. The expected value of this relationship can be used as an error signal in a CDR loop, and it is chosen to minimize the variance. While baud rate CDR is a very attractive solution, there are a number of challenges associated with this approach. First, the defined relationship between the samples and resolved data values requires linear and accurate arithmetic processing of the analog samples. This processing is usually hard and needs to be fast. Moreover in order to reduce the phase variance of the phase correction loop, it might be necessary to choose only certain data patterns or for different patterns calculate different functions. This process adds to the complexity of the baud rate CDR techniques for regular electrical signaling.

# 2.3 Channel

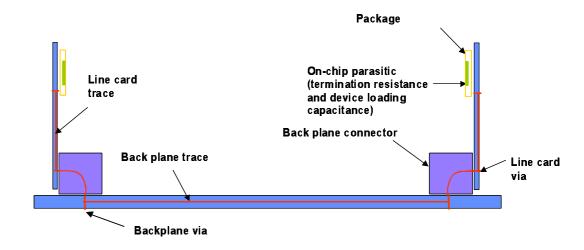

At the data rates required in many systems today, the filtering imposed by the electrical channel is among the most challenging problems. The performance of the channel strongly depends on the application. As an example a typical backplane link and its components are shown in Figure 2.15 [45]. Loss per unit length of PCB-traces increases with the frequency due to the dielectric loss and skin effect. Different trace

Figure 2.15: Signal path and channel components in a typical backplane

lengths and backplane material properties, as well as types of connectors, vias and routing layers, cause significant variation in channel transfer function both among different boards and among channels in the same backplane.

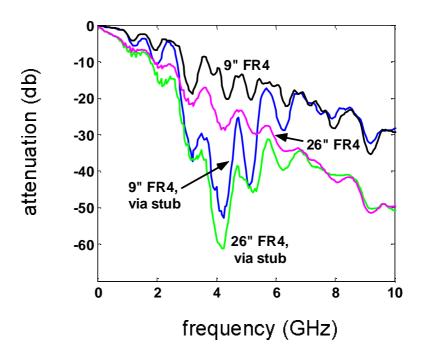

The typical transfer functions for channels within a single backplane are illustrated in Figure 2.16 [8]. Since the loss in the channel increases with the frequency, the channel acts as a low-pass filter. The filtering effects leads to spread of narrow pulses originally confined to a bit-period as shown in Figure 2.17. This effect is called dispersion. The tail of the pulse acts as an additive noise for the next bits and is referred to as inter-symbol interference or ISI. Dispersion is enhanced by the filters formed by unintended transmission line impedance discontinuities caused by via stubs and connections. In the time domain these discontinuities cause reflections, which also lead to ISI. Crosstalk or co-channel interference is the other problem that occurs in dense interconnects. Both far and near end cross-talk (FEXT and NEXT), are important in such systems.

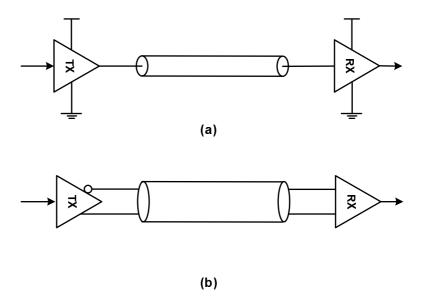

One way to reduce the cross-talk problems is to use differential signaling instead of single-ended. A differential signalling scheme transmits both the signal and its complement on a differential channel as it is shown in Figure 2.18. A drawback of differential signaling is the need for an additional pin per IO and potentially increased power consumption. However, reduction in the noise possible through differential

Figure 2.16: Typical frequency transfer function of a backplane channel

Figure 2.17: Dispersion in a band-limited channel

Figure 2.18: Signaling methods (a) single-ended signaling, (b) differential signaling

signalling may enable lower signaling levels to reduce the overall power consumed, relative to single-ended signalling.

Even with differential signaling the dispersion problems will not go away. Also by simply increasing the signal intensity the SNR does not improve significantly since the ISIs depend on the signal itself. In fact these residual errors are not random but deterministic in nature. This means that if the channel pulse response and input sequences are known, it is possible to at least partly correct the channel dispersion at the receiver and transmitter. These techniques are referred to as equalization, and explored in the next section.

# 2.3.1 Equalization

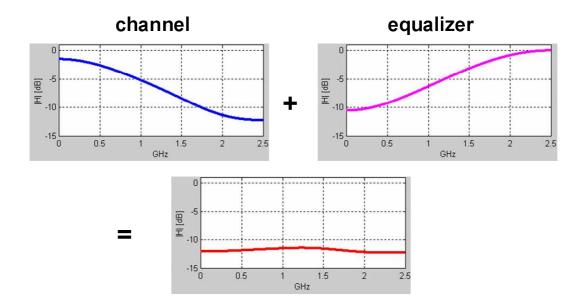

Equalization techniques have been used increasingly in high speed links in recent years [46] [47] [38] [26]. An equalizer subtracts the ISI in the time domain or equivalently flattens the frequency response of the channel. In order to flatten the frequency response we can boost the high frequencies relative to the low frequencies, or attenuate the low frequencies; see Figure 2.19. These techniques are known as linear

Figure 2.19: Linear equalization, flattens the frequency response

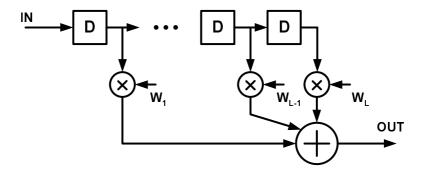

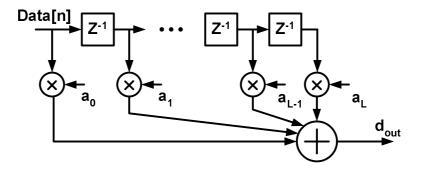

equalization. A linear equalizer at the receiver side can be built with an FIR filter shown in Figure 2.20. The FIR filter could be either digital or analog. This equalizer effectively amplifies the high frequencies attenuated by the channel. The main issue with such a solution is that the noise at high frequencies is also amplified. The coefficients  $W_i$ , can be set by using adaptive algorithms such as least-mean-square (LMS). In an analog FIR filter, the precision of the arithmetic operations as well as building the analog delay lines are among the challenges of building the FIR filter.

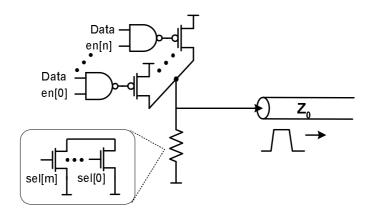

Alternatively the equalizer can be built at the transmitter side. The transmitter equalizer shown in Figure 2.21, attenuates the low frequency components of the incoming signal. In this design, due to the limited output power, the amplitude of the output signal should be adjusted accordingly. The FIR filter here is in fact a digital to analog converter (D/A) while the FIR at the receiver is a analog to digital converter (A/D). In general the design of an D/A is simpler and one can achieve better precision in design of transmitter equalizer compared to the receiver equalizer. Setting the equalization weight at the transmitter side is possible but is not as straightforward [48].

In all techniques discussed so far, a linear equalizer tries to invert the channel

Figure 2.20: Linear equalization at the receiver with FIR filtering

Figure 2.21: Linear equalization at the transmitter with FIR filtering

Figure 2.22: Decision feedback equalization

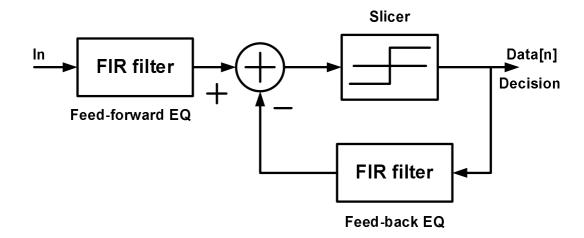

and compensate for attenuations at high frequencies. A different class of equalizers called decision-feedback-equalizers or DFE, focuses on directly removing the ISI from the input signal. Removing the ISI is possible if the characteristics of the channel as well as the data decisions are available. In communications, DFE has been used heavily instead of linear filtering, to circumvent the problem of noise amplification [49]. Recently similar techniques has been applied to serial links [50] [44].

A possible DFE implementation is shown in Figure 2.22. Here the slicer resolves the data value and the decision, and older bits are fed to an FIR filter that then drives a DAC whose output is subtracted from the input signal [51]. The feedback filter of the DFE only removes the ISI caused by previous bits, while a feedforward filter is necessary to remove the pre-curser ISI. The feedforward FIR is normally implemented at the transmitter side, where we have access to the bits not sent to the channel yet.

Unfortunately the above approach suffers from latency problems at the receiver side. For a 10Gb/s binary link, we have only 100ps to resolve the input, drive the DAC, and have the DAC outputs settle to the required precision. The latency problem has motivated an interesting approach called loop unrolling. While the decision is made for the last bit, the feedback is computed two times in parallel, assuming the incoming data is either "1" or "0". As soon as the data is resolved, one of the outputs is chosen by using a fast multiplexer. This technique was proposed by Parhi

and Kasturia [52] [53]. This approach doubles the number of comparators in a 2-PAM scheme if it is applied to one tap of the equalizer. This method can be applied to two or more taps of feedback, though the number of decision blocks increases exponentially.

DFE is capable of canceling the ISI caused by reflections from the discontinuities in the signal path. This type of ISI is usually created by the bits that are far enough from the current bit, and latency in DFE is not a problem anymore. However a very high number of taps adds to the complexity and parasitics at the input node, as well as to power consumption and area. In most systems only a limited number of taps are available.

# 2.4 Summary

Electrical signaling is the most natural approach for interconnecting electronic chips since no conversion of energy is required and achieving high levels of integration is possible. As a result of extensive design efforts as well as access to faster transistors, electrical signaling has experienced a significant performance improvement in the last two decades. In many electrical signaling applications, most of channel components, for instance the PCB boards, are kept unchanged to avoid extra cost. In these systems considerable effort is dedicated to the design of transceivers capable of high-speed signaling through the same channel to meet the requirements of today systems. However, the high-speed signaling is now running into the limitation of channel bandwidth and discontinuities in the signal path. Moreover the cross-talk between adjacent signals puts a hard limit on the density of high speed IOs in the system. As we discussed in this chapter, advanced timing recovery techniques as well as equalization techniques have allowed the maximum data rates to continue to scale. However these techniques heavily add to the complexity, power consumption and area of the transceivers.

The complexity of transceiver design can be reduced if the channel characteristics are improved. A fundamentally different approach is to use a carrier at much higher frequencies than the signal bandwidth. If the channel can support that carrier, there is a high chance to have a flat frequency response over the signal bandwidth, which avoids dispersion. An excellent example of such carrier is a coherent light traveling in a transparent medium, which has led to fiber optics communication systems. However, for chip-to-chip interconnections, switching to optics, which involves energy conversions, is beneficial only if one can build simpler transceivers that can result in higher number of IOs per chip. In the rest of this thesis we explore different techniques that can facilitate this goal.

# Chapter 3

# Receiver Design for Optical Interconnects

The power consumption and area of transmitter and receiver electronics limit the number of IOs possible on-chip. As we discussed in Chapter 2, the electrical channel limitations require complex transceiver designs for supporting very high data rates. Although optical interconnections between electronic chips require the overhead of OE conversion, the high quality of optical channels prompts us to investigate the possibility of building small and simple electronics that allow large numbers of optical IOs per chip. Using optics is particularly promising because of the emergence of techniques for building dense 2D arrays of optical devices hybrid-integrated to the silicon chips [12] [13] [14] [54] [55] [56] [57] [58] [59].

This chapter is focused on the receiver design for optical interconnects. The overall performance of high speed optical links depends on the design of the receiver front-end. Receiver circuitry plus the OE conversion devices directly affect the maximum data rate, required optical power, electrical power consumption and area of the link. Receiver design objectives are strongly dependent on the application and overall system configuration. Optics has been used widely for long-haul high-speed data communication. Optical fibers confine and guide the beam from the transmitter side to the receiver. Since in optical signaling the maximum modulation frequency (data rate) is much smaller than the carrier frequency (frequency of the light), the

frequency dependent power loss in the fiber is very small. A flat response over the frequencies of interest corresponds to very small dispersion in the channel. In long-haul optical fiber communication, other types of dispersions such as modal dispersion can cause ISI [60]. Moreover, although the fiber loss is much smaller than the loss in copper wires, an optical beam that travels over many kilometers, experiences a significant power loss. Thus the main requirements for receivers in long-haul communications are very high sensitivity and bandwidth. Like in electrical serial links, long-haul optical links can afford high levels of design complexity to achieve good performance [60] [27] [28].

For short-haul parallel interconnections, the channel distortion and loss is negligible [10] [11]. However, limitations on power consumption, area, and noise generation become important constraints in the design of large numbers of high-speed IOs on a single chip. Integration of optical devices as well as cross-talk between different signals can add to the difficulties of having thousands of beams connecting different chips.

We start this chapter by briefly reviewing the basics of optical links and optical devices used at the receiver side. Since the receiver circuitry directly interfaces with the photodetectors, understanding the operation and characteristics of these devices is essential for an optimum design. In the second part of this chapter, we focus on the design of the receiver electronics. First we examine the prior art in frontend design for optical communication. Investigating the existing designs provides a motivation for the third part of this chapter, which describes the proposed double sampling/integrating front-end.

# 3.1 High-Speed Optical Interconnects Overview

With the recent advances in the optical technology, optical devices that can handle 10's of Gb/s data rates are available. These high performance optical devices facilitate very high data rates in optical interconnects, if high bandwidth transceiver circuitries, optimized for the characteristics of optical devices are designed.

In most optical data transmission systems, a coherent light from a laser is amplitude modulated with the transmit data. The amplitude modulation of the light can be done either by directly changing the current of the laser or by using an external optical modulator. A suitable laser choice for the direct modulation in a 2D array system is a vertical cavity surface emitting laser, VCSEL. While using direct modulation avoids the need for an external light source, VCSELs have a number of problems that are subjects of ongoing research. In order to avoid the turn-on delay of the laser, a bias current above the threshold is required. The power consumption and heat generation associated with biasing and modulation of VCSEL can change the properties of the lasers in large arrays. Thus external modulators are preferred in some designs. A promising modulator device is a multiple quantum-well (MQW) p-i-n diode [61]. The absorption properties of the quantum well structure in the i region are dominated by quantum-confined Stark effect (QCSE) [62]. With constant reverse voltage bias across the diode, the light absorption in the i region has a relatively narrow peak at a certain wavelength  $\lambda_1$ . Because of the QCS effect, changing the reverse voltage across the diode causes the absorption peak to shift to a different wavelength. This means that for a certain wavelength, changing the voltage across the diode causes significant change is the light absorption, which results in a modulation effect. These modulators can achieve data rates higher than 40Gb/s.

In most optical systems a 2-PAM modulation scheme is adopted. The modulated light is then sent to the receiver through an optical channel. For short-haul chip-chip interconnection, where a line of sight (LOS) is possible, the optical beam can be sent directly via the free space to the receiver, which was shown in Figure 1.1. For longer distances or places where a LOS is not available, optical fibers and waveguides are employed.

The data transmission scheme in the optical links is very similar to the electrical links, see Figure 3.1. A clock signal at the transmitter is used to define uniform time periods for sending the data signals successively one after another. At the receiver side a photodiode converts the optical signal to an electrical signal proportional to its input optical power. The receiver circuitry following the photodetector is responsible for resolving the data from the incoming electrical signal. Similar to electrical receivers,

Figure 3.1: Synchronous optical transmission over free space

a clock signal, synchronized with the data is used for sampling and data decision.

In the next section we investigate some of the properties of photodetectors used in high-speed optical interconnects. We are particularly interested in the surface normal devices that can be used for building dense 2D arrays, integrated or hybrid integrated with CMOS chips.

#### 3.1.1 Photodetectors

The two commonly used devices for OE conversion are p-i-n diodes and metal-semiconductor-metal MSM diodes. In both types of diodes, an electrical field in a semiconductor material, drives the electrons and holes generated by the incident photons to the terminals. The result is a current proportional to the number of photons absorbed per second. In a p-i-n diode, a reverse-bias across the diode ensures a strong field in the i region and a very small current in absence of light.

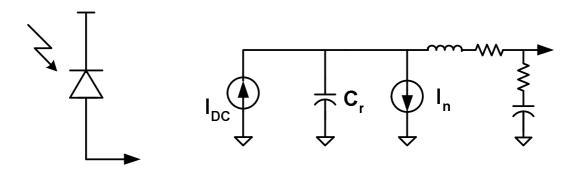

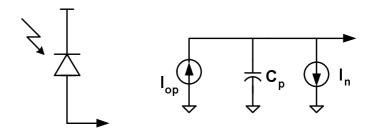

Figure 3.2 shows a simple electrical model for a photodetector. The optically generated current  $I_{op}$  is proportional to the input optical power  $P_{op}$ . The diode responsivity R is defined as  $R = I_{op}/P_{op}(A/W)$ . If the wavelength of the light is

Figure 3.2: Equivalent electrical model of a reverse-biased photodiode

$\lambda$ , the responsivity of a detector can be expressed as  $R = q\eta\lambda/hc^{-1}$  where  $\eta$  is the diode quantum efficiency. An optimally designed p-i-n diode, has  $\eta \simeq 1$ , which at 850nm implies R = 0.68A/W. Stand-alone GaAs and silicon p-i-n detectors have responsivities close to this value. The noise current  $I_n$  in Figure 3.2 is mainly due to the diode shot noise. Other sources of noise are the thermal noise of the series resistance and the background illuminations. In most designs the diode noise is much smaller than the noise of the receiver front-end circuitry.

Detector capacitance is usually the dominant input load for a receiver, impacting the sensitivity, electrical power consumption, and for some designs, the bandwidth of the front-end. Additionally, the detector integration scheme can affect the overall footprint and density of the front-end, which is particularly important for parallel interconnects. Photodetectors can be hybrid-integrated to CMOS chips after chip manufacture via a number of techniques, which are reviewed by Krishnamoorthy et al in [15] and Miller et al. in [58]. The advantage of hybrid integration is that the material and design of the photodetector is independent of the transistor technology. The most mature hybridization techniques are wire bonding and flip-chip bonding. Flip-chip bonding is a manufactureable technology enabling the integration of large device arrays. The performance tradeoffs between these two techniques are evaluated in [15]. Wire bonding has greater parasitic inductance and capacitance, reducing performance at high bit-rates as compared to flip-chip bonding. Hence flip-chip bonding

$<sup>^{1}</sup>hc/\lambda$  is the photon energy, where h is the Plank constant and c is the speed of light.

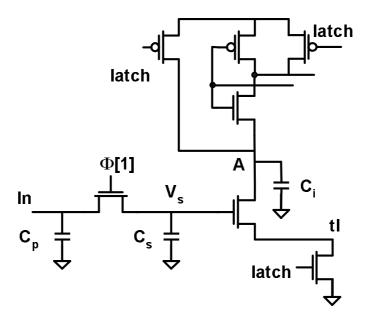

is more suitable for high-performance applications requiring minimum front-end capacitance. The capacitance of detectors themselves reduces as the width of the high field depletion region is increased. For p-i-n detectors this width is the width of the intrinsic region and for MSMs, it is the finger spacing. Increasing this critical dimension however, lowers the field and can make the detector slower, unless greater bias voltages are available. Capacitance can also be reduced by removal of excess substrate or the use of insulating substrates. For a given design, capacitance scales with the detector size, which is limited by the practical ability to focus light to spots smaller than 5 to 10 microns diameter. Wire-bonded off-the-shelf p-i-n detectors present a front-end capacitance in the range of 200fF or higher depending on the detector size. In [63] the measured capacitance of  $15\mu m \times 15\mu m$  flip-chip bonded GaAs p-i-n detectors is reported to be 52fF.