## THE LOAD-BALANCED ROUTER

A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

> Isaac Keslassy May 2004

© Copyright by Isaac Keslassy 2004 All Rights Reserved I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

> Nick McKeown (Principal Adviser)

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

Balaji Prabhakar

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

Mark Horowitz

Approved for the University Committee on Graduate Studies.

## Abstract

The function of a router is to switch arriving packets to their correct output destination. A router is built to achieve a specified capacity (the sum of the rates of its interfaces), and users expect a router to consistently achieve this capacity. However, no commercial high-speed router can guarantee today that it will achieve its full capacity for all arrival traffic patterns. This is because of the difficulty of scheduling its switch fabric, and will become even more difficult in the future as the number of interfaces and the interface speeds increase.

In this thesis, I advocate the use of a load-balanced router, a router architecture that is scalable and can guarantee a full capacity. A load-balanced router consists of two stages. First, a load-balancing stage spreads arriving packets equally among linecards. Then, a forwarding stage transfers packets from the linecards to their final destination. A load-balanced router does not use any centralized scheduler. Therefore, it can scale while providing the throughput guarantees needed by network operators.

In this thesis, I first explain how to simplify the load-balanced router architecture. While current routers commonly need switch fabrics with fast reconfiguration times, I show how to implement the load-balancing and forwarding stages of a load-balanced router using a single passive optical switch fabric with no reconfigurations. I also prove that among all possible switch fabrics with no reconfigurations, a specific loadbalanced switch fabric uniquely achieves the maximum possible guaranteed capacity.

A problem with the load-balanced router is that different packets of the same flow can take different paths, possibly leading to packet reordering. In this thesis, I introduce a simple distributed algorithm that can avoid packet reordering while providing delay and capacity guarantees.

Finally, I present a practical switch fabric architecture that would enable loadbalanced routers to scale to higher numbers of interfaces, and I prove that this architecture can adapt to arbitrary removals and additions of interfaces. I conclude by showing that the load-balanced router can help provide the scalability and capacity guarantees needed in the Internet.

## Contents

## Abstract

| 1 | Intr | ntroduction              |                                                           |    |

|---|------|--------------------------|-----------------------------------------------------------|----|

|   | 1.1  | 1 Background             |                                                           |    |

|   | 1.2  | The Load-Balanced Router |                                                           |    |

|   |      | 1.2.1                    | Assumptions                                               | 2  |

|   |      | 1.2.2                    | Basic Load-Balanced Router Architecture                   | 3  |

|   |      | 1.2.3                    | Definitions                                               | 4  |

|   |      | 1.2.4                    | 100% Throughput Guarantee of a Basic Load-Balanced Router | 6  |

|   |      | 1.2.5                    | Advantages of a Basic Load-Balanced Router                | 7  |

|   | 1.3  | Motiva                   | ation of the Thesis                                       | 8  |

|   |      | 1.3.1                    | Optical Switch Fabric                                     | 9  |

|   |      | 1.3.2                    | Packet Reordering                                         | 9  |

|   |      | 1.3.3                    | Pathological Traffic Patterns                             | 10 |

|   |      | 1.3.4                    | Missing Linecards                                         | 10 |

|   | 1.4  | Outlin                   | ne of the Thesis                                          | 11 |

| 2 | Mes  | sh Moo                   | del                                                       | 12 |

|   | 2.1  | From                     | Crossbar to Mesh                                          | 12 |

|   |      | 2.1.1                    | Mesh Architecture                                         | 12 |

|   |      | 2.1.2                    | Uniform Multiplexing                                      | 14 |

|   | 2.2  | 2.2 The Optimal Mesh     |                                                           |    |

|   |      | 2.2.1                    | Motivation                                                | 15 |

$\mathbf{iv}$

|   |     | 2.2.2  | Problem Formulation                                    | 15 |

|---|-----|--------|--------------------------------------------------------|----|

|   |     | 2.2.3  | Examples of Guaranteed Throughput                      | 19 |

|   |     | 2.2.4  | Properties of the Guaranteed Throughput                | 22 |

|   |     | 2.2.5  | The Biased Mesh                                        | 23 |

|   |     | 2.2.6  | Optimality of the Biased Mesh                          | 26 |

|   |     | 2.2.7  | Uniqueness of the Optimal Capacity Matrix              | 26 |

|   |     | 2.2.8  | Conclusions and Intuition                              | 27 |

| 3 | Pac | ket Re | eordering                                              | 28 |

|   | 3.1 | Preser | ntation of Packet Reordering                           | 28 |

|   |     | 3.1.1  | Example of Reordering in the Load-Balanced Router      | 28 |

|   |     | 3.1.2  | Consequences of Packet Reordering for Internet Traffic | 30 |

|   |     | 3.1.3  | Preventing Reordering                                  | 31 |

|   | 3.2 | Applie | cation Flow-Based Routing (AFBR)                       | 32 |

|   |     | 3.2.1  | How AFBR Works                                         | 32 |

|   |     | 3.2.2  | Properties of AFBR                                     | 33 |

|   | 3.3 | Unifor | rm Frame Spreading (UFS)                               | 33 |

|   |     | 3.3.1  | Presentation of UFS                                    | 33 |

|   |     | 3.3.2  | Advantages of UFS                                      | 35 |

|   |     | 3.3.3  | Filling a Frame                                        | 36 |

|   | 3.4 | Full C | Ordered Frames First (FOFF)                            | 37 |

|   |     | 3.4.1  | Presentation of FOFF                                   | 37 |

|   |     | 3.4.2  | Implementation                                         | 38 |

|   |     | 3.4.3  | Properties of FOFF                                     | 41 |

| 4 | Imp | olemen | tation                                                 | 43 |

|   | 4.1 | Archit | tecture Requirements                                   | 44 |

|   |     | 4.1.1  | A 100Tb/s Router Example                               | 44 |

|   |     | 4.1.2  | Architecture Requirements                              | 44 |

|   |     | 4.1.3  | Assumptions                                            | 45 |

|   | 4.2 | The H  | Iierarchical Mesh Architecture                         | 45 |

|   |     | 4.2.1  | Scaling the Number of Linecards                        | 45 |

|   |     | 4.2.2   | The Hierarchical Mesh                                        | 46 |

|---|-----|---------|--------------------------------------------------------------|----|

|   | 4.3 | The N   | MEMS-Based Architecture                                      | 47 |

|   |     | 4.3.1   | Writing the Mesh as a Sum of Matches                         | 47 |

|   |     | 4.3.2   | Using MEMS Switches                                          | 49 |

|   | 4.4 | Lineca  | ard Schedule                                                 | 51 |

|   |     | 4.4.1   | Determining the Number of MEMS Switches                      | 51 |

|   |     | 4.4.2   | The Linecard Schedule Problem                                | 53 |

|   |     | 4.4.3   | Number of MEMS Switches Needed for a Linecard Schedule $~$ . | 55 |

|   |     | 4.4.4   | Valid Schedules                                              | 56 |

|   |     | 4.4.5   | Constructing a Valid G-G Schedule                            | 59 |

|   |     | 4.4.6   | Valid L-L Schedule                                           | 61 |

|   |     | 4.4.7   | From a Valid G-G Schedule to a Valid L-G Schedule            | 61 |

|   |     | 4.4.8   | Practical Considerations                                     | 66 |

|   | 4.5 | Practi  | icality and Reliability of the 100Tb/s Router                | 67 |

|   |     | 4.5.1   | The Electronic Crossbars                                     | 68 |

|   |     | 4.5.2   | Packaging 100Tb/s of MEMS Switches                           | 70 |

|   |     | 4.5.3   | Fault-Tolerance                                              | 70 |

|   |     | 4.5.4   | Building 160Gb/s Linecards                                   | 70 |

|   |     | 4.5.5   | Packaging 16 Linecards in a Rack                             | 71 |

|   |     | 4.5.6   | Implementation Summary                                       | 71 |

| 5 | Cor | ıclusio | n                                                            | 72 |

|   | 5.1 | Towar   | rds a Simpler Internet                                       | 72 |

|   | 5.2 | Futur   | e Directions in Load-Balanced Router Architectures           | 73 |

|   | 5.3 | Apply   | ring Load-Balanced Routing to Network Design                 | 74 |

| A | Opt | timalit | y of the Biased Mesh                                         | 76 |

| в | Uni | quene   | ss of the Optimal Capacity Matrix                            | 81 |

| С | Pro | of tha  | t UFS Has 100% Throughput                                    | 85 |

| _ |     |         |                                                              | 0  |

| D  | Proof that FOFF Sends Packets in Order                               |  |     |  |  |

|----|----------------------------------------------------------------------|--|-----|--|--|

|    | D.1 Intuition on the FOFF scheme                                     |  | 88  |  |  |

|    | D.2 Assumptions                                                      |  | 88  |  |  |

|    | D.3 Notations and Lemmas                                             |  | 89  |  |  |

|    | D.4 Theorem                                                          |  | 93  |  |  |

|    | Proof of Average Packet Delay with FOFF                              |  |     |  |  |

| F  | Proofs for the Linecard Schedule                                     |  |     |  |  |

|    | F.1 Proof for Theorem 11                                             |  | 103 |  |  |

|    | F.2 Proofs for the Construction of the Valid G-G Schedule $\ldots$ . |  | 103 |  |  |

|    | F.3 Ford-Fulkerson Algorithm                                         |  | 108 |  |  |

| Bi |                                                                      |  |     |  |  |

## List of Tables

| 4.1 | Example of application of the algorithm for constructing a valid G-G |    |

|-----|----------------------------------------------------------------------|----|

|     | schedule                                                             | 61 |

# List of Figures

| Basic load-balanced router                                                         | 3                                                                                                                                                                                              |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Example of reordering in the basic load-balanced router.                           | 9                                                                                                                                                                                              |

| Load-balanced router architecture based on a double mesh                           | 13                                                                                                                                                                                             |

| Load-balanced router architecture based on (a) a single mesh, and (b)              |                                                                                                                                                                                                |

| an AWGR                                                                            | 14                                                                                                                                                                                             |

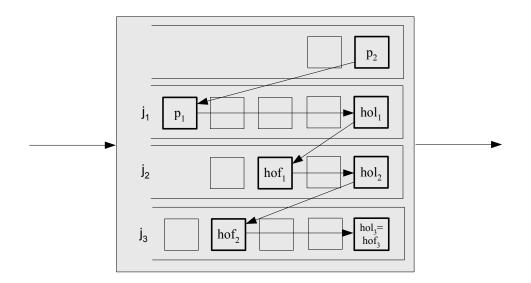

| Example of packet reordering in a load-balanced router                             | 29                                                                                                                                                                                             |

| Illustration of the UFS algorithm                                                  | 35                                                                                                                                                                                             |

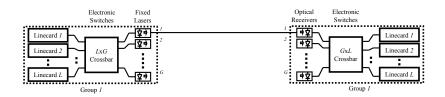

| Hierarchical mesh architecture                                                     | 46                                                                                                                                                                                             |

| Hierarchical mesh architecture populated with only the first group.                | 47                                                                                                                                                                                             |

| Partitioned switch fabric                                                          | 48                                                                                                                                                                                             |

| Decomposition of a mesh into matches, with (a) a uniform mesh having               |                                                                                                                                                                                                |

| all groups, and (b) a mesh with a single group                                     | 49                                                                                                                                                                                             |

| MEMS-based architecture.                                                           | 50                                                                                                                                                                                             |

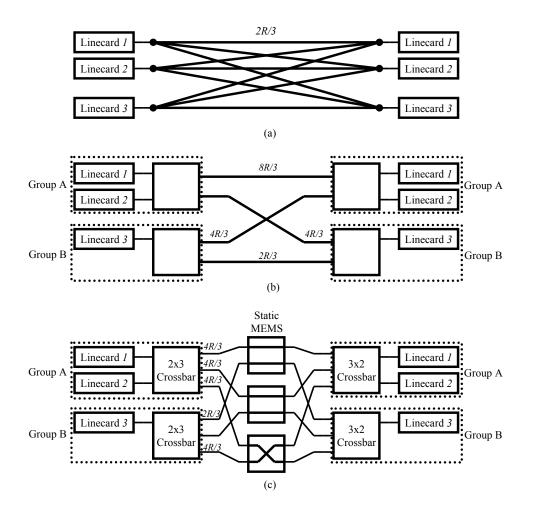

| Example of a MEMS-based switch architecture with three linecards in                |                                                                                                                                                                                                |

| two groups. (a) A full line<br>card mesh logical view. (b) Group ${\cal B}$ is not |                                                                                                                                                                                                |

| fully populated, and so the rates between groups are different. (c) The            |                                                                                                                                                                                                |

| configuration of MEMS switches to achieve the required rates                       | 52                                                                                                                                                                                             |

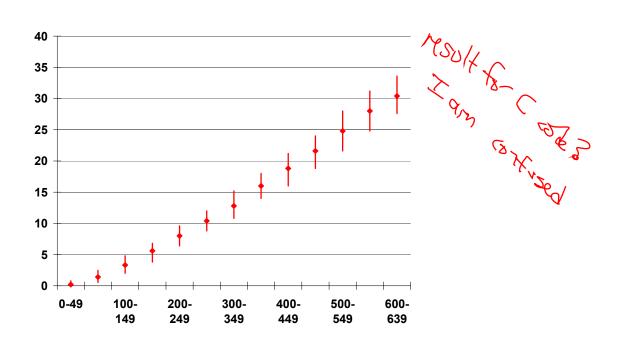

| Running time in milliseconds of the algorithm implementation, as a                 |                                                                                                                                                                                                |

| function of the number of linecards. The plot represents the worst-                |                                                                                                                                                                                                |

| case, average and best-case values for each range                                  | 67                                                                                                                                                                                             |

|                                                                                    | Example of reordering in the basic load-balanced router Load-balanced router architecture based on a double mesh Load-balanced router architecture based on (a) a single mesh, and (b) an AWGR |

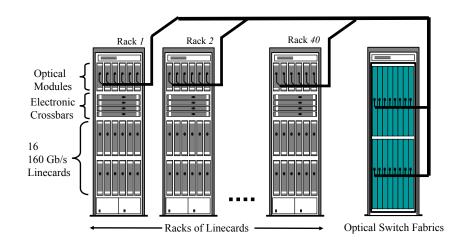

| 4.8 | Possible system packaging for a 100 Tb/s router with 640 linecards           |     |

|-----|------------------------------------------------------------------------------|-----|

|     | arranged as 40 racks with 16 linecards per rack                              | 68  |

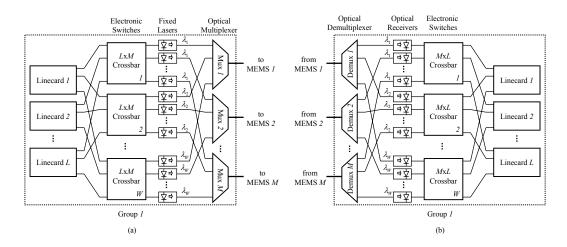

| 4.9 | Bit-sliced crossbars for the MEMS-based architecture. (a) represents         |     |

|     | the transmitting side of the switch fabric. (b) represents the receiving     |     |

|     | side of the switch fabric.                                                   | 69  |

|     |                                                                              |     |

| D.1 | Proof notations                                                              | 90  |

| D.2 | View of the reordering buffer of output $k$ . In this example, the head of   |     |

|     | line of queue $j_3$ is also head of flow, and therefore can leave the output |     |

|     | without any packet reordering                                                | 94  |

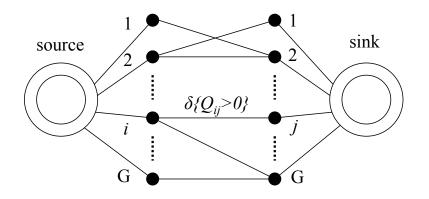

| F.1 | Illustration of the Ford-Fulkerson construction                              | 108 |

## Chapter 1

## Introduction

## 1.1 Background

The Internet consists of end-hosts interconnected using links and routers. Packets sent by a source end-host transit through different links before arriving to their destination end-host. Routers form the junction between links. The role of a router is to switch each arriving packet from its input link to its output link. Therefore, a router logically consists of two consecutive stages. First, a lookup stage determines the appropriate output link of each packet based on the address of its destination. Then, a switching stage transfers the packet from its input link to its output link.

In this thesis, we will focus on the switching stage of high-capacity routers. Let a flow be the set of all packets with the same input and output links. Today, in the most common router architectures, packets from the same flow take the same path through the router. However, these architectures typically share several problems. They often involve a complex centralized scheduler. They commonly do not provide the throughput guarantees that network operators need to make efficient use of their expensive long-haul links. And, because all packets from the same flow take the same path, they are also sensitive to single-point failures. These considerations have lead to a recent interest in introducing parallelism inside routers, by having the packets take different paths. Examples of multi-path routers include Parallel Packet Switch (PPS) routers [42, 44, 45], Parallel Shared Memory (PSM) and Distributed Shared Memory (DSM) routers [46], Memory-Space-Memory (MSM) routers [24, 25], buffered Clos networks [17, 23, 63], and ring, torus, and hypercube interconnection networks [30, 31, 38, 67, 73, 74].

However, these multi-path routers commonly share the very same problems they were supposed to solve in single-path routers. In particular, they either require complex, centralized schedulers, or rely on simple distributed scheduling algorithms that lack throughput guarantees. More recently, C.S. Chang et al. introduced the Load-Balanced Router architecture [20, 21]. This architecture is based on load-balancing packets uniformly inside the router before forwarding them to their correct destination, an idea first introduced by Valiant *et al.* [82, 83]. As developed later in the Introduction, C.S. Chang *et al.* show that a load-balanced router does not require any scheduler and that it can guarantee 100% throughput for a broad class of traffic. Therefore, the load-balanced router is not subject to the two main problems commonly present in former architectures: centralized scheduling and the lack of throughput guarantees needed by network operators. This makes the load-balanced router an appealing architecture to study. However, as detailed later, the load-balanced router suffers from several problems, such as packet reordering and the need for frequent switch fabric reconfigurations. In this thesis, we will show how to solve these problems, and present how the load-balanced router can help improve router performance.

## 1.2 The Load-Balanced Router

## **1.2.1** Assumptions

Throughout the thesis, we will assume for simplicity that all incoming variablesize packets are segmented into *fixed-size packets*, or simply *packets*, and reassembled when leaving the router. We will say that links are connected to routers through *linecards*, and denote by N the number of input (and output) linecards. We will also assume that all linecards have the same line rate and that time is slotted, so that at most one packet can arrive to any input port and at most one packet can depart from any output port at each time-slot. Finally, we will assume that there is no packet in

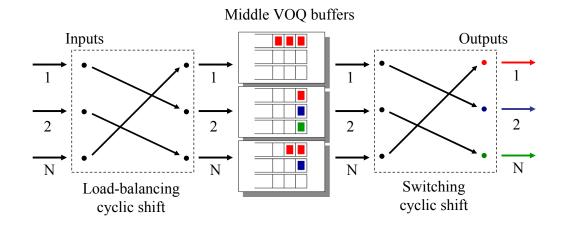

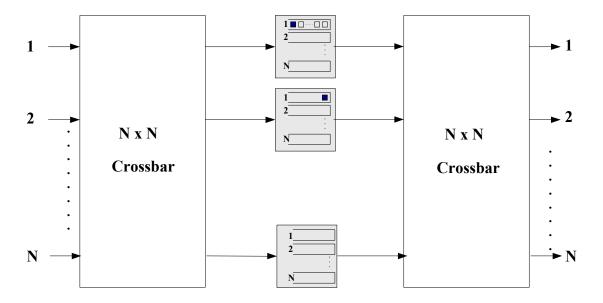

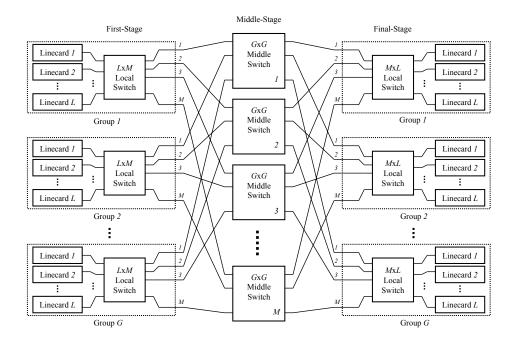

Figure 1.1: Basic load-balanced router.

the router initially.

### **1.2.2** Basic Load-Balanced Router Architecture

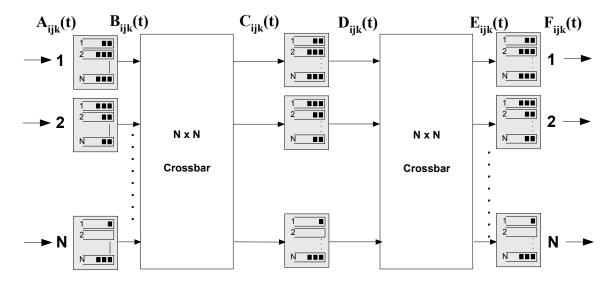

A basic load-balanced router is shown in Figure 1.1. It consists of a single stage of N buffers, sandwiched by two identical stages of switching. Each buffer is partitioned into N separate FIFO (First-In-First-Out) queues, one per output (hence we call them virtual output queues, VOQs). Each of the two switching stages goes through the same pre-determined cyclic shift configuration. At time t, input i of each switching stage is connected to output  $[(i + t - 1) \mod N] + 1$ . Therefore, the configuration is a cyclic shift, and each input is connected to each output exactly  $\frac{1}{N}$ -th of the time, regardless of the arriving traffic. We will call each switching stage a *fixed, equal-rate switch*.

Although they are identical, it helps to think of the two stages as performing different functions. The first stage is a load-balancer that spreads traffic over all the VOQs. The second stage is an input-queued crossbar switch in which each VOQ is served at a fixed rate. When a packet arrives to the first stage, it is immediately transferred to an intermediate input, which depends on the current configuration of the load-balancer. In the intermediate input, the packet is stored in a VOQ according to its eventual output. Sometime later, the VOQ will be served by the second fixed, equal-rate switch. The packet will then be transferred across the second switch to its output, from where it will depart the system.

## **1.2.3** Definitions

At first glance, it is not obvious how the load-balanced router can make any throughput guarantees; after all, the sequence of switch configurations is predetermined, regardless of the state of the VOQs or the traffic rates. In a conventional single-stage crossbar switch, throughput guarantees are only possible if a scheduler configures the switch based on the knowledge of the states of all the VOQs or all the traffic rates. However, C.S. Chang *et al.* prove in [20] that the load-balanced router, without any scheduler, will still be able to provide 100% throughput for a broad class of arrival traffic. This is an important theorem for the understanding of the loadbalanced router, and thus we choose to reproduce it here. Let's first introduce all the definitions needed to present the theorem.

Let  $a = \{a(t), t \ge 1\}$  be the sequence of traffic arrivals to the first switching stage,  $b = \{b(t), t \ge 1\}$  the sequence of traffic departures from the first switching stage (and arrivals to the buffering stage),  $q = \{q(t), t \ge 1\}$  the sequence of queue lengths, and  $P = \{P(t), t \ge 1\}$  the sequence of switch permutation matrices. Pdefines the connections between the inputs (rows) and the outputs (columns) of the first switching stage. As defined above, at time t, input i of each switching stage is connected to output  $[(i+t-1) \mod N] + 1$ . Therefore, P is periodic, and P(t) is the  $[t \mod N]$ -th extra-diagonal matrix. For instance, P(0) = P(N) = P(2N) = ... = Id, the identity matrix. In addition, we have  $b = P \cdot a$ .

For each sequence a, let  $\theta_s(a) = \{a(t+s), t \ge 1\}$  represent the time-shifted version of a.

Stationary: A stochastic sequence a is stationary if it has the same joint distribution as its time-shifted version, i.e. for any time-shift s and any A,

$$Pr(a \in A) = Pr(\theta_s(a) \in A).$$

In other words, a is stationary if all its statistical properties are invariant with respect

to time.

**Ergodic:** A stationary sequence a is ergodic if for all A, B,

$$\lim_{t \to \infty} \frac{1}{t} \sum_{s=1}^{t} Pr(\theta_s(a) \in A, a \in B) = Pr(a \in A)Pr(a \in B).$$

Intuitively, a is ergodic if it tends in probability to a limiting form that is independent of the initial conditions. In addition, for a stationary ergodic sequence a, timeaverages are equal to ensemble-averages, i.e.

$$\lim_{t \to \infty} \frac{1}{t} \sum_{s=1}^{t} a(s) = Ea(1), \ a.s.$$

Weakly mixing: A stationary sequence a is weakly mixing if for all A, B,

$$\lim_{t \to \infty} \frac{1}{t} \sum_{s=1}^{t} |Pr(\theta_s(a) \in A, a \in B) - Pr(a \in A)Pr(a \in B)| = 0$$

Both weak mixing and ergodicity are measures of how fast the present loses influence over the future. Weak mixing reflects a stronger memory loss over time, as weak mixing implies ergodicity. Most Internet traffic models are stationary and weakly mixing, and therefore also ergodic. Since stationarity of traffic models is often implied by the constancy of the traffic generator, let's illustrate the weak mixing property of Internet traffic models. Bernoulli traffic is weakly mixing because successive events are independent. On/off Markov bursty traffic is weakly mixing because the influence of the present on the future decreases geometrically. Fractional Gaussian noise, a model for self-similar traffic, is also weakly mixing [60, 85]. However, periodic traffic is not weakly mixing because the influence of the present does not decrease over time.

Admissible mean rate: Let r = Ea(1) be the mean rate matrix of a stationary ergodic arrival sequence a.  $r_{ij}$  represents the mean arrival rate for packets going from input i to output j. Then r is admissible if for all j,

$$\sum_{i=1}^{N} r_{ij} < 1,$$

and for all i,

$$\sum_{j=1}^{N} r_{ij} < 1.$$

100% throughput: A switch has 100% throughput for a given class of arrival traffic if for any arrival sequence with admissible mean rate, q(t) is upper-bounded by a random matrix that converges in distribution.

Such a property implies that for any arbitrarily small probability  $\epsilon > 0$ , there is a corresponding queue size such that after some time-slot, the probability that q will exceed this queue size is bounded by  $\epsilon$ . When q is ergodic, this also implies that the workload will only exceed this queue size at most a fraction  $\epsilon$  of the time.

Work-conserving system: A queueing system is work-conserving if and only if it is non-idling when there are customers in the queue.

## 1.2.4 100% Throughput Guarantee of a Basic Load-Balanced Router

**Theorem 1** A basic load-balanced router guarantees 100% throughput for any stationary and weakly mixing arrival traffic with admissible mean rate.

*Proof:* The proof follows the proof in [20], but with a few changes. In [20], the authors assume that the two crossbars cycle through the same set of N permutations in the same order, but that they do not necessarily start with the same permutation. In particular, the states at time t = 0 of both crossbars are chosen independently at random among the N possible permutations. In this thesis, for practical purposes, we assume that at each time-slot the two crossbars use the same permutation, and that the initial permutation at t = 0 is fixed. However, such an assumption implies that the sequence P is not stationary and ergodic, since P(0) is fixed. This property is needed in the proof. Therefore, without loss of generality, we (theoretically) re-assign the start of time in the router uniformly at random among time-slots  $\{-N, ..., -1\}$ . As a consequence, the state of the first permutation P(0) is chosen uniformly at random among the N possible values, and it can be checked that P is stationary and ergodic. This change of time definition does not affect the arrivals, which are

stationary and independent of P. The expected value of P(t) is  $EP(t) = \frac{1}{N}e$ , where e is the  $N \times N$  matrix with all ones.

Let r be the admissible mean rate of a. Since  $b = P \cdot a$ , and a and P are stationary and independent, b is stationary with average rate

$$Eb(t) = EP(t) \cdot Ea(t) = \frac{1}{N}e \cdot r.$$

In addition, a is weakly mixing and P is ergodic, therefore b is ergodic (Theorem 2.6.1 in [66]). Using the fact that b and P are stationary and ergodic, we get:

$$\lim_{t \to \infty} \frac{1}{t} \sum_{s=1}^{t} \left( b(s) - P(s) \right) = Eb(t) - EP(t) = \frac{1}{N}e \cdot r - \frac{1}{N}e < 0, \ a.s$$

As proved by Loynes [7, 18, 57], if arrivals and services of a work-conserving switch are stationary and ergodic, and at any time the expected number of arrivals is less than the expected number of services, then the switch has 100% throughput. Let's now examine the VOQ of intermediate input *i* containing all packets destined to output *j*. This VOQ is serviced exactly every *N* time-slots as long as it is non-empty. Let's examine this VOQ every *N* time-slots, and define the sampled state of the VOQ as the sampled VOQ. At every sample, the sampled VOQ is serviced as long as it is non-empty. Therefore, the sampled VOQ is work-conserving. In addition, *b* and *P* are stationary and ergodic, and Eb(t) - EP(t) < 0. Therefore, the arrivals and services to the sampled VOQ are stationary and ergodic, and the expected number of arrivals is less than the expected number of services. Using the above result by Loynes, it follows that the switch has 100% throughput.

## 1.2.5 Advantages of a Basic Load-Balanced Router

In addition to the 100% throughput property presented above, a basic loadbalanced router has several other appealing properties when compared with traditional centralized-scheduler architectures. These properties involve all the main router elements: *scheduling*, *control*, *switch fabric* and *linecards*. First, a basic load-balanced router uses no centralized scheduler. This is unlike the most common current router architectures, which use a centralized arbiter that computes a match between the inputs and the outputs for each time-slot [2, 3, 28, 56, 58, 59, 79]. Indeed, a basic load-balanced router does not need *any* scheduling, since the sequence of crossbar permutations is predetermined.

Second, a basic load-balanced router does not need any back-and-forth exchange of VOQ-state and scheduling-decision information between the linecards and a centralized scheduler, since there is no centralized scheduler. This simplifies *the switch control.* It also removes the loss of bandwidth due to the exchange of information.

Third, a basic load-balanced router simplifies the switch fabric. It uses only N states for the switch fabric out of the possible N! states. The state sequence is predetermined, and not computed at each time slot.

Finally, a basic load-balanced router simplifies *the linecards*, and especially the buffering stage. It only uses one stage of buffering, while typical centralized-scheduler switches run the switch fabric faster than the line rate and require two stages of buffering (at the inputs and at the outputs). A basic load-balanced router also typically requires less buffering per linecard because it spreads long bursts across the intermediate inputs, as shown in [20].

All these properties suggest that it might be possible to scale a basic load-balanced router more easily than traditional architectures. The remainder of the thesis considers problems that might occur with the load-balanced router, and how we could solve them.

## 1.3 Motivation of the Thesis

Several problems in a basic load-balanced router architecture prevent its implementation in high-speed routers. This thesis aims to solve these problems.

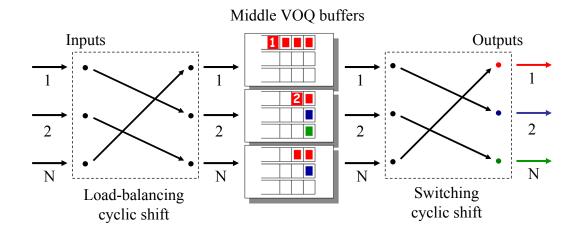

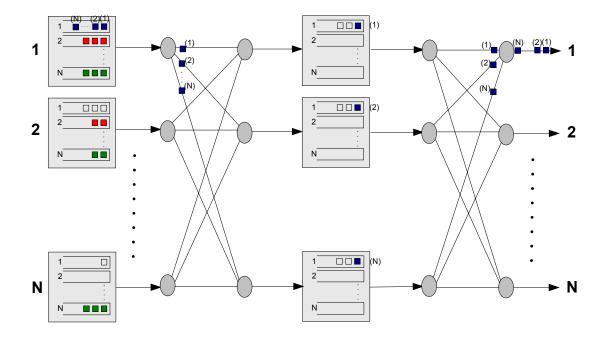

Figure 1.2: Example of reordering in the basic load-balanced router.

### **1.3.1** Optical Switch Fabric

Using optics in the switch fabric is often desired in order to scale routers to higher speeds and consume less power that electronic interconnects. However, because of the switch fabric reconfigurations, two reasons prevent the use of high-capacity optical switch fabrics in the basic load-balanced router. First, high-capacity optical switch fabrics often have slow reconfiguration times. For instance, MEMS-switch reconfiguration times are in tens of milliseconds [64, 70]. However, with 64-byte packets and speeds of 40-160 Gbps, a reconfiguration time of a few nanoseconds is needed. In addition, tunable optical devices are often significantly more expensive than fixed devices. Consequently, our objective will be to find a mechanism that allows for the use of optics in a load-balanced router without any need for reconfiguration.

## 1.3.2 Packet Reordering

Another problem in the load-balanced router is that packets can be reordered. This is because the load-balancer spreads packets without regard to their final destination, or to when they will depart from the VOQs. Figure 1.2 illustrates how two packets arriving back to back at the same input, and destined to the same output, are spread to different intermediate linecards. These two packets, numbered 1 and 2, are successively sent to the first two intermediate linecards. Since the intermediate linecard of packet 1 has a higher VOQ occupancy than the intermediate linecard of packet 2, packet 1 will leave the router after packet 2. Therefore, the two packets leave the router out-of-order.

While reordering packets is allowed (and is common [10, 48]) in the Internet,<sup>1</sup> network operators generally insist that routers do not reorder packets belonging to the same application flow. In addition, in its current version, TCP does not perform well when packets arrive to the destination out of order. Such packets can be perceived as loss indicators and might trigger un-necessary retransmissions, thus reducing the throughput provided to the application [13].

## **1.3.3** Pathological Traffic Patterns

Even though the load-balanced router guarantees 100% throughput for a large class of traffic patterns, it is still vulnerable to some pathological traffic patterns. For instance, if at each time-slot t a packet arrives to input  $[t \mod N] + 1$  and is destined to output 1, it will always be placed in the same first VOQ of the first intermediate linecard. As a consequence, the traffic arriving to the forwarding stage is clearly non uniform, and its throughput is only  $\frac{1}{N}$ . This illustrates how pathological periodic traffic patterns prevent a basic load-balanced router from providing significant throughput guarantees.

### 1.3.4 Missing Linecards

A last problem with the predetermined configuration of a basic load-balanced router is that the router does not work properly when a linecard is missing. This situation might happen if the operator wants to slowly build up the number of linecards instead of installing all the linecards at once. It might also occur if a linecard fails or if linecards are removed in order to connect some lines to a different router.

The basic load-balanced router architecture assumes that any input linecard equally load-balances its traffic across all intermediate linecards. However, if an

$<sup>^1 \</sup>mathrm{Internet}\ \mathrm{RFC}\ 1812$  "Requirements for IP Version 4 Routers" [8] does not forbid packet reordering.

intermediate linecard is missing, packets going through this linecard will be lost. Therefore, this will prevent the load-balanced router from working as expected.

## 1.4 Outline of the Thesis

This thesis explains how a load-balanced router can be implemented in high-speed routers. The following chapters model and solve the problems exposed above.

Chapter 2 shows how to use optics in the switch fabric. It proposes an implementation of the load-balanced router based on meshes, and explains why this implementation involves no reconfiguration. It also presents a simple implementation using a passive AWGR (Arrayed Waveguide Grating Router) optical device. Finally, it proves that among all possible switch fabrics with no reconfigurations, a specific load-balanced switch fabric uniquely achieves the maximum possible guaranteed throughput.

Then, Chapter 3 shows how to avoid both the packet reordering and the pathological traffic pattern problems by using a novel algorithm. It shows that this algorithm keeps packets in order, is practical to implement, and prevents pathological traffic patterns. It also proves that for any arbitrary adversarial traffic, this algorithm keeps the average packet delay through the switch within a constant from that of an ideal (output-queued) switch.

In Chapter 4, we explain why the implementations mentioned before do not adapt easily to larger port counts and to linecard failures. This leads us to introduce an architecture based on MEMS (MicroElectroMechanical Systems). This architecture illustrates the implementation that we would choose were we to build a high-speed router. We then further study how practical and reliable it is, before concluding on two problems related to this implementation: how to arrange the MEMS switches and how to find a correct linecard schedule upon linecard failure or addition.

We conclude this thesis in Chapter 5, by explaining how a load-balanced router helps scaling routers while achieving 100% throughput guarantee.

Finally, the appendices will contain many of the proofs needed in this thesis.

## Chapter 2

## Mesh Model

## 2.1 From Crossbar to Mesh

## 2.1.1 Mesh Architecture

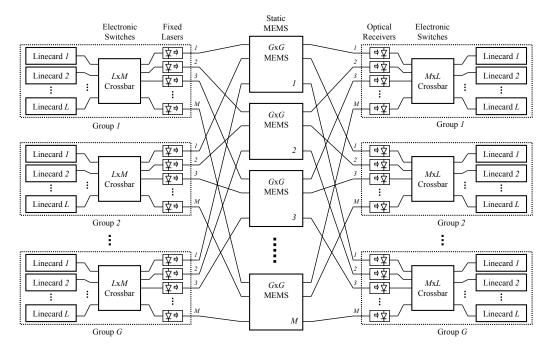

We introduced in the Introduction the load-balanced router, a new architecture that requires no centralized scheduler and yet guarantees 100% throughput under a broad class of traffic patterns. In this chapter, we will present how the loadbalanced router can be practically implemented using an optical switch fabric with no reconfiguration.

The load-balanced router architecture relies on two fixed, equal-rate switches. Each of these switches connects any input to any output exactly  $\frac{1}{N}$ -th of the time, regardless of the arriving traffic. We saw in the Introduction that these fixed, equal-rate switches could be implemented using two  $N \times N$  switch fabrics that are reconfigured every timeslot. However, if we were to use an optical switch fabric, this constraint would hinder our ability to scale to higher speeds. For instance, MEMS-switch reconfiguration times are in tens of milliseconds [64, 70], while we would need reconfiguration times of a few nanoseconds. In addition, a system with no reconfigurations. Therefore, we would like to replace this fixed, equal-rate switch with a fixed system that does not need any reconfigurations. This is realized by using a fixed mesh of optical channels.

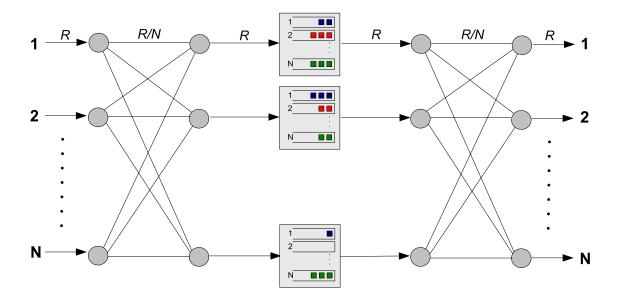

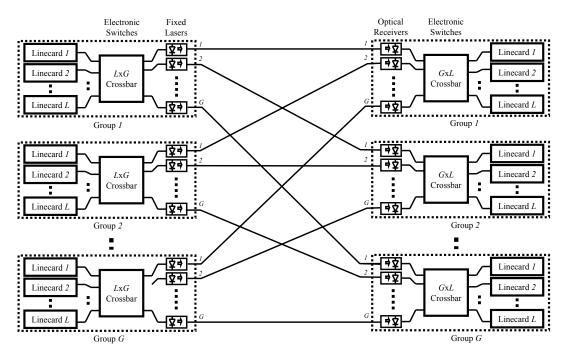

Figure 2.1: Load-balanced router architecture based on a double mesh.

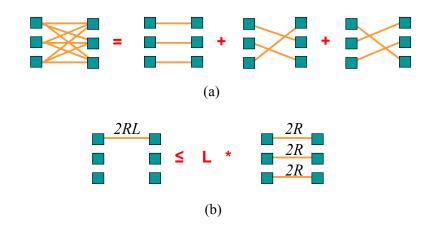

A first observation is that we can replace each fixed equal-rate switch with  $N^2$  fixed channels at rate R/N, as illustrated in Figure 2.1. Hence, each switch is replaced by a uniform mesh. The rates provided between any switch input and any switch output will stay the same. Therefore, the switch is still a fixed, equal-rate switch.

A second observation is that we can replace the two meshes with a single mesh running twice as fast, as shown in Figure 2.2(a). This is possible because in a physical implementation, a linecard contains an input, an intermediate input and an output. Every packet traverses the mesh twice, each time at rate R/N, therefore the total channel rate is 2R/N. After a packet crosses the switch the first time, it is stored in an intermediate linecard; from there, it crosses the switch again to reach the output linecard. Note that this architecture will be further analyzed and extended in Chapter 4, in order to provide more scalability and flexibility to the switch.

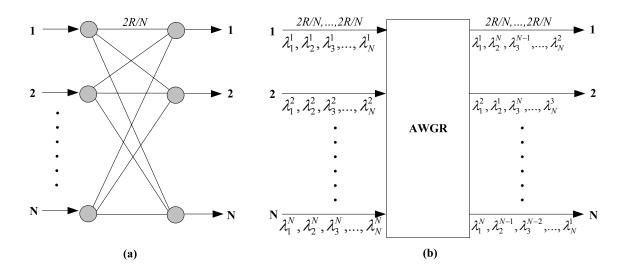

A third observation is that a uniform mesh with optical channels can be replaced by an Arrayed Waveguide Grating Router (AWGR), as represented in Figure 2.2(b). Input *i* transmits *N* distinct channels on its outgoing fiber. Each different channel  $\lambda_w^i$  is transmitted at rate 2R/N on a specific wavelength  $\lambda_w$ . The AWGR, a passive optical device, shuffles the channels such that each channel of a given input is destined

Figure 2.2: Load-balanced router architecture based on (a) a single mesh, and (b) an AWGR.

to a different output. As a result, the system behaves as a single mesh — indeed, it is a mesh, but based on an AWGR instead of the more conventional  $N^2$  fibers. Its main advantage is the reduction in the number of fibers needed from  $N^2$  to 2N.

## 2.1.2 Uniform Multiplexing

How is it that we can implement the load-balanced router equivalently using a crossbar, a mesh or an AWGR? Are there any other equivalent architectures?

Actually, the load-balanced router architecture only assumes that the switch fabric is able to spread arriving traffic uniformly across the N outputs, and each output is able to receive traffic uniformly from the N inputs. This simply is a uniform multiplexing (and demultiplexing), a process well-known in the literature. As a consequence, the uniform multiplexing of arriving traffic could be realized by Time Division Multiplexing (crossbar), Space Division Multiplexing (mesh), Wavelength Division Multiplexing (AWGR), and so on, as well as a combination of these methods. Any other architecture would similarly be sufficient, as long as it can uniformly multiplex and demultiplex traffic.

## 2.2 The Optimal Mesh

## 2.2.1 Motivation

Perhaps the most interesting characteristic of the load-balanced router is that it provably achieves 50% throughput with a single switch fabric (and therefore 100% throughput with two switch fabrics or a speedup of two) for a broad class of arrivals.

However, it is not obvious why the switch needs to have a fixed, equal rate, i.e. why the mesh needs to be uniform. Do all links need to have a capacity of R/N? How would the throughput change if the mesh was not uniform? What arrangement of link capacities maximizes the throughput? If linecards were interconnected instead using a ring, a torus or a hypercube, would throughput be higher?

To make the comparison, we will consider a load-balanced switch with arbitrary link capacities and an arbitrary load-balancing policy. We will allow packets to take any path through this switch, using any number of hops. We will only impose that this switch does not use any speed-up, and that each packet goes at least once through the switch. Then, we will determine the architecture that has the highest guaranteed throughput.

Below, we will first define the problem and provide some examples. Then, we will prove that a given biased mesh reaches the maximum throughput and is unique in doing so. Finally, we will provide some intuition on the results.

## 2.2.2 Problem Formulation

#### Notations and Assumptions

Define a *doubly stochastic* matrix as a non-negative matrix with all row and column sums equal to 1. Similarly, an *admissible* (or doubly sub-stochastic) matrix is a nonnegative matrix with all row and column sums upper-bounded by 1. Finally, define the time unit such that each node can send and receive at most one bit per second (if the maximum node speed is R, scale the time unit by a factor  $\frac{1}{R}$ ).

A link of fixed capacity  $C_{ij}$  connects node *i* to node *j*, where  $1 \leq i, j \leq N$ . The matrix  $C = [C_{ij}]_{1 \leq i, j \leq N}$  is the capacity matrix, and any node *l* can send up to  $\sum_{j=1}^{N} C_{lj}$  (and likewise receive at most  $\sum_{i=1}^{N} C_{il}$ ) bits per time unit to and from the N nodes (including itself). Since every node l can send and receive at most one bit per time unit,  $\sum_{i=1}^{N} C_{il} \leq 1$  and  $\sum_{j=1}^{N} C_{lj} \leq 1$ , therefore the matrix C is admissible. The capacity matrix C defines the architecture; for example, the *uniform mesh architecture* (in which nodes are connected to each other with equal capacity), corresponds to the uniform matrix C where  $C_{ij} = 1/N$ . Similarly, a ring could be defined by  $C_{ij} = \mathbf{1}_{j=i+1 \mod N}$ .

Denote by T the arrival traffic rate matrix, with  $T_{ij}$  the arrival rate to node i of packets destined for node j. We will assume that T is admissible, since it cannot be supported otherwise. Suppose we want to load-balance these packets across multiple paths, each path having an arbitrary number of hops. If P(i, j) is the set of paths between nodes i and j, then any path  $p \in P(i, j)$  can be represented as  $(i \rightarrow node_1 \rightarrow$  $node_2 \rightarrow \ldots \rightarrow j)$ . Let  $T_{ij}^p$  be the rate of the flow carried by p. If the arrival traffic rate matrix T is feasible (i.e. the network has 100% throughput for T), it is possible to decompose T into several paths p, and therefore for all i, j,

$$T_{ij} = \sum_{p \in P(i,j)} T_{ij}^p.$$

(2.1)

Similarly, we'll define the effective load matrix L using for all i, j:

$$L_{ij} = \sum_{\{p:(i \to j) \in p\}} T_{ij}^{p}.$$

(2.2)

The effective load of a link is the sum of the loads of the paths sharing the link. A solution is feasible if and only if we can find a decomposition of T such that  $L \leq C$ , i.e. no link is over-booked.

#### **Problem Intuition**

Assume for a moment that N = 2 and that we use a uniform mesh architecture, with capacity matrix

$$C = \left(\begin{array}{cc} 0.5 & 0.5\\ 0.5 & 0.5 \end{array}\right).$$

We'll use this example to gain some intuition about the throughput of interconnection networks.

If the arrival rate matrix is

$$T_1 = \left(\begin{array}{rrr} 0.9 & 0\\ 0 & 0 \end{array}\right)$$

then we can't send traffic at rate 0.9 on the path  $1 \rightarrow 1$ , because the capacity is limited by  $C_{11} = 0.5$ . Therefore, we need to load-balance traffic, by using the spare capacity of other links. We will send 0.5 on the direct path  $1 \rightarrow 1$ , and the remaining 0.4 on the alternative path  $1 \rightarrow 2 \rightarrow 1$ . The resulting load matrix is

$$L_1 = \left(\begin{array}{cc} 0.5 & 0.4\\ 0.4 & 0 \end{array}\right),$$

and  $L_1 \leq C$ . Clearly the direct path is not always sufficient to carry the required rate matrix, but in this case it is possible to use a load-balanced path in order to carry it.

Not all rate matrices are feasible, i.e. the throughput is not always 100%. Consider the arrival rate matrix

$$T_2 = \left(\begin{array}{cc} 0.9 & 0\\ 0 & 0.9 \end{array}\right).$$

Sending 0.5 on  $1 \rightarrow 1$ , 0.4 on  $1 \rightarrow 2 \rightarrow 1$ , 0.5 on  $2 \rightarrow 2$  and 0.4 on  $2 \rightarrow 1 \rightarrow 2$ , the load matrix is

$$L_2 = \left(\begin{array}{cc} 0.5 & 0.8\\ 0.8 & 0.5 \end{array}\right),\,$$

and so  $L_2 \not\leq C$ . In this particular case, we need to scale down  $T_2$  to

$$\left(\begin{array}{cc} 0.75 & 0\\ 0 & 0.75 \end{array}\right)$$

for the solution to be feasible.

Finally, load-balancing doesn't always help, particularly in small matrices when there aren't many paths to divert traffic away from congested links. And it is always useless to divert traffic to oneself. For example, consider the rate matrix

$$T_3 = \left(\begin{array}{cc} 0 & 0.5 + \epsilon \\ 0.5 & 0 \end{array}\right),$$

where  $\epsilon > 0$ . Sending traffic on the path  $1 \to 1 \to 2$  does not divert traffic from the congested link  $1 \to 2$ , therefore  $T_3$  is not feasible. This teaches us that when sending traffic from node *i* to node  $j \neq i$ , it is useless to use the link  $i \to i$ , because traffic is transferred across the network with no benefit. Comparing  $T_1$ ,  $T_2$  and  $T_3$ , this example also shows that finding the maximum throughput of a given rate matrix is not straightforward, even when N = 2. Moreover, since the number of cases to consider increases with N, such a problem is increasingly difficult to solve as N grows.

### **Problem Definition**

Our objective is to find the load-balanced network with the largest throughput guarantee. In other words, we want to find a network with a guaranteed throughput  $\theta^*$ , where  $\theta^*$  satisfies two properties. First, given any admissible arrival traffic, the network guarantees a throughput  $\theta^*$ , i.e. it will switch a fraction  $\theta^*$  of the traffic for any input-output flow. And second, no other network can have a better guaranteed throughput than  $\theta^*$ . We will define the problem by decomposing it into three successive optimization problems. First, we will find the throughput for a given network and a given rate matrix. Then, we will obtain the worst-case throughput of a network, which can be achieved for any rate matrix. Finally, we will provide  $\theta^*$ , which is the best guaranteed throughput among all networks.

In the first optimization, we want to find the maximum throughput for a given network and a given rate matrix. In other words, given capacity matrix C and rate matrix T, we want to find the best possible throughput  $\theta(C, T)$ , such that the scaleddown rate demand matrix  $\theta(C, T) \cdot T$  is feasible. Put mathematically,

$$\theta(C,T) \equiv \max_{\theta}(\theta)$$

, subject to:

(i)

$$\sum_{p=1}^{P(i,j)} T_{ij}^p = \theta \cdot T_{ij} \qquad \forall i, j$$

(ii)

$$L(i,j) \equiv \sum_{\{p:(i \to j) \in p\}} T_{ij}^p \le C_{ij} \quad \forall i, j$$

(iii)

$$T_{ij}^p \ge 0 \qquad \forall i, j, p$$

The throughput  $\theta(C, T)$  is the maximum of the set of throughputs  $\theta$  that satisfy three feasibility conditions. First, the arriving traffic is a scaled-down version of T by a factor  $\theta$ , such that it can be decomposed into several paths p. The second condition is that the sum of the loads of the paths must be less than C, i.e. that the load matrix is feasible. The last condition is that the rate on each path must be nonnegative.

The second optimization finds the guaranteed maximum throughput  $\theta(C)$  for the network. This is the throughput that is achievable by any rate matrix in the network, and therefore

$$\theta(C) \equiv \min_{T \text{ admissible}} (\theta(C, T)).$$

(2.3)

Finally, we find the maximum possible guaranteed throughput for any network, yielding a guaranteed throughput  $\theta^*$ , where

$$\theta^* \equiv \max_{\substack{C \text{ admissible}}} (\theta(C)). \tag{2.4}$$

## 2.2.3 Examples of Guaranteed Throughput

#### Guaranteed Throughput of the Uniform Mesh

The uniform mesh is an architecture in which all links have the same capacity, i.e.  $C_{ij} = 1/N$  for all i, j. We will show that the maximum guaranteed throughput of the uniform mesh is 50%.

We saw already in the Introduction why the uniform mesh guarantees at least 50% throughput, although the proof was based on slightly different assumptions. In short, each packet goes through both the load-balancing stage and the forwarding stage, and therefore through two hops. Consequently, the link between node i and node j can receive load in two possible ways. Either node i is sending some traffic to some node and spreads it using the intermediate node j, or some node sends traffic to node j and

spreads it using the intermediate node *i*. Mathematically,  $L_{ij} = \sum_k T_{ik} + \sum_k T_{kj} \le 2$  with an admissible *T*. Therefore,  $\theta(C) \ge 50\%$ .

Is it possible to do better using a different load-balanced routing algorithm? The following example shows that it is not.

Assume that

$$T = \begin{pmatrix} 0 & x & 0 & \dots & 0 \\ 0 & 0 & x & \ddots & \vdots \\ \vdots & & \ddots & \ddots & 0 \\ 0 & & 0 & x \\ x & 0 & \dots & 0 & 0 \end{pmatrix} = \sigma_{i \to (i+1) \mod N},$$

where  $x \ge 1/2$ , and the modulo function takes values in  $\{1, ..., N\}$  when nodes are numbered  $\{1, ..., N\}$ . A node *i* can send at most  $C_{i(i+1 \mod N)} = 1/N$  directly, and needs to send the remainder x - 1/N to load-balanced paths, each of these paths using at least two links. Hence, the total traffic load contributed by each node to the system is at least  $(1/N) + 2 \cdot (x - 1/N)$ , and the total traffic load contributed by the Nnodes is N(1/N + 2(x - 1/N)) = 2Nx - 1. As we saw earlier, diagonal elements don't help load-balancing, and with this rate matrix they are also useless for direct paths. Hence, the total useful traffic capacity is the sum of all non-diagonal elements of C, i.e.  $N \cdot (1 - 1/N) = N - 1$ . For the solution to be feasible, we need  $2Nx - 1 \le N - 1$ , which translates into  $x \le 1/2$ . And so there exists a traffic rate matrix that is only feasible with a throughput of at most 50%, hence  $\theta(C) \ge 50\%$ . Since we found that the two-hop algorithm provides a throughput of 50%,

$$\theta(C) = 50\%,\tag{2.5}$$

and it is not possible to improve on the two-hop algorithm.

#### Guaranteed Throughput of a Ring

As a second example, consider a network in which the nodes are connected in a uni-directional ring, i.e. node i is connected to node  $(i + 1) \mod N$ . Remember that we assumed that each packet needs to go at least once through the network. In the worst case, T is the identity matrix so that nodes only send traffic to themselves through the ring. Therefore all packets cross N links, and the throughput  $\theta(C_{ring}, T)$ is equal to 1/N. This T is the worst case, since packets do not need to use more than N links to reach their destination, and therefore

$$\theta(C_{ring}) = 1/N,\tag{2.6}$$

which - as expected - is much lower than for the uniform mesh.

### Guaranteed Throughput of a Permutation Matrix

The ring is a special case of a permutation matrix  $\sigma$  of the set  $\{1, ..., N\}$ , where  $\sigma$  is the capacity matrix of a network.  $\sigma$  can be represented as a 0-1 matrix with exactly one 1 in each row and column; i.e.  $\sigma_{ij} = 1$  if  $\sigma(i) = j$ , and  $\sigma_{ij} = 0$  otherwise. Since  $\sigma$  is a permutation, it can be decomposed as a product of disjoint cycles (the decomposition is unique up to the order of the cycles).

If  $\sigma$  can be written as a single cycle of length N, we can assume without loss of generality that  $\sigma(1) = 2$ ,  $\sigma(2) = 3,..., \sigma(N) = 1$ , and so  $\sigma$  is the capacity matrix of a ring, with  $\theta(\sigma) = 1/N$ .

Alternatively, if  $\sigma$  can be written as the product of two or more cycles, then there are two nodes *i* and *j* such that node *i* is in the first cycle and node *j* is in the second one. It is then impossible to reach node *j* from node *i* (the capacity graph is not connected), hence the throughput for any matrix *T* such that  $T_{ij} = 1$  is zero, and  $\theta(\sigma) = 0$ .

This example illustrates that the throughput of a capacity matrix is sensitive to its coefficients; and that the throughput of a disconnected graph is zero.

## 2.2.4 Properties of the Guaranteed Throughput

#### Concavity

With the examples above, we computed the throughputs of several capacity matrices, but found that it is not straightforward in general to compute throughput directly. Since we want to find the capacity matrix with the largest guaranteed throughput, we will use general properties of the throughput function. We'll start by showing that it is concave, scales linearly, and is strictly increasing, as defined below.

Let's show that throughput is concave. Assume that two capacity matrices  $C_1$  and  $C_2$  achieve throughputs of  $\theta(C_1, T)$  and  $\theta(C_2, T)$  for a rate matrix T. Then, applying the definition of throughput, for any  $\lambda \in [0, 1]$ , the matrix  $C = \lambda C_1 + (1 - \lambda)C_2$  will achieve a throughput of  $\theta(C, T) \geq \lambda \theta(C_1, T) + (1 - \lambda)\theta(C_2, T)$ . This can be seen by using the paths from  $C_1$  for a fraction  $\lambda$  of the traffic, and the paths from  $C_2$  for a fraction  $1 - \lambda$ . As a consequence, we also have  $\theta(C) \geq \lambda \theta(C_1) + (1 - \lambda)\theta(C_2)$ . This leads to the following proposition.

**Proposition 2** The guaranteed throughput function  $\theta(C)$  is concave in C.

#### Linear Scaling

Given any positive  $\lambda$ , we can find a feasible rate allocation for  $\lambda C$  from the rate allocation for C (and vice versa) by scaling the rate assigned to each path by a factor  $\lambda$  (respectively by  $\frac{1}{\lambda}$ ). Therefore, we get the following proposition:

**Proposition 3** The guaranteed throughput function  $\theta$  is linear with respect to scaling, *i.e.*

$$\theta(\lambda \cdot C) = \lambda \cdot \theta(C).$$

### Strictly Increasing

Clearly  $\theta$  is a non-decreasing function in the space of admissible capacity matrices. In other words, having more capacity cannot decrease the throughput. If  $C_1$  and  $C_2$  are two admissible capacity matrices, where  $C_1 \leq C_2$  (i.e. for all  $i, j, C_{1_{ij}} \leq C_{2_{ij}}$ , defining a partial order relation), then from the definition of  $\theta$ :  $\theta(C_1) \leq \theta(C_2)$ . Now, if  $C_1 < C_2$ , there exists  $\epsilon$  such that

$$C_2 \ge C_1 + \epsilon \cdot C_{\text{uniform}}$$

where  $C_{\text{uniform}}$  is the capacity matrix of the uniform mesh. Hence

$$\begin{aligned}

\theta(C_2) &\stackrel{(a)}{\geq} \quad \theta((1+\epsilon)(\frac{1}{1+\epsilon}C_1 + \frac{\epsilon}{1+\epsilon}C_{\text{uniform}})) \\

\stackrel{(b)}{\equiv} \quad (1+\epsilon) \cdot \theta(\frac{1}{1+\epsilon}C_1 + \frac{\epsilon}{1+\epsilon}C_{\text{uniform}})) \\

\stackrel{(c)}{\geq} \quad (1+\epsilon)(\frac{1}{1+\epsilon}\theta(C_1) + \frac{\epsilon}{1+\epsilon}\theta(C_{\text{uniform}})) \\

\stackrel{(d)}{\equiv} \quad (1+\epsilon)(\frac{1}{1+\epsilon}\theta(C_1) + \frac{\epsilon}{1+\epsilon}\frac{1}{2})) \\

&> \quad \theta(C_1),

\end{aligned}$$

where (a) uses the fact that  $\theta$  is non-decreasing, (b) uses the equality  $\theta(\lambda \cdot C) = \lambda \theta(C)$ , (c) uses the concavity of  $\theta$  and (d) uses the value of  $\theta(C_{\text{uniform}})$ .

**Proposition 4** The guaranteed throughput function  $\theta$  is strictly increasing, i.e. if  $C_1 < C_2$  then  $\theta(C_1) < \theta(C_2)$ .

## 2.2.5 The Biased Mesh

### Definition

We have already seen that the uniform mesh has a throughput of 50%, even though a node potentially spreads traffic over the useless links to itself. We can therefore expect a modified mesh - that doesn't spread to itself - to have higher throughput. This is indeed the case; in fact, it is the network with the highest guaranteed throughput.

In this modified mesh, a link from a node to itself is only used to send traffic directly, and not for spreading. However, a link from a node to another one is used for sending traffic directly as well as for spreading. Therefore, intuitively, a link from a node to another one should have twice as much capacity as a link from a node to itself, because it will be used for two functions instead of one. We'll call such a modified mesh the *biased mesh*. Its capacity matrix  $\hat{C}$  is

$$\hat{C} = \begin{pmatrix} c & 2c & \dots & 2c \\ 2c & c & \ddots & \vdots \\ \vdots & \ddots & \ddots & \ddots & \vdots \\ \vdots & & \ddots & c & 2c \\ 2c & \dots & 2c & c \end{pmatrix},$$

where c = 1/(2N - 1).

In the remainder (Propositions 6, 7 and 8), we will show that  $\hat{C}$  uniquely achieves the highest guaranteed throughput, using three consecutive steps. First, we will show that  $\hat{C}$  achieves a throughput of N/(2N-1). Then, we will prove that this is the largest achievable throughput for any network. Finally, we will demonstrate that the biased mesh is the only network to achieve this throughput.

#### Guaranteed Throughput of the Biased Mesh

Our first objective is to show that the guaranteed throughput of the biased mesh with the capacity matrix  $\hat{C}$  is at least N/(2N-1). Using the definition of the guaranteed throughput, we need to consider all admissible rate matrices T. The following proposition significantly restricts the number of rate matrices T we need to consider.

**Proposition 5** The guaranteed throughput  $\theta(C)$  defined in (2.3) can be found by considering the set of permutation matrices, i.e.,

$$\theta(C) = \min_{T \text{ permutation}} (\theta(C, T)).$$

(2.7)

*Proof:* For any admissible matrix T, there is at least one doubly stochastic matrix  $\overline{T}$  such that  $T \leq \overline{T}$  [84]. Clearly  $\theta(C, \overline{T}) \leq \theta(C, T)$ , and so we only need to consider the doubly stochastic rate matrices.

Birkhoff's theorem states that the set of doubly stochastic matrices is in the convex hull of the permutation matrices [12]. The result follows, using the definition of throughput.

Proposition 5 limits the set of rate matrices we need to consider to the set of permutation matrices. To show that the throughput of  $\hat{C}$  is at least N/(2N-1), we just need to show that a throughput of N/(2N-1) can be achieved for all the permutation matrices. It leads to the following proposition.

**Proposition 6** The guaranteed throughput of the biased mesh with capacity matrix  $\hat{C}$  is at least N/(2N-1).

*Proof:* Let's prove that  $\hat{C}$  achieves a throughput of N/(2N-1) when  $T = \sigma$ , with  $\sigma$  a permutation. Let c = 1/(2N-1). Consider a node *i*, and let's prove that *i* can always send at rate Nc to  $\sigma(i)$ . Our objective is to send directly as much flow as we can, and to uniformly load-balance the remainder among the non-diagonal elements. Distinguish among two cases: either  $\sigma(i) = i$  or  $\sigma(i) \neq i$ .

If  $\sigma(i) = i$ , node *i* needs to send *Nc* to itself. Therefore, it can send *c* directly to itself, and load-balance the remaining rate of (N-1)c among the other (N-1) nodes, then sending *c* to each node.

If  $\sigma(i) \neq i$ , node *i* needs to send *Nc* to node  $\sigma(i) \neq i$ . Therefore, it can send 2*c* directly to  $\sigma(i)$ , and load-balance the remaining rate of (N-2)c among the (N-2) nodes different from *i* and  $\sigma(i)$ , then sending *c* again to each node.

Let's examine the load on each link. Each diagonal element  $\hat{C}_{ii}$  only receives traffic if it is destined from node *i* to node *i*, and then it receives exactly *c*, its capacity.

Moreover, each non-diagonal element  $\hat{C}_{ij}$  can only receive traffic in two distinct cases, which can't happen at the same time. If  $j = \sigma(i)$ ,  $\hat{C}_{ij}$  receives exactly 2c, its capacity. Otherwise  $j \neq \sigma(i)$ , and  $\hat{C}_{ij}$  receives c from the load-balanced path  $i \to j \to \sigma(i)$ , and c from the load-balanced path  $\sigma^{-1}(j) \to i \to j$ , summing to 2c, its capacity.

Therefore the load on each link is always bounded by its capacity, hence this solution is feasible and the guaranteed throughput of  $\hat{C}$  is at least Nc = N/(2N-1).

#### 2.2.6 Optimality of the Biased Mesh

We just found that the biased mesh guarantees a throughput of at least  $\frac{N}{2N-1}$ . Is the biased mesh optimal, or could any capacity matrix guarantee a better throughput? The following proposition shows that the biased mesh achieves indeed the maximum possible guaranteed throughput for any possible admissible capacity matrix.

**Proposition 7** If the capacity matrix C is admissible, then the guaranteed throughput  $\theta(C) \leq \frac{N}{2N-1}$ .

The proof for Proposition 7 is in Appendix A.

## 2.2.7 Uniqueness of the Optimal Capacity Matrix

Since we proved that the biased mesh achieves the optimal throughput N/(2N-1), we will now demonstrate that it is the only capacity matrix to do so. This is done in Proposition 8, proved in Appendix B.

**Proposition 8** The only capacity matrix C that can achieve the optimal throughput N/(2N-1) is the capacity matrix  $\hat{C}$  of the biased mesh.

In conjunction with Propositions 6, 7 and 8, we have established therefore the following theorem.

**Theorem 9** The biased mesh satisfies these three properties:

- (i) The guaranteed throughput of the biased mesh is equal to  $\hat{\theta} = N/(2N-1)$ .

- (ii) The biased mesh achieves the maximum possible guaranteed throughput for any network, i.e.  $\theta(\hat{C}) = N/(2N-1)$ .

- (iii) The biased mesh is the only network to achieve this guaranteed throughput, i.e.  $\theta(C') < \theta(\hat{C})$  for any admissible capacity matrix  $C' \neq \hat{C}$ .

#### 2.2.8 Conclusions and Intuition

Theorem 9 shows that the biased mesh architecture achieves the best throughput among all possible architectures, and is the only one to do so. Therefore, it performs better than many alternative architectures, including the ring, torus and hypercube architectures.

However, this result assumes that if packets arrive to their destination after a single hop, they can immediately leave the switch. Therefore, the architecture will need to allow for one-hop as well as two-hop paths through the switch. This might prove difficult to implement, and might be a reason for a designer to prefer the uniform mesh. Using the fact that the uniform mesh achieves 50% throughput (Equation 2.5), we know that the uniform mesh is

$$\frac{\theta(\hat{C})}{\theta(C_{\text{uniform}})} = \frac{\frac{N}{2N-1}}{\frac{1}{2}} = \frac{1}{1 - \frac{1}{2N}} = 1 + o(1) - \text{optimal}$$

(2.8)

for its guaranteed throughput. Therefore, the load-balanced router with a uniform mesh is *asymptotically optimal*. Asymptotically with N, it guarantees at least as much throughput as any other fixed interconnection with an admissible capacity matrix. This is an additional argument in favor of the uniform mesh.

# Chapter 3

# Packet Reordering

The first two chapters introduced the load-balanced router and illustrated how it can be practically implemented using optics. In this chapter, we'll see how the load-balanced router can reorder packets. Packet reordering is a widespread property among load-balanced systems and can be detrimental to Internet traffic. Therefore, we will provide and analyze different possible algorithms to prevent packet reordering. We will finally focus on the FOFF algorithm, and prove that it prevents reordering as well as provides throughput and delay guarantees.

# 3.1 Presentation of Packet Reordering

#### 3.1.1 Example of Reordering in the Load-Balanced Router

Let's first define packet reordering. As defined in the Introduction, a flow is the set of all packets having the same input and output destination. Packet reordering occurs in a router when packets from a same flow depart from the router in an order different from the one in which they arrived.

Packet reordering could occur in a load-balanced router. This is because the load-balancer spreads packets as they arrive without regard to their final destination or departure time. Therefore, packets from the same flow can take different paths

Figure 3.1: Example of packet reordering in a load-balanced router

of different delays within the router. Consequently, as illustrated below, this loadbalancing among paths of different delays could incur packet reordering.

Figure 3.1 illustrates this possibility. In this example, all packets considered are destined to the output 1. By definition, in the first N time-slots, each input is connected to the first intermediate input exactly once. Assume that each input except the first one receives a packet and transfers it to the first intermediate input when they are connected together. After N time-slots, the first intermediate input will have received N - 1 packets from inputs 2, ..., N, and only one of these packets will have been serviced. Therefore, N - 2 packets are left in the first intermediate input then receives two packets back-to-back when it is successively connected to intermediate inputs 1 and 2. Therefore, the first input consecutively transfers these two packets to intermediate inputs 1 and 2 (packets from input 1 are represented as filled in Figure 3.1). Since the second packet is alone in its queue, while the first one has N - 2 packets in front of it, it is clear that the second packet will be serviced earlier, and therefore will also arrive to output 1 and leave the router earlier. Consequently, the two packets were *reordered*. They belong to the same flow, and the order in which

at

they arrived to the input is different from the order in which they  $\mathbf{x}_{\mathbf{k}}$  e leaving the output.

The example shows that reordering occurs when VOQs in different intermediate inputs and destined to the same output have different lengths. Due to the fixed-rate service, the amount of reordering depends on the difference between the lengths of the VOQs. For instance, assume that VOQs are modeled as having an infinite buffer capacity. Then, when a VOQ length increases while the other stays constant, the VOQ length difference grows unbounded, and therefore the possible amount of reordering also grows unbounded. Therefore, the load-balanced router does not provide any guarantee about the amount of reordering.

## 3.1.2 Consequences of Packet Reordering for Internet Traffic

The load-balanced router exhibits reordering - but is reordering really a problem?  $\leftarrow$  RFC 1812, the most common standard defining router requirements, does not forbid reordering in routers [8]. In addition, reordering is not uncommon in the Internet [10, 48]. Therefore, we might believe that reordering is not necessarily a problem.

However, in its current version, TCP (Transmission Control Protocol) does not perform well when out-of-order packets arrive to the destination. Out-of-order packets can be perceived as loss indicators, and trigger unnecessary retransmissions and TCP timeouts [13]. These retransmissions and timeouts cause a decrease in TCP throughput and an increase in packet delay. Consequently, since TCP traffic constitutes the vast majority of Internet traffic [35, 37], network operators generally insist that routers do not reorder packets belonging to the same application flow, i.e. sharing the same (source, destination) pair. Our goal in this chapter is to provide this guarantee. In particular, if we assume that all packets from an application flow take the same path in the Internet and therefore belong to the same router flow in the router, it is sufficient to guarantee that the router does not reorder packets belonging to the same router flow.

#### 3.1.3 Preventing Reordering

There are two methods of preventing packet reordering. The first method consists in *bounding the amount of reordering* and using a finite reordering buffer at the output. The second method is to make sure that *packets arrive in order* to the output, thus keeping packets in order throughout the router.

We saw in the example above that reordering can occur when VOQ lengths are different, and that the amount of reordering typically increases as the difference of VOQ lengths increases. Therefore, most of the algorithms that prevent reordering will try to bound or prevent any VOQ length difference. To do so, these algorithms will typically rely on a small input-stage coordination buffer, which spreads packets uniformly among the intermediate inputs.

In [21], the authors propose two schemes based on the first method of bounding reordering. Both schemes rely on algorithms found in the PPS (Parallel Packet Switch) router [44] and use a small input-stage coordination buffer. The first scheme, called FCFS (First Come First Served), uses a jitter control buffer in the intermediate inputs to ensure proper ordering of the traffic leaving the intermediate inputs. The second scheme, EDF (Earliest Deadline First), schedules packets according to their departure times in an ideal (output-buffered) router. However, both schemes do not seem practical. The jitter control mechanism in FCFS might require up to Nmemory-write accesses per time slot. And EDF needs to retrieve the packet with the smallest time stamp from a queue, making it hard to implement in a high performance router.

The second method of preventing reordering, which keeps packets ordered throughout the router, is used in [53] and [22]. [53] presents an algorithm that uses a coordination buffer in the input stage, and then queues packets in VOQs in the intermediate inputs based on their input, intermediate input, and output. Using this fine-grained queueing, the algorithm guarantees that packets arrive at the outputs in order. However, this algorithm requires a more complex queueing management system, and communication of state information between the intermediate inputs and the outputs. In [22], the authors introduce an algorithm in which the buffers in the intermediate inputs are finite and packets are guaranteed to leave the router in order. However, the algorithm assumes that in each frame period, arrivals of packets destined to a given output are constrained. While this might be satisfied in frame-based traffic such as SONET (Synchronous Optical Network) traffic, this property is not satisfied in general in the Internet.

Therefore, all these algorithms present significant problems in router implementations. Our objective is to find a different scheme in order to guarantee that packets leave the router in order. We will first consider Application Flow-Based Routing (AFBR) and Uniform Frame Spreading (UFS), two algorithms that attempt to maintain packets ordered throughout the router. Then, we will present Full Ordered Frames First (FOFF), an algorithm that bounds reordering, and we will prove that FOFF also provides throughput and delay guarantees.

# **3.2** Application Flow-Based Routing (AFBR)

#### 3.2.1 How AFBR Works

We saw above that reordering is due to the uncontrolled use of parallelism in the load-balanced router. Reordering occurs when packets from the same router flow, and in particular from the same application flow, take different paths with different delays. Therefore, a simple idea is to make all packets from the same application flow take the same path inside the router. We will call this an *Application Flow-Based Routing* (AFBR).

AFBR can be implemented by hashing packet header fields (e.g., source and destination IP addresses and protocol identification) into N different hash values. Packets from the same application flow will return the same hash value. Then, all packets having the same hash value will be transferred by a given input to the same intermediate input. Therefore, all packets from the same application flow take the same path inside the router. Consequently, AFBR prevents reordering throughout the router for packets from the same application flow.

Note that hashing flows is common in load-balanced systems. It is used for example in backbone links [15], address lookups [14, 47], packet processing [16], web

servers [68, 69], network processors [32, 50] and flow demultiplexing [33].

#### 3.2.2 Properties of AFBR