## **ON-CHIP WIRES: SCALING AND EFFICIENCY**

A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

> Ron Ho August 2003

© Copyright by Ron Ho 2003 All Rights Reserved I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

> Mark A. Horowitz (Principal Adviser)

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

Bruce A. Wooley

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

Krishna C. Saraswat

Approved for the University Committee on Graduate Studies:

## Abstract

Recent years have seen an increase in the importance of on-chip wires, as they have slowed down and gates have sped up. This dissertation takes a close look at the story of wire scaling. It forecasts wire and gate characteristics from the Semiconductor Industry Association roadmap and combines them into performance metrics, showing how the ratio of wire delays to gate delays scales slowly for scaled-length wires and grows rapidly for fixed-length wires.

This duality of "fast local wires" contrasted with "slow global wires" affects how we approach VLSI designs. First, CAD place-and-route tools must improve to keep up with growing die complexity and more local blocks gathered on a chip. Second, modular architectures can effectively exploit the dual nature of wires, using wide global buses of high bandwidth to offset long wire latencies.

Using such wide and long global buses can burn a great deal of power, especially if built with traditional delay-optimal CMOS repeaters. Traditional repeaters can be sized and spaced to save about 30% in energy for only a 10% delay penalty. Because this 30% of energy savings is not a lot, techniques for running global wires at a reduced voltage can be very important. These include NMOS drivers, overdrive pre-emphasis, and voltage pre-equalization. Using these circuit techniques offers an order-of-magnitude in energy savings for no effective slowdown. Experimental results on a 180nm testchip validate this 10x savings in energy over 10mm long on-chip buses, running at 1 token per 10 gate delays. Further experimental data shows receiver input offsets under 90mV, with input offset compensation leading to residual input uncertainties of around 15mV.

## Acknowledgements

The title page of this doctoral thesis lists my name as the single author, although that is a deception. The ideas and concepts in the pages that follow arose from the work of many people, and to them I owe my thanks.

Mark Horowitz has done his best to teach me how to do research these past several years. His ability to see right through problems to solutions, his patience with recalcitrant graduate students, and his constant and easy availability made him a wonderful advisor. I thank him for taking me on as a graduate student so many years ago.

Bruce Wooley and Krishna Saraswat agreed to be my associate advisor and third reader, respectively, and I appreciate their assistance and input to my research and dissertation. Nick Bambos very graciously agreed to chair my defense committee.

The staff at Stanford has been helpful, knowledgable, and supportive, as needed. Charlie Orgish and Joe Little have taught me more than I can remember about computers and how to set up a computing infrastructure. Darlene Hadding, Terry West, Deborah Harber, Lindsay Brustin, and Taru Fisher all helped me navigate the maze of Stanford administration.

My long tenure in the research group meant that I've had the pleasure of working with many of Mark's graduate students. Ken Mai bore the brunt of my idea-bouncing, as my most frequent collaborator, and I learned a great deal from him. I also spent time building chips with Dan Weinlader and teaching chip-building with Gu-Yeon Wei, both enjoyable experiences. Ken Yang, Stefanos Sidiropoulus, Jeff Solomon, Hema Kapadia, and Birdy Amrutur all enriched my Stanford career through various projects and papers. I owe my officemates David Harris, Evelina Yeung, and Vicky Wong special mention, for putting up with me over the years. Although my colleages at Intel more often than not tried to convince me to "give up that Ph.D. pipe dream and come back full-time," I owe much to them, especially Jason Stinson, Branko Perazich, Ron Zinger, and Mehrdad Mohebbi. Over the past ten years, their friendship, knowledge in designing CPUs, and, of course, willingness to employ me were all invaluable to my parallel career in graduate school. My current colleagues at Sun, Robert Drost and Ivan Sutherland, have greatly encouraged these final steps towards completion.

My sister Minnie and her husband Rohit both served as existence proofs for the obtainability of a Stanford engineering doctorate. My parents, long before graduate school and long before Stanford, taught me how to think and how to be curious about how and why things worked. They started me on this path, and I'm grateful that they did.

But above all and most importantly, my wife Christina showed unflagging support, optimism, and patience. Without her help I would never have finished this work, and so I humbly dedicate it to her.

# Contents

| Al | Abstract v |          |                                          |      |  |

|----|------------|----------|------------------------------------------|------|--|

| Ac | know       | ledgem   | ents                                     | vii  |  |

| 1  | Intr       | oductio  | n                                        | 1    |  |

|    | 1.1        | Organi   | zation                                   | . 3  |  |

| 2  | Met        | rics, mo | odels, and scaling                       | 4    |  |

|    | 2.1        | A simp   | ple gate delay model                     | . 4  |  |

|    | 2.2        | Wire c   | haracteristics                           | . 5  |  |

|    |            | 2.2.1    | Resistance                               | . 6  |  |

|    |            | 2.2.2    | Capacitance                              | . 8  |  |

|    |            | 2.2.3    | Inductance                               | . 10 |  |

|    | 2.3        | Wire p   | erformance metrics                       | . 13 |  |

|    |            | 2.3.1    | Signal coupling                          | . 13 |  |

|    |            | 2.3.2    | Wire delay                               | . 17 |  |

|    |            | 2.3.3    | Repeaters                                | . 21 |  |

|    | 2.4        | Gate m   | netrics under scaling                    | . 22 |  |

|    | 2.5        | Wire c   | haracteristics under scaling             | . 24 |  |

|    |            | 2.5.1    | Resistance under scaling                 | . 26 |  |

|    |            | 2.5.2    | Capacitance and inductance under scaling | . 26 |  |

|    |            | 2.5.3    | Noise as a limiter to scaling            | . 29 |  |

|    |            | 2.5.4    | Noise minimization techniques            | . 29 |  |

|    | 2.6        | Wire p   | erformance under scaling                 | . 32 |  |

|   | 2.7   | Summ     | ary                                    | 36 |

|---|-------|----------|----------------------------------------|----|

| 3 | Imp   | lication | is of Scaling                          | 37 |

|   | 3.1   | Desig    | n at the ground level: CAD tools       | 38 |

|   |       | 3.1.1    | Claim: CAD tools need not improve      | 38 |

|   |       | 3.1.2    | Underlying problem in synthesis        | 40 |

|   |       | 3.1.3    | Wire exceptions                        | 41 |

|   | 3.2   | Design   | n at 50,000 feet: Architectures        | 46 |

|   |       | 3.2.1    | A historical perspective               | 47 |

|   |       | 3.2.2    | On-die signal range                    | 49 |

|   |       | 3.2.3    | Wire-aware architectures: modularity   | 51 |

|   | 3.3   | Efficie  | ent global wiring networks             | 55 |

|   | 3.4   | Summ     | ary                                    | 56 |

| 4 | Effic | cient Re | epeaters                               | 57 |

|   | 4.1   | Codin    | g for energy savings                   | 57 |

|   | 4.2   | CMOS     | S repeaters                            | 61 |

|   |       | 4.2.1    | Optimizing for delay                   | 61 |

|   |       | 4.2.2    | Optimizing for energy-delay product    | 64 |

|   |       | 4.2.3    | Other constraints and metrics          | 66 |

|   | 4.3   | Genera   | al repeater models                     | 68 |

|   |       | 4.3.1    | Delay and energy for the general model | 70 |

|   | 4.4   | Exam     | ples of repeater optimizations         | 71 |

|   |       | 4.4.1    | Example: Buffers                       | 71 |

|   |       | 4.4.2    | Example 2: Tristates                   | 74 |

|   | 4.5   | Summ     | ary                                    | 78 |

| 5 | Low   | -Swing   | Repeaters                              | 80 |

|   | 5.1   | Benefi   | its and costs of low-swing signaling   | 80 |

|   | 5.2   |          | wing repeater systems                  | 83 |

|   |       | 5.2.1    | Low-swing transmitter circuits         |    |

|   |       | 5.2.2    | Wire engineering                       |    |

|   |       |          |                                        |    |

|    |                  | 5.2.3    | Low-swing receivers                    | . 97  |

|----|------------------|----------|----------------------------------------|-------|

|    | 5.3              | Putting  | g it all together                      | . 104 |

| 6  | Exp              | eriment  | al Results                             | 105   |

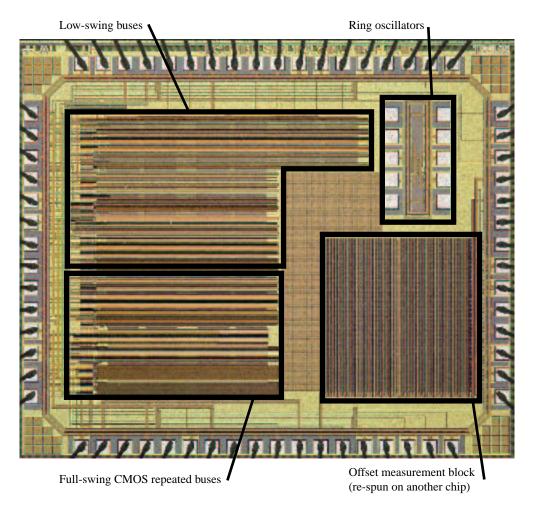

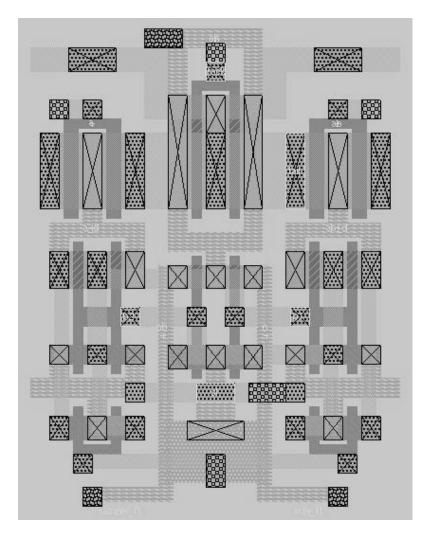

|    | 6.1              | Testch   | ip overview                            | . 105 |

|    | 6.2              | Bus ex   | periments                              | . 108 |

|    |                  | 6.2.1    | Overhead                               | . 109 |

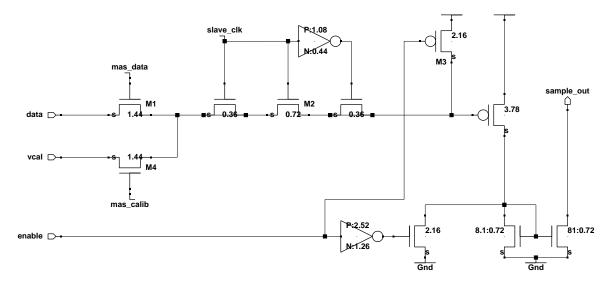

|    |                  | 6.2.2    | Measurement circuits                   | . 110 |

|    |                  | 6.2.3    | Performance and results                | . 112 |

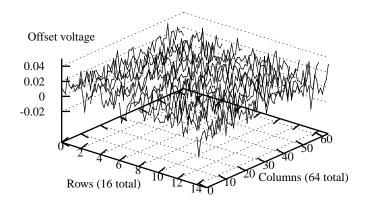

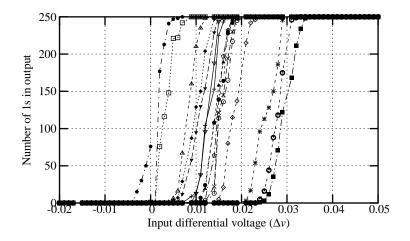

|    | 6.3              | Offset   | experiments                            | . 118 |

|    |                  | 6.3.1    | Offset measurements                    | . 118 |

|    |                  | 6.3.2    | Systematic errors                      | . 121 |

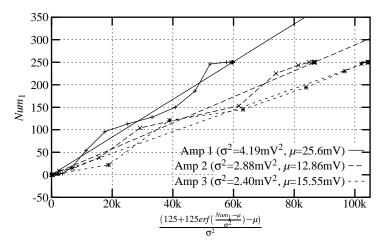

|    |                  | 6.3.3    | Residual offsets after compensation    | . 123 |

|    |                  | 6.3.4    | Offset experiments we wish we had done | . 126 |

|    | 6.4              | Summ     | ary                                    | . 126 |

| 7  | Con              | clusions | 5                                      | 128   |

| A  | Fano             | out in a | buffered repeater                      | 131   |

| Bi | Bibliography 134 |          |                                        |       |

# **List of Tables**

| 2.1        | Sample $\frac{1}{2}R_{wire}C_{wire}$ delays, 0.18- $\mu$ m technology                     | 19  |

|------------|-------------------------------------------------------------------------------------------|-----|

| 2.2        | Wire pitch dimensions for an Intel 0.18- $\mu$ m technology [36]                          | 24  |

| 2.3        | Aggressive wire predictions, technology terms only                                        | 25  |

| 2.4        | Conservative wire predictions, technology terms only                                      | 26  |

| 2.5        | Resistance, in $\Omega/\mu$ m, with technology scaling                                    | 27  |

| 2.6        | Capacitance, in fF/ $\mu$ m, with technology scaling $\ldots \ldots \ldots \ldots \ldots$ | 28  |

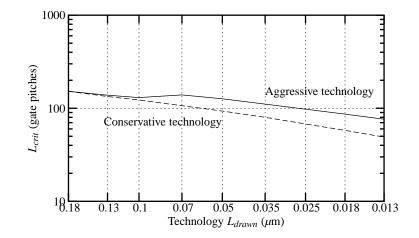

| 3.1<br>3.2 | $L_{crit}$ in gate pitches, with technology scaling                                       |     |

| 4.1        | Savings from using bus-invert                                                             | 59  |

| 4.2        | Minimal energy delay, under risetime constraints                                          | 68  |

| 4.3        | Buffer minimal energy delay, under risetime constraints                                   | 74  |

| 4.4        | Minimal energy delay, under risetime constraints                                          | 77  |

| 5.1        | Estimated improvements to receiver sizing                                                 | 102 |

# **List of Figures**

| 1.1  | The view of the future, circa 1997                                           | 2  |  |  |

|------|------------------------------------------------------------------------------|----|--|--|

| 2.1  | A fanout-of-four inverter delay                                              | 5  |  |  |

| 2.2  | Drawn to relative scale: A $0.25$ - $\mu$ m aluminum interconnect technology |    |  |  |

|      | (left) and a 0.13- $\mu$ m copper interconnect technology (right)            | 6  |  |  |

| 2.3  | A simple resistance model                                                    | 7  |  |  |

| 2.4  | A simple capacitance model                                                   | 9  |  |  |

| 2.5  | A signal wire <i>ab</i> and two potential returns <i>cd</i> and <i>ef</i>    | 11 |  |  |

| 2.6  | Partial loops for the three wires                                            | 11 |  |  |

| 2.7  | Bus coupling noise model                                                     | 15 |  |  |

| 2.8  | Decomposition of attacker and victim waveforms                               | 15 |  |  |

| 2.9  | Idealized wave-pipeline with 1-, 2-, and 3- $\tau$ repeat rates              | 20 |  |  |

| 2.10 | Unrepeated bandwidth, in an 0.18- $\mu$ m technology                         | 21 |  |  |

| 2.11 | FO4 scaling at TTLH (90% $V_{dd}$ , 125 degrees)                             | 23 |  |  |

| 2.12 | Resistance scaling, optimisitic and pessimistic trend curves                 | 27 |  |  |

| 2.13 | Capacitance scaling, optimisitic and pessimistic trend curves                | 28 |  |  |

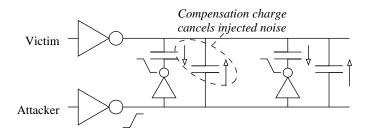

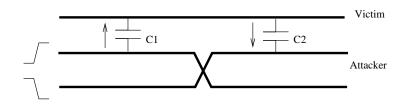

| 2.14 | Staggering repeaters minimizes injected noise                                | 30 |  |  |

| 2.15 | Charge compensation devices inject "negative" noise                          | 30 |  |  |

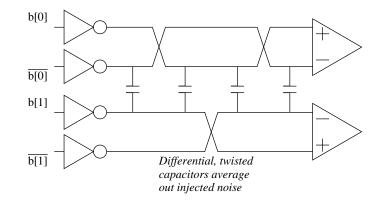

| 2.16 | Twisted differential wires effectively eliminate noise                       | 31 |  |  |

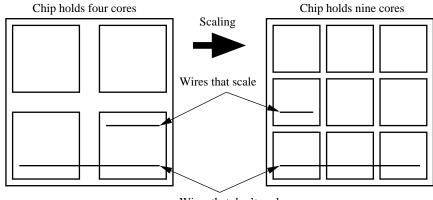

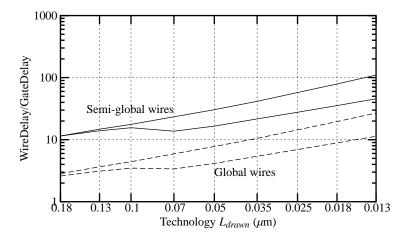

| 2.17 | Two kinds of wire on a chip: local and global                                | 32 |  |  |

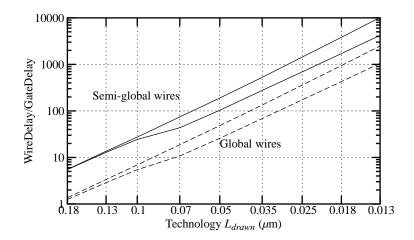

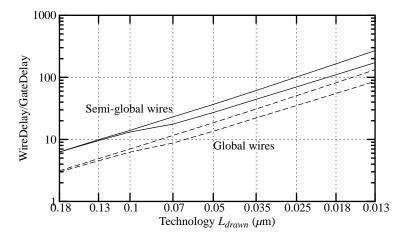

| 2.18 | Local unrepeated wires, spanning 800 standard cells: 10x penalty over nine   |    |  |  |

|      | generations. The lines indicate optimistic and pessimistic scaling trends    | 33 |  |  |

| 2.19 | Global unrepeated wires, spanning 5mm: 2000x penalty over nine genera-       |    |  |  |

|      | tions. The lines indicate optimistic and pessimistic scaling trends          | 34 |  |  |

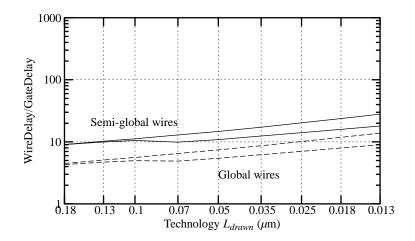

|      |                                                                              |    |  |  |

| 2.20 | Global repeated wires, spanning 5mm: 40x penalty over nine generations . 34      |    |  |

|------|----------------------------------------------------------------------------------|----|--|

| 2.21 | Local repeated wires, spanning 800 standard cells: 2-3x penalty over nine        |    |  |

|      | generations                                                                      | 35 |  |

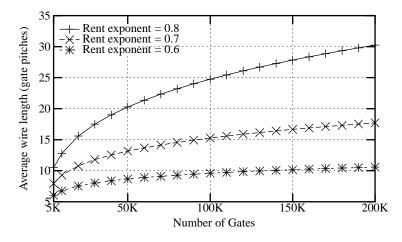

| 3.1  | Average wire length versus gate count                                            | 39 |  |

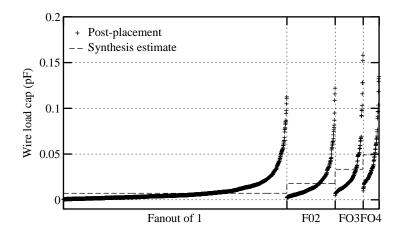

| 3.2  | Estimated versus actual wire loads                                               | 41 |  |

| 3.3  | $L_{crit}$ scaling                                                               | 43 |  |

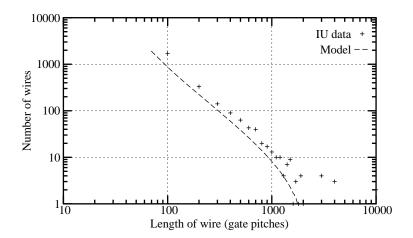

| 3.4  | M-Machine IU unit versus model (k=3, p=0.7, f=2.3)                               | 43 |  |

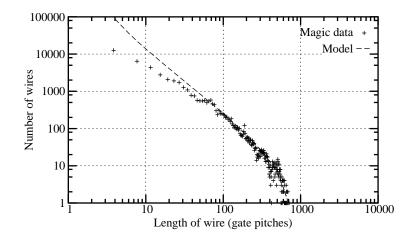

| 3.5  | Flash MAGIC node versus model (k=3, p=0.7, f=2.5)                                | 44 |  |

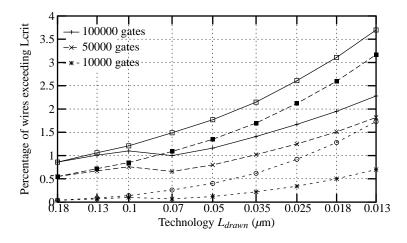

| 3.6  | Percentage of wires that exceed $L_{crit}$ under scaling. The two sets of curves |    |  |

|      | show optimistic and pessimistic technology scaling trends                        | 44 |  |

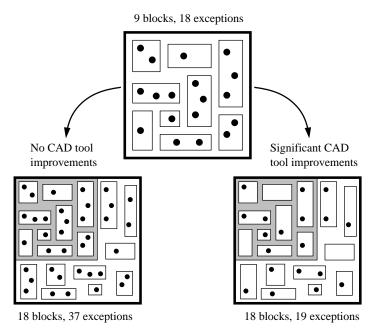

| 3.7  | Wire exceptions under scaling                                                    | 45 |  |

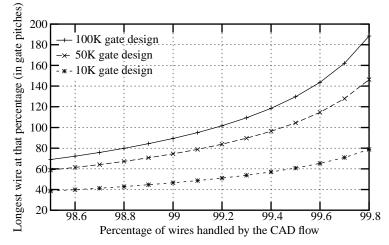

| 3.8  | CAD tools handling more wires must also handle <i>longer</i> wires               | 46 |  |

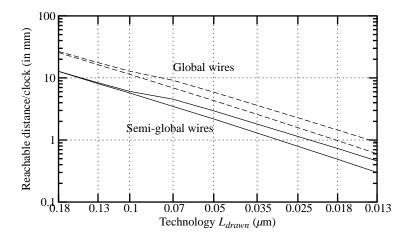

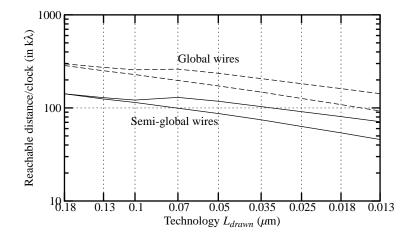

| 3.9  | Reachable distance per 16 FO4 clock, in mm                                       | 50 |  |

| 3.10 | Reachable distance per 16 <i>FO4</i> clock, in $k\lambda$                        | 51 |  |

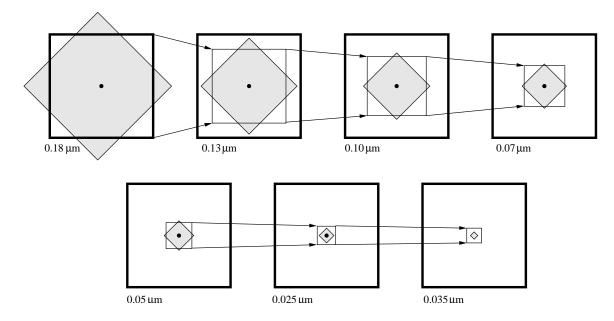

| 3.11 | Reachable distance on a chip under scaling                                       | 52 |  |

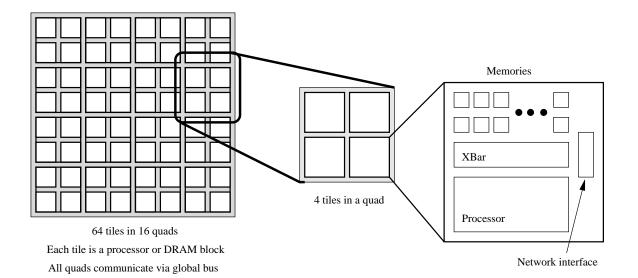

| 3.12 | Smart Memories project                                                           | 53 |  |

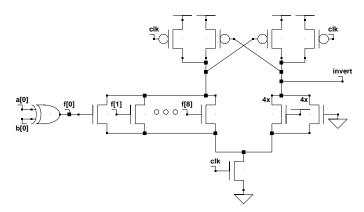

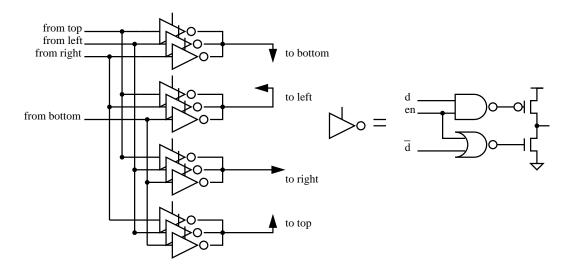

| 4.1  | Bus-invert transmission logic                                                    | 59 |  |

| 4.2  | Simple model using inverters                                                     | 61 |  |

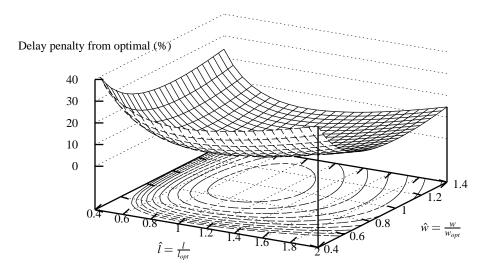

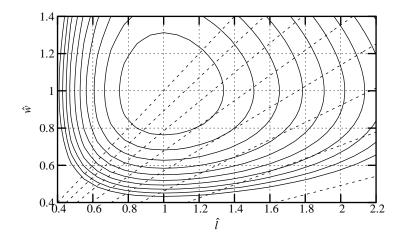

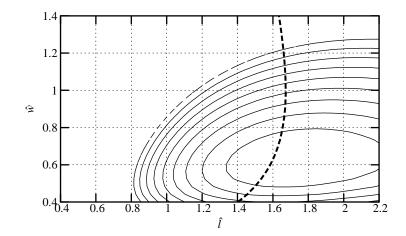

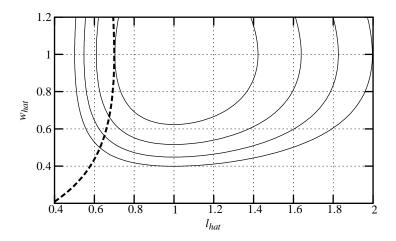

| 4.3  | Delay sensitivity (2% contours)                                                  | 63 |  |

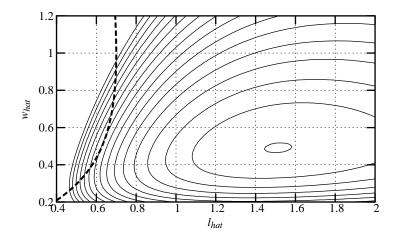

| 4.4  | 2% delay contours (solid lines) and 5% energy contours (dashed lines).           |    |  |

|      | Energy increases towards the upper left direction.                               | 65 |  |

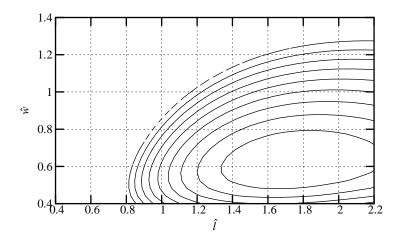

| 4.5  | 2% contours for energy delay optimization                                        | 65 |  |

| 4.6  | 2% contours for energy-delay optimization with risetime constraint               | 67 |  |

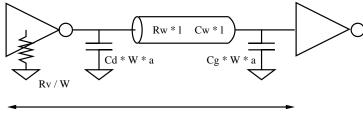

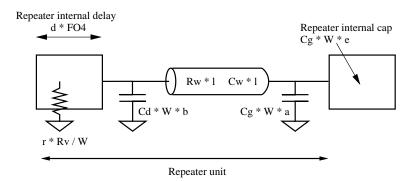

| 4.7  | General repeater model                                                           | 69 |  |

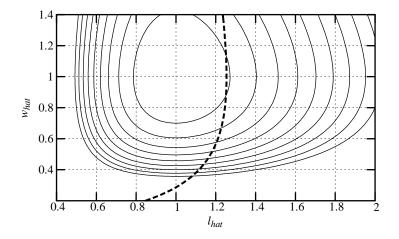

| 4.8  | Delay sensitivity (2% contours) with rise-time constraint (dashed line)          | 73 |  |

| 4.9  | Energy delay sensitivity (2% contours) with rise-time constraint (dashed line)   | 73 |  |

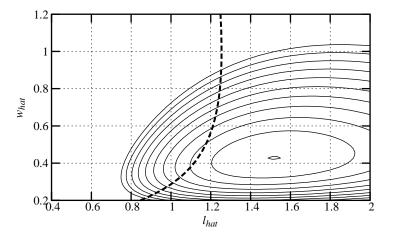

| 4.10 | Simple model using tristate repeaters                                            | 75 |  |

| 4.11 | Delay sensitivity (4% contours) with rise-time constraint (dashed line)          | 77 |  |

| 4.12 | Delay-Energy 4% contours with rise-time constraint (dashed line)                 | 78 |  |

|      |                                                                                  |    |  |

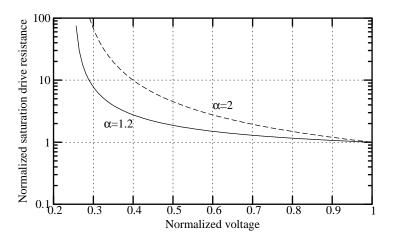

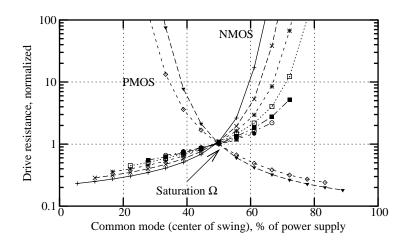

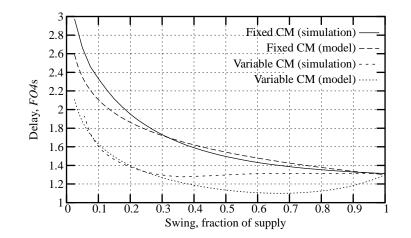

| 5.1  | Drive resistance versus power supply, for $V_t = \frac{1}{4}V_{dd}$                         |

|------|---------------------------------------------------------------------------------------------|

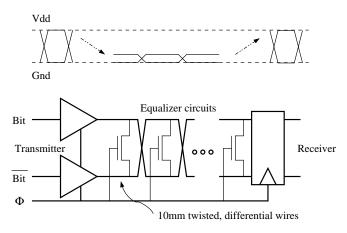

| 5.2  | Generic low-swing repeated wire                                                             |

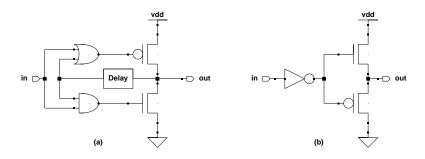

| 5.3  | Cutoff drivers. (a) Logical cutoff. (b) Self-cutoff                                         |

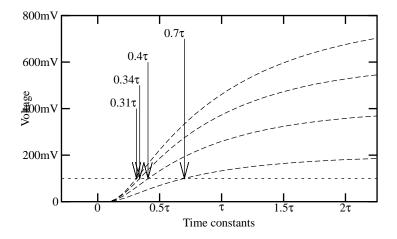

| 5.4  | Overdrive transmitter benefits                                                              |

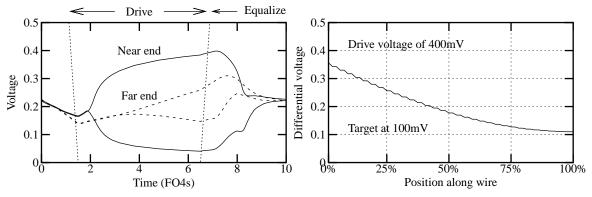

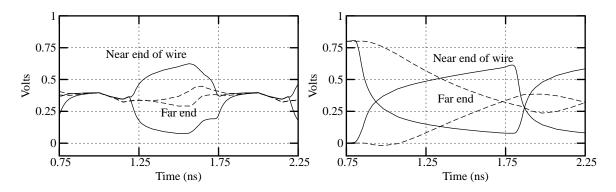

| 5.5  | (a) Simulation of wire split at receiver end and (b) Wire differential voltage              |

|      | profile at t=6.4 <i>FO4</i>                                                                 |

| 5.6  | Equalized versus non-equalized drivers                                                      |

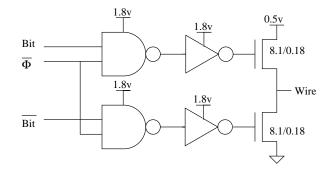

| 5.7  | Transmitter, one of a pair, sized for a 0.18- $\mu$ m technology 91                         |

| 5.8  | Driver resistance in a MOSIS $0.18$ - $\mu$ m technology                                    |

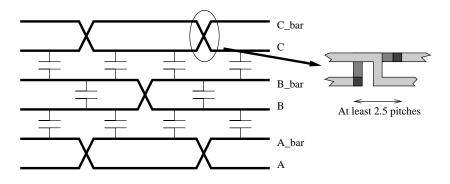

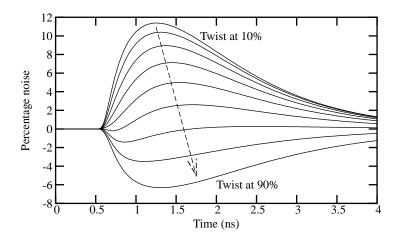

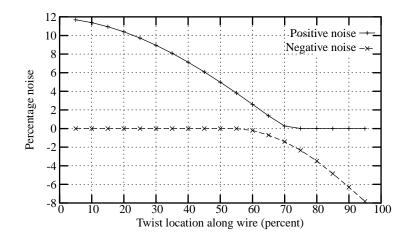

| 5.9  | A typical twist solution                                                                    |

| 5.10 | Optimized twisting would put the twist at 70% down the wire                                 |

| 5.11 | Simulated noise, 5mm wires, $100\Omega$ and $50\Omega$ drive resistances $\ldots \ldots 95$ |

| 5.12 | Peak of simulated noise, with optimal around 70%                                            |

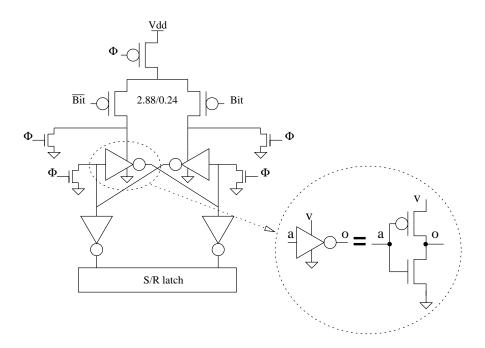

| 5.13 | Receiver amplifier, in 0.18- $\mu$ m technology                                             |

| 5.14 | Sense amplifier delays                                                                      |

| 6.1  | Chip photomicrograph                                                                        |

| 6.2  | Master-slave variant of on-die sampler circuit, sized for a $0.18-\mu$ technology 110       |

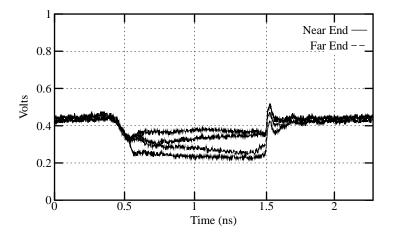

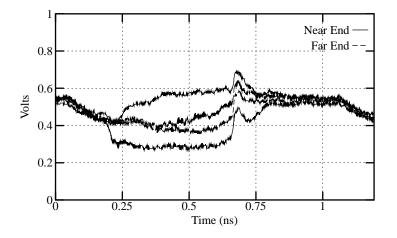

| 6.3  | Low-swing bus at 500MHz                                                                     |

| 6.4  | Low-swing bus at 1GHz                                                                       |

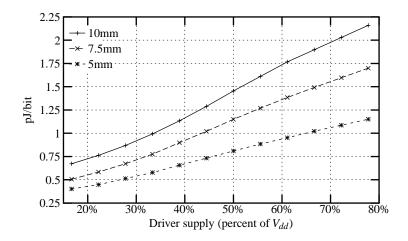

| 6.5  | Measured energy consumption of low-swing bus at 500MHz. Full-swing                          |

|      | bus had measured energy consumption of 9.84pJ/bit                                           |

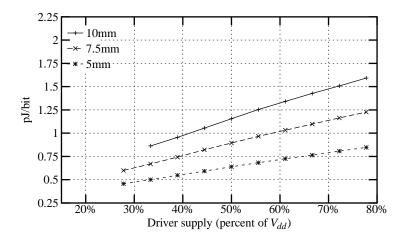

| 6.6  | Measured energy consumption of low-swing bus at 1GHz. Full-swing bus                        |

|      | had measured energy consumption of 9.84pJ/bit                                               |

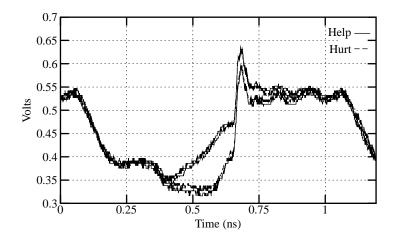

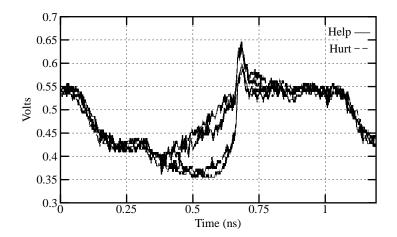

| 6.7  | Fully-twisted wire: no difference between "help" or "hurt"                                  |

| 6.8  | Untwisted wire: a difference between "help" and "hurt"                                      |

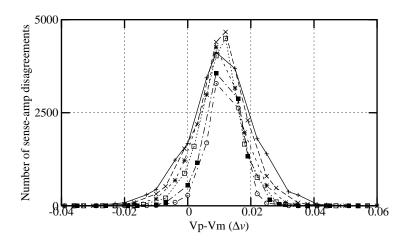

| 6.9  | Measured scan-chain disagreements. The x-axis is $\Delta v$ and the different               |

|      | curves are for $v_{cm}$ ranging from 0.1V to 1.1V (higher $v_{cm}$ towards the center).119  |

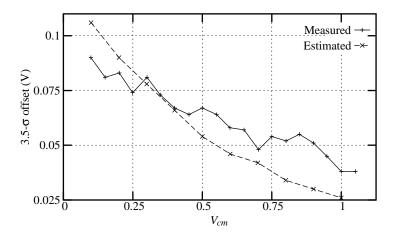

| 6.10 | Measured offsets versus common-mode voltage                                                 |

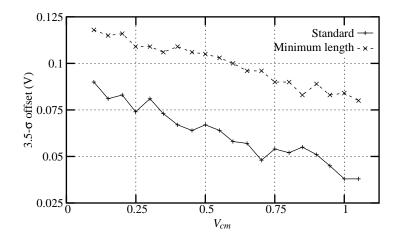

|      | Measured offset of minimum channel length amplifiers                                        |

|      | Measured offsets in their physical locations (in volts)                                     |

| 6.13 | Sense amplifier                                           | 22 |

|------|-----------------------------------------------------------|----|

| 6.14 | Residual noise error distributions                        | 24 |

| 6.15 | Matching the residual noise to an error function          | 25 |

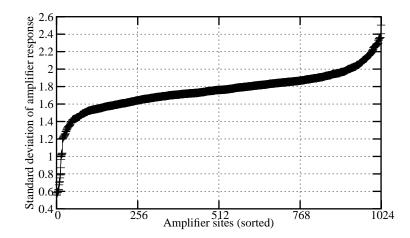

| 6.16 | Standard deviations across the entire array of amplifiers | 25 |

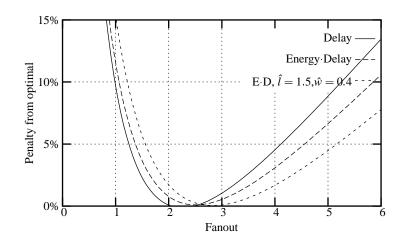

| A.1  | Delay and Energy Delay vs. buffer internal fanout         | 33 |

## **Chapter 1**

## Introduction

The importance of on-chip wires has dramatically risen over the past decade. Prior to the early 1990s, chip designers could treat on-chip wires as purely capacitive loads of logic gates; these wires had no intrinsic delays of their own. As technologies scaled into the mid-1990s, growing wire resistance coupled with shrinking native gate speeds made wire delays increasingly important. For example, the principal and enduring speedpath on the PentiumPro/II/III architectures at Intel, designed in the early-to-mid 1990s, was a long write-back bus whose wire length spanned much of the chip.

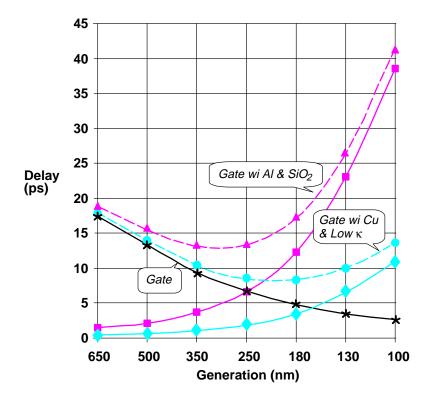

About this time, a now-famous graph projected wire and gate delays into what was then the distant semiconductor future (see Figure 1.1). James Meindl noted wryly that this graph, based on an early study from the 1980's [1], should have been designated the logo of the Semiconductor Research Corporation, so often was it invoked at industry meetings [2]. It showed a clear divergence between gate delays and wire delays, and the use of copper rather than aluminum only delayed the eventual cross-over. This graph raised more questions than it answered, such as how long were the wires, what kind of gates could run so fast, and whether speed-up technologies like repeaters were used. Regardless, it conveyed its point clearly: like it or not, wires are getting slower as gates are getting faster.

The seemingly inexorable divergence between improving gate delays and degrading wire delays seems to paint a bleak future for chip designers. But does it? After all, the industry continues to produce more and more chips of enormous complexity, with designers

Figure 1.1: The view of the future, circa 1997

constantly creating new architectures and circuits for ever-increasing performance. Chip builders, it seems, must know things that Figure 1.1 does not express.

This dissertation takes a close look at the story of wire scaling: how do wires perform now, and how will they perform in the future? What are designers doing today and what will they do tomorrow? As we shall see, managing wire delay as technology scales is important, but doing so in an energy-efficient manner is just as critical.

### 1.1 Organization

To understand the effects of technology scaling on on-chip wires we must first decide what wire metrics are important. Chapter 2 describes models of wire and gate delays. These models allow us to project the wire and gate delays in future technologies. Notice that only their *relative* performance matters. If gate delays and wire delays changed identically, either dramatically or even not at all, then the overall system design would still be balanced, and neither gates nor wires would individually limit overall performance.

Chapter 3 takes the results from Chapter 2 and looks at the implications of such scaling trends. Although wire scaling affects the entire VLSI design space, I limit my attention to two areas in particular: CAD tools and their ability to automate design, and computer architectures and how they can leverage or exploit the scaled characteristics of wires. In discussing these latter architectural implications of scaling, I will consider long on-chip wires and how energy efficiency on these wires will become an important design constraint.

Figuring out how to drive long wires is not a new problem. A number of solutions using optimally-repeated CMOS repeaters are well-known. However, the problem of driving these wires efficiently is rarely considered. Being stingy with delay typically means spending extravagently in power, and repeaters with slightly sub-optimal delays can offer potentially large energy savings. Chapter 4 examines these tradeoffs.

Tweaking repeater sizing and placement can buy only limited energy savings. Chapter 5 departs from the full-swing CMOS repeater discussion to consider low-swing circuit architectures. It discusses design issues related to low-swing drivers, receivers, and the wires themselves. Chapter 6 follows and gives results from testchip experiments.

## **Chapter 2**

## Metrics, models, and scaling

In order to lay a consistent foundation for the following sections, this chapter considers how to model the delays of wires and gates. A contemporary  $0.18 - \mu m$  technology will provide a framework for our discussion of gate and wire delays. Gates will use a delay metric called an *FO4*, which is based on feature size and described below; wires will use simple cross-sectional-area-based models for resistance and capacitance that lead to correspondingly simple wire delay metrics. These measures of gate and wire performance can help project trends of wire delays relative to gate delays, including side effects such as noise. As technologies scale, some wires scale in length and others do not, and we can apply our metrics to both of these types of wires. As we shall see, the scaled-length wires do trend with gate delays, but the fixed-length wires do not.

### 2.1 A simple gate delay model

Transistors are very complicated devices that can be connected in a myriad of ways, so characterizing gate performance in a way that facilitates comparisons to wires initially appears difficult. However, for reasons of productivity, CAD tool support, and robust behavior, VLSI designers use transistors in only a very limited set of topologies; static and simple dynamic CMOS gates dominate digital designs. As a result, metrics that characterize the performance of these gates will suffice.

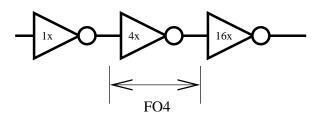

To measure gate speed, we use the delay through an inverter driving four identical

Figure 2.1: A fanout-of-four inverter delay

copies of itself, shown in Figure 2.11. This is called a "fanout-of-four inverter delay," or simply an *FO4*. In our benchmark 0.18- $\mu$ m technology, an *FO4* is 90ps.

Combinational delays, composed of many different static and dynamic CMOS gate delays, can be normalized to this *FO4*. The resulting relative delay holds constant over a wide range of process technologies, temperatures, and voltages. We can therefore treat the *FO4* as our proxy for CMOS gate delays: to understand how gates compare with wires, we need estimate the delay of only a single loaded inverter.

*FO4* delays are generally constant for a given feature size; that is, one company's 180nm technology will produce an *FO4* delay reasonably close to another company's 180nm technology. This simplifies estimating *FO4*s. However, specialized in-house technologies (such as those from Intel or IBM) typically offer 30-50% faster *FO4* delays due to highly optimized—and expensive—gate engineering. We will discuss this further in Section 2.4.

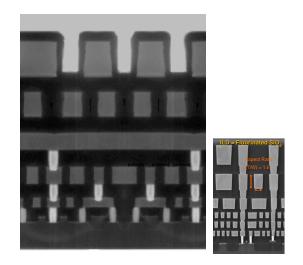

### 2.2 Wire characteristics

Two generations of Intel process technologies, shown as cross-sectional photographs in Figure 2.2, reflect advances in on-chip wiring. A 0.25- $\mu$ m technology from 1997, the vehicle for 700MHz Pentium III processors, used five layers of aluminum metal, with shiny tungsten plugs connecting them [3]. A 0.13- $\mu$ m technology from 2002, the vehicle for 3GHz Pentium 4 processors, uses six layers of copper metal with copper vias [4]. Between these two technologies, spanning three generations, the wires' cross-sectional areas and spacings fell dramatically. The importance of cross-sectional area and spacing lies in their effects on the wire electrical characteristics that we care about: resistance and capacitance.

Figure 2.2: Drawn to relative scale: A  $0.25-\mu m$  aluminum interconnect technology (left) and a  $0.13-\mu m$  copper interconnect technology (right)

For the forseeable future, resistance and capacitance will determine wire delay and noise behavior. The following sections describe geometric models for resistance and capacitance that are based on cross-sectional area and spacing. The simplicity of these models does not preclude them from including many of the non-idealities of real wires. We will also discuss wire inductance and why we can ignore its role in performance modeling.

### 2.2.1 Resistance

All wires have a finite conductance, representing the ability of the wire to carry a charge flow. Aluminum wires have a resistivity of  $3.3 \text{m}\Omega \cdot \text{cm}$ , while newer thin-film copper wires, used in most contemporary processes, have a resistivity of  $2.2 \text{m}\Omega \cdot \text{cm}$ . Resistance (per unit length) may be approximated by the material resistivity divided by the conductor's cross-sectional area, but several wire non-idealities affect this model.

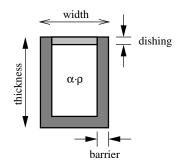

For copper wires, a thin barrier layer on three sides of the wire, required to prevent copper from diffusing into the surrounding oxide (see Figure 2.3) raises resistance by decreasing the wire's effective cross-sectional area. Similarly, due to surface planarization

Figure 2.3: A simple resistance model

and proximity effects to neighboring lines, wide wires may be over-polished, or "dished," again reducing effective cross-sectional area. Finally, electrons inelastically scatter off lattice bonds at the edges of wires. As the wire dimensions grow smaller and smaller, this will reduce the mean free path of electrons, effectively increasing the material resistivity [5]. A modern 0.18- $\mu$ m technology has a copper barrier thickness of 17nm, negligible dishing for normally-sized wires, and negligible carrier scattering [6].

Assuming that the barrier layer is conformal, a reasonable assumption with fabrication techniques such as atomic layer deposition, we can write wire resistance as

$$R_{wire} = \alpha_{scatter} \cdot \frac{\rho}{(thickness - barrier - dishing)(width - 2 \cdot barrier)}$$

(2.1)

We can ignore skin effects for the vast majority of on-chip wires, because wires are under a few skin depths thick and wide. Digital gates rarely swing with transition times faster than an *FO4*, or 90ps in our 0.18- $\mu$ m technology, which corresponds to frequency components of 1.5GHz<sup>1</sup>. At that frequency, copper has a skin depth of 1.7 $\mu$ m, or nearly 20 $\lambda$ , exceeding most wire dimensions. A signal's edge rate, and hence frequency content, scales with technology, but so do wire dimensions. Because skin depth falls with the square root of frequency, wires will shrink faster than their skin depth, making this issue less important under scaling.

<sup>&</sup>lt;sup>1</sup>For a signal switching with a transition time of *t*, the "knee" frequency of that signal's harmonics sits at  $(2\pi t)^{-1}$ . This the frequency at which the spectral amplitude is half that of the standard 20db/decade rolloff. A common misconception is that high-frequency effects become less important if we slow down clock rates. A more accurate statement is that they become less important only with slow edge rates.

At upper layers, metal widths may well exceed two skin depths, especially for those signals carrying power or ground. Designers typically route power and ground wires right next to each other to maximize decoupling capacitance, and by the "proximity effect," currents in the two wires flow as close to each other as possible, making horizontal skin depth important. For those specialized wires, skin effects will prompt designers to break the wide wires up into fingers.

Plugs, or vias, between aluminum metal layers were made of tungsten, and tended to be fairly resistive; in a 0.25- $\mu$ m process a M1-M2 via resistance was about 5 $\Omega$  and vias from M5 down to the substrate added up to more than  $20\Omega$ . This may seem large considering a 1 $\mu$ m wide, 1mm long M5 line itself had a total resistance of only  $20\Omega$ , but by arraying many vias together, designers could easily reduce plug resistance; in most cases, self-heat and electromigration checks required arrayed vias for long wires anyway. Copper processes improve via resistance by depositing vias at the same time as wires. These copper vias are much less resistive and do not need to be as aggressively arrayed, although some recent experience has shown that copper vias have their own electromigration concerns: they serve as nucleation sites, gathering voids that flow down the copper wires much like tumbleweeds [7]. Copper vias thus tend to be arrayed like aluminum vias, only for improved reliability and not reduced resistance.

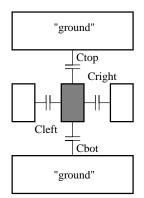

### 2.2.2 Capacitance

All wires have capacitance, modeling the charge that must be added to change the electric potential on the wire. Some analytical models approximate the capacitance of a wire over a plane; more accurate ones combine a bottom-plate term with a fringing term to account for field lines emerging from the edge and top of the wire. However, wires today are taller than they are wide, and will grow even taller to reduce resistance as technologies scale. At minimum pitch their side-to-side capacitances are a significant and growing portion of the total. Capacitance is thus better modeled by four parallel-plate capacitors for the top, bottom, right, and left sides, as shown in Figure 2.4 [8], plus a constant. This extra term lumps all the fringing field terms together and approximates their sum as a constant.

Here, the only non-ideality we need to consider are vertical and horizontal capacitors

Figure 2.4: A simple capacitance model

that have different relative dielectrics. This may be due to air gaps in the intra-layer oxide (faintly visible in the left picture in Figure 2.2), or due to intentional differences in technologies that leverage low- $\kappa$  materials [9]. In this case, we can use

$$C_{wire} = \varepsilon_0 \left( 2M \varepsilon_{horiz} \frac{thickness}{spacing} + 2\varepsilon_{vert} \frac{width}{ILD_{thick}} \right) + fringe(\varepsilon_{horiz}, \varepsilon_{vert})$$

(2.2)

That we can lump the fringe terms into a constant value (though one which changes for different technologies as the dielectric constants  $\varepsilon_{horiz}$  and  $\varepsilon_{vert}$  change) is somewhat surprising. This is really just a result of curve-fitting, and comes about because the fringe terms vary only logarithmically with spacing.

The "far" plates for the top and bottom capacitors are typically modeled as being grounded: they represent a collection of orthogonally-routed conductors that, averaged over the length of the wire, maintain a constant voltage. This capacitance would be multiplied by an appropriate factor if the orthogonal wires switched simultaneously and monotonically, as with a precharge bus. Capacitors to the left and right, on the other hand, have data-dependent effective capacitances that can vary: if the left and right neighbors switch in the opposite direction as the wire, the effective sidewall capacitances double, and if they switch with the wire, the effective sidewall capacitances approach zero. We model this multiplication effect by varying the M parameter in Equation 2.2 between 0 and 2 (our simple model ignores the effects the M term has on the fringe capacitance). These left and right neighbors are also the worst offenders for noise injection. The fringe term depends only

weakly on geometry and for today's  $0.18 \ \mu m$  technologies with homogenous dielectrics is about 40 fF/ $\mu m$ . For the very top layers of metal with no upper layers, we can use three parallel plates with extra fringing terms on the two horizontal capacitors.

#### 2.2.3 Inductance

All wires also have inductance, representing an inertia against changing current through the wire. Unlike resistance or capacitance, inductance has no handy closed-form models. Freshman physics taught us to think about the inductance of a loop, and how a changing magnetic flux through that loop induces a voltage on it. This view of inductance does not easily model on-chip wires, however, because we do not always know what structures form the "loop": if we send current down an on-chip wire, the return currents may flow in adjacent wires, parallel power supply buses, or even the substrate. In fact, due to return currents flowing in the paths of least impedance, the actual current loops will change with the frequency content of the signal. At low frequencies, wide low-resistance power buses, even if far away, have low impedance ( $Z = R + j\omega L$ ), leading to fairly large loops and hence higher inductance. At high frequencies, far-away return paths have unattractively high impedances, and return currents will bypass them to return in local, capacitively-coupled wires, implying lower inductance but higher path resistance.

This "chicken-and-egg" problem is the basic challenge in calculating inductance: we cannot know the inductance until we know what the loop (or loops) are. But we cannot discern the correct loops until we know what the inductance is. To bypass this problem, today's tools define return paths to be at a fixed common reference,<sup>2</sup> and the resultant "partial inductances," when combined with wire resistances and capacitances, can yield accurate results inside circuit simulation [11][12].

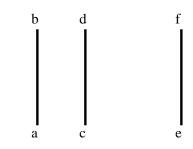

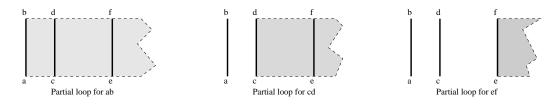

Figure 2.5 shows an example of using partial inductance. Here, wire *ab* carries current from a driver to a load, and this current can return in wires *cd* or *ef* (two power supply lines). There would be many more potential return paths in a realistic layout. Figure 2.6 shows the partial inductances for each of these wire segments. The partial "loops" terminate

<sup>&</sup>lt;sup>2</sup>The common return path can be arbitrarily picked, so long as it is consistent. The most mathematically convenient return path is at infinity; however, this choice leads to physically non-intuitive numbers. As Larry Pillegi noted, "visualizing a loop at infinity is somewhat like drawing God." [10]

Figure 2.5: A signal wire *ab* and two potential returns *cd* and *ef*

at infinity, so their flux areas extend out to the right past the page edge. These partial inductances come only from the geometric information about these wires and not from any assumptions of the current loops. Suppose current upwards in *ab* returns downwards

Figure 2.6: Partial loops for the three wires

in *cd*. Then *cd*'s flux area has the inverse polarity, and when overlaid atop the flux area for *ab*, cancels with *ab*'s flux areas to the right of *cd*. This leaves only the area between *ab* and *cd*, leading to a simple loop inductance calculation and hence an impedance for that loop. The same calculation can be performed for current returning in *ef*, similarly leading to an impedance for that loop. Then in a SPICE simulation, the return current will split, preferring the loop with less overall impedance, and allowing overall loop inductance calculations.

Most inductance calculation tools overestimate inductance because they assume all wire current uniformly flows to the end of the line, while in VLSI circuits, most current actually returns through distributed wire capacitances [13]. A larger problem with inductance calculation involves data explosion: inductance falls slowly with distance inside the return loop, so all wires within several pitches—*i.e.* several wires—must be included in the computation. For each extracted wire we must calculate the mutual inductance to multiple

neighbors, and the amount of data to store and compute quickly becomes unmanageable. Sparsification schemes try to reduce this data without destabilizing the resultant coupling matrices [14][15].

To determine whether or not wire inductance is important we need to consider two questions [16][17][18]:

- Does the driver-end of the wire swing slowly enough to avoid transmission-line effects? Quantitatively, does the driver impedance exceed the line impedance (*R<sub>gate</sub>* > 2 · Z<sub>0</sub>)?

- Do resistive losses in the wire outweigh any transision line effects? Quantitatively, does the wire's attenuation factor  $(0.5 \cdot l \cdot R_{wire})/Z_0$  exceed one?

Short signal wires meet the first condition, making inductance unimportant for them. This is because in a contemporary 0.18- $\mu$ m technology, FastHenry simulations of a well-gridded bus show  $L_{wire} = 0.3$ nH/mm with  $C_{wire} = 0.3$ pF/mm, making  $Z_0$  approximately  $30\Omega$ ,<sup>3</sup> much less than short-line driver resistances. Typical on-chip inductance values range from 0.2 - 0.5nH/mm [19]. In a 0.18- $\mu$ m technology, a drive resistance less than 60 $\Omega$  (twice  $Z_0$ ) must be at least 85 $\mu$ m in width, a driver size appropriate for a 2mm-long wire. Under scaling, both drive resistance and  $Z_0$  remain constant, maintaining this driver-impedance inequality.

The second condition is satisfied by wires that span a typical repeater distance or longer. As will be seen in following chapters, an optimally-repeated wire (assuming RC behavior) has a wire length of

$$l = 3 \cdot \sqrt{\frac{R_{gate}C_{gate}}{R_{wire}C_{wire}}}$$

(2.3)

Thus, the attenuation factor can be written

$$\frac{0.5 \cdot l \cdot R_{wire}}{Z_0} = 1.5 \sqrt{\frac{R_{wire}(R_{gate}C_{gate})}{L_{wire}}}$$

(2.4)

<sup>&</sup>lt;sup>3</sup>We approximate  $Z_0 = \sqrt{\frac{L_{wire}}{C_{wire}}}$ , while more accurately,  $Z_0 = \sqrt{\frac{R_{wire} + j\omega L_{wire}}{j\omega C_{wire}}}$ . With edge rates faster than 100ps, and hence signal frequency content exceeding 1.5GHz (10G-rad/s), this approximation holds quite well.

In our 0.18- $\mu$ m technology, with  $R_{wire} = 30\Omega/\text{mm}$  and  $R_{gate}C_{gate} = 10\text{ps}$ , the optimal repeater distance is about 3mm, and the attenuation term shows that line resistance overwhelms inductance unless the wire is shorter than two-thirds the repeat distance, or 2mm. Under scaling, the attenuation constant for a given wire will increase, making it increasingly resistive.

Hence, in a 0.18- $\mu$ m technology, inductance can be safely ignored for wires shorter than 2mm and for wires longer than 2mm. For wires that are exactly 2mm long, simulations show the delay of an *LRC* wire differs from the delay of an *RC* wire by under 3%, much less than the uncertainty in capacitance or resistance extraction. Wire inductance is therefore unimportant for the delay of typical signal wires.

With much wider wires having much lower resistance, such as power lines, or with systems very sensitive to the exact delay modeling, such as clock networks, inductance does play a role in design. For most signal wires, however, inductance effects on delay are largely irrelevant. Inductive noise, which depends on  $M\delta i/\delta t$ , is not as easily dismissed and will be discussed in more detail below.

### 2.3 Wire performance metrics

The discussion of wire characteristics above provides the groundwork for an examination of wire performance. This section will first consider robustness by exploring signal coupling noise issues, and then discuss delay and bandwidth metrics.

### 2.3.1 Signal coupling

Coupling noise is a serious problem for a chip designer, as both mutual capacitance and inductance terms for wires can be large. To understand the magnitude of coupling noise problems, we need to compare the induced noise to the noise margins of the receiving gate. Static and dynamic CMOS gates are voltage controlled—they switch their output voltage when the input voltage exceeds some threshold. Thus we are concerned about the voltage noise on the wire relative to the voltage margins of the receiving gates.

Capacitance noise coupling is a larger effect so we will look at it first. The large aspect

ratios of modern wires mean that for a wire surrounded by neighboring wires on either side, the cross-capacitance to these sideways neighbors dominates the total capacitance; sideways cap can exceed 70% of the total. When these sideways neighbors (the "attackers") switch, the current that flows through the coupling capacitors must then flow through the center wire (the "victim"), inducing noise on it. The familiar model of  $V_{noise} = V_{swing} \frac{C_{coupling}}{C_{total}}$  gives a pessimistic upper bound on the noise, because this is the noise voltage only if the victim line is left floating. Many recent papers have modeled this noise more carefully, and have shown that the noise voltage depends on both the coupling capacitance to total capacitance ratio as well as on the ratio of the strengths of the gates driving the two wires [21][22][23]. A convenient model simple enough for first-order hand calculations is:

$$V_{noise} = V_{swing} \cdot \frac{C_{coupling}}{C_{total}} \cdot \frac{1}{1 + \frac{\tau_{att}}{\tau_{vic}}}$$

(2.5)

where  $\tau_{att}$  and  $\tau_{vic}$  are the time constants of the attacker and victim drivers, respectively. If the attacker has a much smaller time constant than the victim (and is hence much stronger), the noise approaches the pessimistic worst-case. Typically, however, the transition times of different gates are matched, which gives an attacker-to-victim time constant ratio that is greater than one. If the two wires are identical, with identical drivers, the time constant ratio will be set by the difference between the effective resistance of a MOS transistor in the saturated region, driving the aggressor wire, and a transistor in the linear region, trying to hold the value of the victim wire stable. This ratio is usually between two and four,<sup>4</sup> which greatly reduces capacitive coupled noise for most nodes.

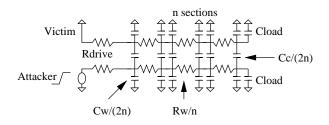

However, the limitation of this model is that it does not account for distributed line resistance. Adding this effect makes deriving analytical results difficult, leading researchers to use approximations like lumping the wire resistance with the driver resistance [22]. However, for the special case where the wires are identical, the most common case where coupling is a problem, there is a way to view the problem using superposition that gives a simple and intuitive view of coupling. This model starts by assuming that the driver resistances are the same, as shown in Figure 2.7.

<sup>&</sup>lt;sup>4</sup>The ratio hinges on the degree of velocity saturation of the attacking transistor. Since nMOS gates suffer more from velocity saturation, the ratio for nMOS gates is generally closer to 4.

#### 2.3. WIRE PERFORMANCE METRICS

Figure 2.7: Bus coupling noise model

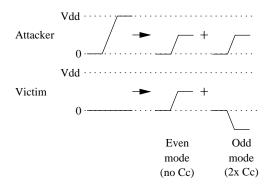

The key to the analysis is to break the driving input into a symmetric, or even mode, input (both sides are driven by a  $\frac{V}{2}$  ramp), and an antisymmetric, or odd mode, input (attacker driven by  $\frac{V}{2}$  ramp and the victim driven by  $-\frac{V}{2}$ ). In the even component, both attacker and victim see a half-amplitude input, and because the two lines now have identical responses, the coupling capacitors conduct no current and can be zeroed out. In this case, the response at the end of the victim is the same as that of a single wire in isolation, with total line capacitance  $C_{total} = nC_s + C_l$ .

For the odd component, the attacker sees a positive half-amplitude step, and the victim sees a negative half-amplitude step. In this case, the two lines have exactly opposite responses, so the coupling capacitors see twice the voltage difference and can be replaced by double-size capacitors referred to ground. Thus we can once again treat the victim wire as an isolated single wire, with total line capacitance  $C_{total} = n(C_s + 2C_c) + C_l$ .

Figure 2.8: Decomposition of attacker and victim waveforms

The combination of the even and odd modes, as in Figure 2.8, will place a full step

on the attacker driver and hold the victim driver to ground, so we need add only the two decoupled responses to get the true victim waveform. In other words, the victim response can be written as the sum of two isolated wire responses, one with no coupling, and the other with double coupling. These two isolated responses can be derived from a number of models, ranging from simple single time-constant exponentials to more complicated moment-matched asymptotic waveforms [24]. The key idea is that symmetry properties allow us to break the highly-coupled circuit into two isolated circuits that are more easily handled.

Note that this model requires that the attacker and victim lines have completely identical resistances and capacitances; in particular, we need them to have the same driver resistances. Yet the driver of the victim wire, a transistor in its linear mode, typically has a lower (stronger) resistance than the saturated transistor driving the attacker wire.

We avoid this limitation by observing that a driving resistor that sees a step input can be transformed into a larger (weaker) resistor by using a slower exponential input. In other words, from the perspective of the downstream wire, a properly-chosen exponential input driven into a resistor is almost indistinguishable from a step input driven into a larger (weaker) resistor. Thus if we use an appropriate exponential input instead of a step input, and the smaller (stronger) victim resistance for both of the wire models, we will effectively increase the attacker driving resistance while maintaining the proper victim resistance.

The mathematical derivation using simple single-time constant models for the wire responses reduces to a peak noise given by:<sup>5</sup>

$$V_{peaknoise} = \frac{C_{coupling}}{C_{total}} \cdot \left(\frac{1+M}{k+M}\right)^{\frac{k+M}{k-1}}$$

(2.6)

$$M = \frac{nR_{wire}}{2R_{att}} \tag{2.7}$$

where k is the ratio of attacker to victim driving resistances (typically between two and four). For reasonable wire lengths, the driver resistance ratio does a good job of attenuating the noise pulse, making it a small issue for static CMOS circuits. However, capacitance coupling is a large problem for weakly-driven nodes, and CAD tools must be used to check

<sup>&</sup>lt;sup>5</sup>Note that this formula reduces to a slightly different result than Equation 2.5 when the wire resistance is 0 (*i.e.* when M = 0). In these cases, this equation gives a better result.

#### 2.3. WIRE PERFORMANCE METRICS

for coupling on such weakly-driven or dynamic nodes.

Noise from inductive coupling can also present problems for VLSI wires. The current flowing down the aggressor wire generates a magnetic field which causes a backwards return current to flow in the victim wire. Inductive coupling pushes the victim in the opposite direction from capacitive coupling: a rising attacker capacitively couples a victim up, but inductively couples the victim down. While capacitive coupling is mostly a "nearest neighbor" phenomenon, inductive coupling has a much larger range. Inductive noise becomes a problem only when a large number of wires switch at the same time in bus-like situations [25][26][27]. The worst-case noise vector would have multiple wires switching, with near neighbors switching in one direction, and far neighbors switching in the opposite direction. This causes the capacitive and inductive noises to add, and the accumulated noise can be enough to cause failures [26].

Designers cope with inductive coupling by adding power planes or densely gridded power supplies to reduce the number of wires that can couple into a victim. Power planes, or dense power grids, effectively reduce both self and mutual inductances for wires in the direction of the grid, because they provide very nice return paths within a few microns of the wire itself and thus limit the extent of the magnetic coupling [28]. Most companies have design rules for buses, such as requiring every fifth wire to be a power supply wire, which makes inductive noise much less than capacitive noise and under 5% of the power supply.

#### 2.3.2 Wire delay

The delay of an on-chip wire can be modeled by a simple RC formulation. Here, we treat a CMOS driver as a simple resistor  $R_{gate}$  with a parasitic load  $C_{diff}$ . The CMOS receiver at the other end of the wire presents a capacitive load  $C_{gate}$ .

$$Delay \propto R_{gate}(C_{diff} + C_{wire} + C_{gate}) + R_{wire}(\frac{1}{2}C_{wire} + C_{gate})$$

(2.8)

By approximating the CMOS driver with a simple resistor, this model ignores both non-linear drive resistance as well as the effect of slew rate on delay.

This model takes advantage of the small effects inductance has on delay: it includes

only R and C terms. Inductance can affect wire delay in four ways, but all are insignificant. First, signal propagation is limited by the speed of light down the wire, set by  $\sqrt{LC}$ . When the driver end of the wire switches, the receiver end cannot begin to transition until at least  $l\sqrt{LC}$ . This effect is insignificant: as discussed previously, wires long enough to make this propagation delay important also have wire resistance that swamps out wire inductance. Second, dramatically under-damped systems will ring, making single-time-constant models poor predictors of delay. But keeping driver fanouts reasonable (*i.e.* not smaller than unity) prevents wires from ringing and keeps the "sharpening" effect of inductance to a small percentage of total line delay. Third, inductive coupling, much like capacitive coupling, can push out delay by forcing a victim to absorb induced transients before swinging. With adherence to some inexpensive design heuristics, however, inductive coupling can be made trivial in comparison to capacitive coupling. Fourth, loop inductance can force return currents into tighter loops with higher resistivity than wider loops. This extra "return path resistance," often overlooked by designers, is typically modeled by simply increasing the  $R_{wire}$  term. This model is imperfect because the return path resistance term actually appears after the load capacitor, so the increase in  $R_{wire}$  is typically done with a correction factor that has been curve-fit to match accurate delay simulations of wiring templates. This scheme, though somewhat inaccurate, has the virtue of easily fitting into standard CAD timing flows.

The first term in Equation 2.8 is about 1*FO4*, as simple sizing heuristics aim for gate sizes to have a fanout of about four for optimal delay [73]. Long wires with large capacitive load might thus imply huge gates, but designers typically use higher fanouts for such long wires; because wire resistance shields downstream capacitance from the drivers, higher fanouts are more efficient. In these long wire cases, the 1*FO4* approximation is somewhat optimistic. We will also assume that our wires are fairly long, so that  $C_{wire} \gg C_{gate}$ . Our metric for delay is therefore simply  $1FO4 + \frac{1}{2}R_{wire}C_{wire}$ . These assumptions do not hold for wires driving large or many gate loads, such as repeated wires (which we will consider later) or control wires driving each bit of a wide datapath. Representative delay numbers for a 0.18- $\mu$ m technology are shown in Table 2.1; this table uses a total capacitance whose cross-capacitance term is Miller-multiplied by a factor of two, to simulate a data-dependent worst-case delay.

#### 2.3. WIRE PERFORMANCE METRICS

|                  | Copper wire delays<br>FO4/mm <sup>2</sup> |

|------------------|-------------------------------------------|

| Local wire       | 0.56                                      |

| Semi-global wire | 0.22                                      |

| Global wire      | 0.05                                      |

Table 2.1: Sample  $\frac{1}{2}R_{wire}C_{wire}$  delays, 0.18- $\mu$ m technology

As Section 2.5 describes in more detail, modern technologies optimize their metal layers for three different tasks. Local wires run on the lowest level of interconnect; the semiglobal wires, on mid-level layers of metal, typically run within functional units; and the global wires, on the top layers of metal, route power, ground, and global signals. The wire delay for all three classes of wires are given in the table. For a copper 0.18- $\mu$ m technology, long unbuffered wires with small loads are not too slow. A 10mm route takes 1+56=57 *FO4*s on local wires, but 1+22=23 *FO4*s on semi-global lines, and 1+5=6 *FO4*s on global wires.

We can also estimate the bandwidth of an unbuffered wire by asking how long we must wait between successive transitions on a wire. If we switch a wire once, we need to wait until residual currents from that transition have mostly died away, or else we will see intersymbol interference when we switch the wire again. We can do this by waiting for three propagation delays before sending the next signal.

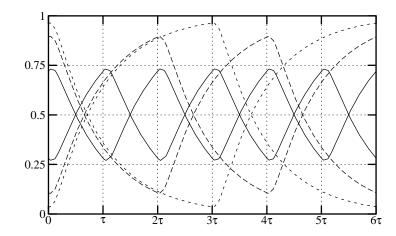

Figure 2.9 shows idealized (linear driver, no noise and no process variations) waveforms from a model of an inverter driving a long wire<sup>6</sup> in a wave-pipelined system. Waiting three time constants ( $\tau$ 's) between tokens allows each waveform step to transition to 95% of the swing; going any faster closes the data "eye" unacceptably. The perfectness of the waveforms underscores the need to wait at least three  $\tau$ 's between tokens—any slight noise or imperfections in the system would close the data eyes further. In reality, real designs, even if wave-pipelined, never achieve these rates: the margining to account for process, voltage, and temperature variabilities would significantly slow the token rate. However, we can still use this three- $\tau$  repeat rate as a safe upper limit for wire bandwidth.

<sup>&</sup>lt;sup>6</sup>This example uses a linear driver resistance of  $36\Omega$ , total gate capacitance of 0.75pF, diffusion capacitance of 0.375pF, wire resistance of  $200\Omega$  and wire capacitance of 0.8pF. The wire is written as a  $\pi$  model.

Figure 2.9: Idealized wave-pipeline with 1-, 2-, and 3-t repeat rates

In the equation below, we assume the propagation delay to be a gate delay (FO4) plus the distributed wire delay. Increasing a wire's pitch will monotonically increase that wire's bandwidth, because it decreases the wire RC product, leading to the misleading result that fatter wires are always better. Therefore, we will actually examine the bandwidth across a routing area. In this case, making wires excessively fat will reduce the number of wires available, and hence potentially reduce bandwidth over that area:

$$BW_{area} = \frac{1}{3(1FO4 + \frac{1}{2}R_{wire}C_{wire})} \cdot \frac{Blockwidth}{Wirepitch}$$

(2.9)

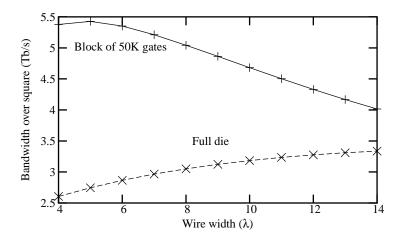

This formulation allows us to examine unrepeated bandwidth in both local and global contexts. For module-length wires, we run semi-global layer metals across a square that holds around 50,000 gates. For global wires, we run top-level metals across a 2cm die and thus consider the bandwidth across a die-sized square.

Figure 2.10 shows module and global unrepeated bandwidth. In Equation 2.9, the lefthand term rises with increasing wire pitch, but the right-hand "number-of-wires" term falls with increasing pitch. Whether or not designers should increase the wire pitch depends on the wire length: if the wire is short enough that its delay is dominated by gate delay, then the bandwidth improvement from increased pitch tends to be less than the bandwidth degradation from fewer wires. If the wire is long enough that its delay dominates gate delay,

Figure 2.10: Unrepeated bandwidth, in an  $0.18 - \mu m$  technology

then bandwidth is improved by increasing pitch. In Figure 2.10, we see that increasing wire width does not improve local bandwidth, but it slightly improves global bandwidth.

The long delay and low bandwidth of the global wires clearly indicates a problem caused by the large resistance of these wires. Fortunately, there is a simple way to dramatically reduce the effect this resistance has on circuit performance—we can break these long wires into a number of shorter segments by adding gain stages between the segments. These stages are called repeaters.

#### 2.3.3 Repeaters

Because the delay of an uninterrupted wire grows quadratically with wire length, designers can add repeating elements periodically along the wire. When added in a way to optimize delay, repeaters make the total wire delay equal to the geometric mean of the total wire delay and the individual repeater stage delay. Hence, the length-squared term in wire delay falls out of the square root, making total delay linear with total wire length:

$$Delay_{rpt} \propto \sqrt{\frac{1}{2}R_{wire}C_{wire} \cdot FO4}$$

(2.10)

Using repeaters is far more attractive for long wires, although they add some design complexity. First, the simplest repeaters are inverting elements, so an even number of repeaters is necessary to maintain logic levels<sup>7</sup>. Second, repeaters for global wires require many via cuts from the upper-layer wires all the way down to the substrate, potentially congesting routes on intervening layers. Third, designers are rarely afforded the luxury of placing repeaters in their optimal locations, because they require active area; designers usually floorplan repeaters in pre-planned clusters. Finally, even with delay-power optimizations, repeaters are still large devices, and repeating an entire bus takes an impressive amount of silicon area. Fortunately for these last two complications, delay and capacitance curves for repeater insertion have fairly shallow optimizations, so that adding or removing a single repeater stage, moving repeaters back and forth, or resizing repeaters have fairly small costs.

Repeated wires offer substantially increased performance. After sending one signal down a wire, we need wait only until that signal fully transitions on the first repeater segment before we send the next signal; the bandwidth of a repeated wire does not depend on the entire wire length. Also, increasing wire pitch makes the repeated segment length longer but does not change the segment delay, so wider wires simply reduce the number of available routing tracks and hence do not improve bandwidth.

In Chapter 4 we will examine repeater sizing, placement, and bandwidth more closely. For now we merely note that repeaters offer an alternative wire design structure that is far more attractive than uninterrupted wires for long wire lengths. For either unrepeated or repeated wires, simple geometric models for wire resistance and capacitance, when coupled with gate delay lead directly to useful wire delay metrics. Next, we consider how these metrics will scale with technology, beginning with gates.

## 2.4 Gate metrics under scaling

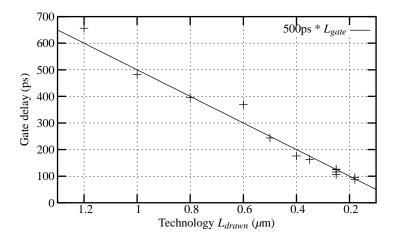

Historically, gates have scaled linearly with technology, and a useful model of FO4 delays has been  $500 \cdot L_{gate}$  ps under worst-case environmental conditions (typical devices, low  $V_{dd}$ , high temperature). In this expression,  $L_{gate}$  is in microns. Figure 2.11 shows FO4 delays for a number of different process technologies running at the worse-case environment corner.

<sup>&</sup>lt;sup>7</sup>Designers may opt to use buffered repeaters, which are two back-to-back inverters. Buffers avoid logical inversion complexity, but, as we will see in the next chapter, are slightly less efficient.

#### 2.4. GATE METRICS UNDER SCALING

This trend may continue for future generations of transistors, as devices seem scalable down to drawn dimensions of 0.018  $\mu$ m [29]. Whether or not such devices will continue to obey the above delay model is uncertain, due to issues in scaling gate oxide,  $V_{dd}$  and  $V_{th}$ . These concerns mean 500· $L_{gate}$  ps is a lower limit for future FO4 delays. Because we are considering wire delays relative to gate delays, faster gates provide the worst case for wire issues, and thus we will use this model as our gate delay projection.

Figure 2.11: FO4 scaling at TTLH (90%  $V_{dd}$ , 125 degrees).

In a commodity 0.18- $\mu$ m technology, our model accurately predicts *FO4* to be about 90ps. In advanced in-house foundries, such as Intel's, *FO4*s are considerably faster: due to notches in the poly gates, the physical gate length  $L_{gate}$  ends up quite a bit smaller than the drawn (and advertised) feature size.<sup>8</sup> For example, Intel's 0.18- $\mu$ m gates have a physical gate length of slightly under 100nm [20], and Intel's 0.13- $\mu$ m gates have a physical gate length of 65nm [4]. Our model still holds as long as we use the correct physical gate length, so an *FO4* in the Intel 0.18- $\mu$ m process is about 50ps. This gap between commodity and advanced transistor technologies appears to be a fairly constant 2x multiplier, allowing us to continue to use our scaling formula.

We assume that other device parameters, such as gate and diffusion capacitance, will also continue to scale. Gate capacitance (per unit width) will remain around 1.5-2 fF/ $\mu$ m;

<sup>&</sup>lt;sup>8</sup>This is not the same as simply saying that "electrical gate length is shorter than drawn gate length," because it is a physical modification of the gate length.

although this would seem to demand too-thin gate oxides, high- $\kappa$  dielectrics may permit this aggressive scaling of the effective  $T_{ox}$  [30]. We project diffusion capacitance to stay at about half the gate capacitance for legged devices, although trench technologies and/or SOI can reduce this [31].

## 2.5 Wire characteristics under scaling

Before we look at how wire characteristics will scale, we will first examine the geometry assumptions in our baseline 0.18- $\mu$ m technology. This process has multiple layers of copper interconnect, with upper layers wider and taller than lower ones. The lowest metal layer, M1, has the finest pitch and hence the highest resistance, and it predominantly connects nets within gates or between relatively close gates. The middle layers, M2 through M4, have a wider pitch than M1 and connect both short- and long-haul routes, typically within functional units. The top layers, M5 and M6, have the widest pitch and hence the lowest resistance and they usually carry global routes, power and ground, and clock. Table 2.2 shows the pitches for these various layers in a contemporary 0.18- $\mu$ m technology. The pitches are described in technology-independent  $\lambda$ 's, where a  $\lambda$  is half of the drawn gate length. We will use similar wire pitches in our scaled technology projections: for our purposes, local wires have a pitch of  $5\lambda$ , semi-global wires a pitch of  $8\lambda$ , and global wires a pitch of  $16\lambda$ .

| Metal | Pitch, µm | Pitch, $\lambda$ |

|-------|-----------|------------------|

| M6    | 1.76      | 20               |

| M5    | 1.6       | 18               |

| M4    | 1.08      | 12               |

| M3    | 0.64      | 7                |

| M2    | 0.64      | 7                |

| M1    | 0.5       | 5.5              |

Table 2.2: Wire pitch dimensions for an Intel 0.18- $\mu$ m technology [36]

Predicting the future of wire technologies is tricky; whatever we say will almost certainly turn out to be wrong. Hence, we take a two-sided approach in this section. First, we consider wire performance given very optimistic, or aggressive, projections of technology scaling. This would include minor or insignificant resistance degradation from dishing or scattering, aggressive low- $\kappa$  dielectrics, and tall wire aspect ratios. Second, we also consider wire performance given very pessimistic, or conservative, projections. This would include significant scattering and dishing effects, very limited low- $\kappa$  dielectrics, and small wire aspect ratios. Pushing either projection to extremes allows us to confidently state that future technologies will fall inside the resulting broad range. This approach will be useful if both extremes still tell us a consistent story, and we shall see that they do.

|            |                           | Technology, in $\mu$ m |       |       |        |        |        |        |        |        |  |

|------------|---------------------------|------------------------|-------|-------|--------|--------|--------|--------|--------|--------|--|

|            |                           | 0.18                   | 0.13  | 0.1   | 0.07   | 0.05   | 0.035  | 0.025  | 0.018  | 0.013  |  |

| Common     | Material                  | Cu                     | Cu    | Cu    | BulkCu | BulkCu | BulkCu | BulkCu | BulkCu | BulkCu |  |

| Wire       | ρ, mΩ · µm                | 0.022                  | 0.022 | 0.022 | 0.018  | 0.018  | 0.018  | 0.018  | 0.018  | 0.018  |  |

| Properties | $\varepsilon_r$ for $C_c$ | 3.750                  | 3.188 | 2.709 | 2.303  | 1.958  | 1.664  | 1.414  | 1.202  | 1.022  |  |

|            | Pitch, µm                 | 0.720                  | 0.520 | 0.400 | 0.280  | 0.200  | 0.140  | 0.100  | 0.072  | 0.052  |  |

|            | Aspect ratio              | 2.0                    | 2.2   | 2.4   | 2.7    | 3.0    | 3.0    | 3.0    | 3.0    | 3.0    |  |

| Semi-      | Thickness, µm             | 0.720                  | 0.572 | 0.480 | 0.379  | 0.300  | 0.210  | 0.150  | 0.108  | 0.078  |  |

| Global     | ILD, µm                   | 0.750                  | 0.540 | 0.480 | 0.405  | 0.315  | 0.210  | 0.150  | 0.108  | 0.078  |  |

| Wires      | Barrier, µm               | 0.017                  | 0.013 | 0.010 | 0      | 0      | 0      | 0      | 0      | 0      |  |

|            | Dishing                   | 0                      | 0     | 0     | 0      | 0      | 0      | 0      | 0      | 0      |  |

|            | $\alpha_{scatter}$        | 1                      | 1     | 1     | 1      | 1      | 1      | 1      | 1      | 1      |  |

|            | Pitch, $\mu m$            | 1.440                  | 1.040 | 0.800 | 0.560  | 0.400  | 0.280  | 0.200  | 0.144  | 0.104  |  |

|            | Aspect ratio              | 2.2                    | 2.5   | 2.7   | 2.8    | 3.0    | 3.0    | 3.0    | 3.0    | 3.0    |  |

|            | Thickness, µm             | 1.584                  | 1.300 | 1.080 | 0.784  | 0.600  | 0.420  | 0.300  | 0.216  | 0.156  |  |

| Global     | ILD, µm                   | 1.5                    | 1.08  | 0.96  | 0.81   | 0.63   | 0.420  | 0.300  | 0.216  | 0.156  |  |

| Wires      | Barrier, µm               | 0.017                  | 0.013 | 0.010 | 0      | 0      | 0      | 0      | 0      | 0      |  |

|            | Dishing                   | 0                      | 0     | 0     | 0      | 0      | 0      | 0      | 0      | 0      |  |

|            | $\alpha_{scatter}$        | 1                      | 1     | 1     | 1      | 1      | 1      | 1      | 1      | 1      |  |

Table 2.3: Aggressive wire predictions, technology terms only

Tables 2.3 and 2.4 summarize the technological parameters used in the conservative and aggressive technology scaling projections. These assume room temperature sheet resistances. Happily, recent SIA roadmap trends do fall within these bounds [37]. In both sets of scaling projections, we keep the semi-global pitch to be  $8\lambda$  and the global pitch to be  $16\lambda$ . One design possibility not pursued here is the use of "superwires": for performance and power delivery reasons, designers may choose to give the very top layers of metal a thickness and pitch that stays constant in microns. These global wires thus scale upwards in size relative to the rest of the metal layers, and will have superior current-carrying and delay characteristics, enabling global delays to scale with gate delays. These superwires

|            |                           | Technology, in $\mu m$ |       |       |       |       |       |       |       |       |

|------------|---------------------------|------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

|            |                           | 0.18                   | 0.13  | 0.1   | 0.07  | 0.05  | 0.035 | 0.025 | 0.018 | 0.013 |

| Common     | Material                  | Cu                     | Cu    | Cu    | Cu    | Cu    | Cu    | Cu    | Cu    | Cu    |

| Wire       | ρ, mΩ · <i>μ</i> m        | 0.022                  | 0.022 | 0.022 | 0.022 | 0.022 | 0.022 | 0.022 | 0.022 | 0.022 |

| Properties | $\varepsilon_r$ for $C_c$ | 3.750                  | 3.375 | 3.038 | 2.734 | 2.460 | 2.214 | 2.104 | 1.998 | 1.899 |

|            | Pitch, µm                 | 0.720                  | 0.520 | 0.400 | 0.280 | 0.200 | 0.140 | 0.100 | 0.072 | 0.052 |

|            | Aspect ratio              | 2.0                    | 2.0   | 2.0   | 2.0   | 2.0   | 2.0   | 2.0   | 2.0   | 2.0   |

| Semi-      | Thickness, µm             | 0.720                  | 0.520 | 0.400 | 0.280 | 0.200 | 0.140 | 0.100 | 0.072 | 0.052 |

| Global     | ILD, µm                   | 0.750                  | 0.540 | 0.480 | 0.405 | 0.315 | 0.210 | 0.150 | 0.108 | 0.078 |

| Wires      | Barrier, µm               | 0.017                  | 0.012 | 0.008 | 0.006 | 0.004 | 0.003 | 0.003 | 0.002 | 0.002 |

|            | Dishing                   | 0                      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|            | $\alpha_{scatter}$        | 1                      | 1     | 1     | 1     | 1     | 1     | 1.05  | 1.05  | 1.05  |

|            | Pitch,µm                  | 1.440                  | 1.040 | 0.800 | 0.560 | 0.400 | 0.280 | 0.200 | 0.144 | 0.104 |

|            | Aspect ratio              | 2.2                    | 2.2   | 2.2   | 2.2   | 2.2   | 2.2   | 2.2   | 2.2   | 2.2   |

|            | Thickness, µm             | 1.584                  | 1.144 | 0.880 | 0.616 | 0.440 | 0.308 | 0.220 | 0.158 | 0.114 |

| Global     | ILD, µm                   | 1.980                  | 1.430 | 1.100 | 0.770 | 0.550 | 0.385 | 0.275 | 0.198 | 0.143 |

| Wires      | Barrier, µm               | 0.017                  | 0.012 | 0.008 | 0.006 | 0.004 | 0.003 | 0.003 | 0.002 | 0.002 |

|            | Dishing                   | 10%                    | 10%   | 10%   | 10%   | 10%   | 10%   | 10%   | 10%   | 10%   |

|            | $\alpha_{scatter}$        | 1                      | 1     | 1     | 1     | 1     | 1     | 1.05  | 1.05  | 1.05  |

Table 2.4: Conservative wire predictions, technology terms only

were first envisioned by Song and Glasser [38] for electromigration and voltage drop considerations. Because their consumption of wire resources (per gate) grows worse under scaling, our discussion does not include their usage.

## 2.5.1 Resistance under scaling

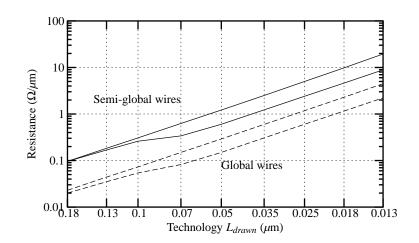

Under ideal scaling in all dimensions, wire resistance grows rapidly, as wire cross-sections fall by 2x each generation (only approximately, because of cladding and dishing correction terms). To prevent this resistance penalty, designers have been scaling wires in only the lateral dimension and increasing wire aspect ratios. Doing this makes the scaling penalty for resistance ( $\Omega$  per unit length) a single scale factor. Not considered here is the possibility of active cooling: refrigeration can lower copper resistance by almost an order of magnitude as temperatures drop from  $300^{\circ}K$  to  $77^{\circ}K$ , although today such cooling is prohibitively expensive. Resistance scaling is shown in Table 2.5 and in Figure 2.12.

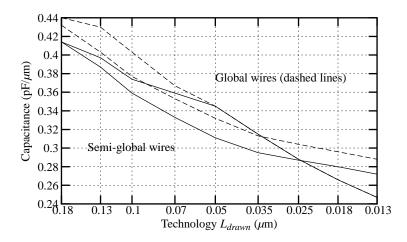

### 2.5.2 Capacitance and inductance under scaling

Under ideal scaling, per-unit-length capacitance would fall due to incremental improvements in dielectric constants; it depends principally on the ratio of dimensions, so as long

|                         |       | Technology, in $\mu$ m |       |       |       |       |       |       |        |  |

|-------------------------|-------|------------------------|-------|-------|-------|-------|-------|-------|--------|--|

|                         | 0.18  | 0.13                   | 0.1   | 0.07  | 0.05  | 0.035 | 0.025 | 0.018 | 0.013  |  |

| Aggr. semi-global wires | 0.096 | 0.168                  | 0.260 | 0.340 | 0.600 | 1.224 | 2.400 | 4.630 | 8.876  |  |

| Aggr. global wires      | 0.020 | 0.035                  | 0.054 | 0.082 | 0.150 | 0.306 | 0.600 | 1.157 | 2.219  |  |